纳米级MOSFET亚阈值区电流特性模型*

王丹丹,王 军,王 林

(西南科技大学 信息工程学院,四川 绵阳 621010)

纳米级MOSFET亚阈值区电流特性模型*

王丹丹,王 军,王 林

(西南科技大学 信息工程学院,四川 绵阳 621010)

基于纳米级金属氧化物半导体场效应晶体管(MOSFET)器件结构,从基本的漂移扩散方程出发,分别建立了亚阈值区漏极电流模型和栅极电流模型。其中将频率与偏置依赖性的影响显式地体现在模型中。通过对比分析发现亚阈值区漏极电流模型具有等比例缩小的可行性,栅极电流具有跟随性和频率依赖性。同时将所建模型的仿真结果与实验结果进行了比较,验证了模型准确性。

纳米级金属氧化物场效应晶体管;亚阈值区;漏极电流;栅极电流;频率依赖性

0 引言

集成电路对高集成度、低功耗和工作频率的需求不断提高,使得CMOS技术不断发展。但对于产品设计来说,漏极电流和栅极电流作为MOS器件的重要直流参数,是器件建模和仿真的难点和核心,同时能够准确预测MOSFET高频电流特性的物理数学模型也是至关重要的[1]。

目前对围绕纳米级MOSFET的性能提升、物理模型的研究已成为国内外研究的热点,其中电流特性模型是MOSFET器件和电路进行直流分析、交流小信号分析、噪声分析等的重要基础[2]。然而文献报道中的器件特性模型,主要聚焦于MOSFET强反区直流漏极电流、电导、本征电荷和本征电容的研究上[3],对于亚阈值区漏电流和栅极电流的研究却鲜有报道。文献[4]提出了传统的长沟道漏电流模型,揭示了强反区漏电流平方律特性,却缺乏亚阈值区的研究。文献[5-7]阐述了传统长沟道MOSFET栅极电流模型推导,但随着器件进入纳米级,工作频率升至吉赫兹以上,已不能准确描述出现的所有新特性,且描述出的电学特性之间总有不自洽存在。

基于器件亚阈值区,本文建立了纳米级MOSFET漏电流模型和栅极电流模型,同时加强了器件电流的频率与偏置依赖性建模来反映器件电流特性。对于亚阈值区电流模型,基于亚阈值区反型电荷,而不是采用传统的有效沟道厚度近似的概念,从而提高了模型的精确度。同时将所建模型的仿真结果与实验测量结果进行了比较,验证了模型的准确性。该模型的建立为纳米级MOSFET的分析和设计提供了参考,推导出的I/V特性方程更容易将抽象级别从器件物理级别提升到电路级。

1 电流模型

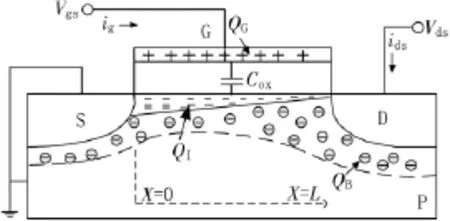

图1是纳米级NMOSFET结构示意图,其中采用了电荷模型。漏极电流和栅极电流特性模型是纳米级NMOSFET器件和电路进行直流分析、交流小信号分析、噪声分析等的重要基础,因此对分析研究纳米级NMOSFET器件的电流特性很有必要。

1.1 漏极电流

基于器件中载流子的随机运动,运用扩散漂移理论,纳米级MOSFET器件中漏极电流可表示为:

图1 纳米级NMOSFET结构示意图

式中,Ids1为漂移电流,Ids2为扩散电流,其表达式分别为:

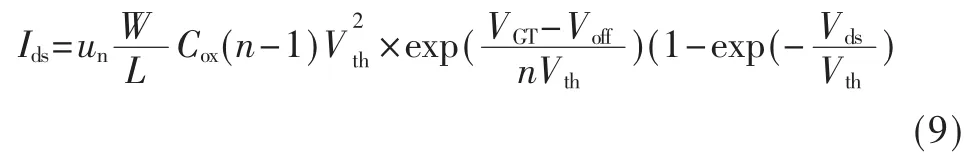

其中 αn为碰撞电离率,QI(x)为器件单位面积反型层电荷数,V(x)为加在 x点上的电压,Vth为热电压,W 为沟道宽度,un为载流子迁移率,Dn为扩散系数,Dn=unkT/q。当器件工作强反区时(栅压大于阈值电压,Vgs>VT),相对于器件沟道中漂移电流来说,此时可以忽略扩散电流,总电流中漂移电流为主导,即 Ids=Ids1。然而随着 Vgs的不断减小,漏电流也不断降低,当 Vgs接近 VT或者小于 VT时,纳米级MOSFET器件的I/V特性从平方律变为指数律,而此时的电流称之为亚阈值电流。当器件工作在亚阈值区,势垒表面的可动载流子迁移率较低,沟道电流以扩散电流为主[8],即:

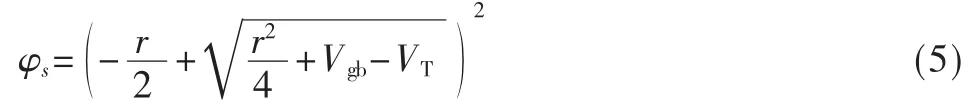

当器件工作在亚阈值区,反型层电荷浓度和耗尽层电荷浓度相比可以忽略不计,从源端到漏端的表面势可视为常数[9-10],通过求解泊松方程可得到表面势表达式为:

其中:

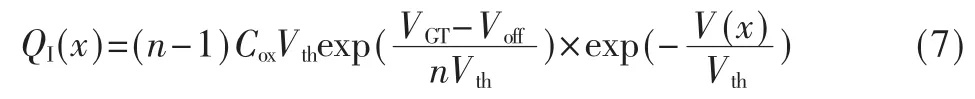

式中,εsi为硅的介电常数,Nsub为衬底的掺杂浓度,Cox是栅氧电容。由表面势可进一步求得沟道反型层单位面积电荷数为:

其中:

式中,VGT=Vgs-VT为栅极过载,Voff为补偿电压。

由上式可以推导纳米级 MOSFET亚阈值区漏电流为:

1.2 栅极电流

感应栅极电流是由沟道内的波动电势通过栅极电容的耦合效应,引起了栅极极板的噪声电流。如图1所示,栅极感应噪声电流可以表示为[11]:

其中 ω为角频率,φS(x)为沿着沟道方向 x处电势。根据电荷守恒可得:

式中QB为耗尽层电荷密度,由电荷与电容的基本关系Q=CU,上式可进一步表示为:

其中CD为耗尽区电容。通过把式(4)、式(12)代入式(10),可推导得感应栅极噪声电流为:

因此,纳米级MOSFET亚阈值区栅极电流表达式为:

2 结果及分析

为验证本文所建立的纳米级MOSFET亚阈值区漏电流模型和栅感应电流模型的准确性,首先将拟合参数代入模型后,利用MATLAB进行仿真,然后将仿真结果与实验测量结果相比较来验证模型的准确性,同时分析不同偏置条件下的器件电流特性。

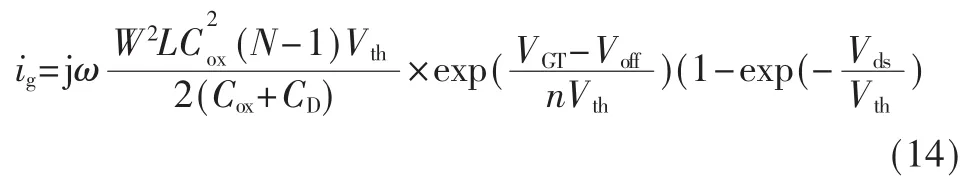

图2所示为亚阈值区纳米级MOSFET的输出特性曲线。从图中可以看出,曲线1、曲线2和曲线3分别是栅极偏置为 Vgs=0.15 V,Vgs=0.2 V和 Vgs=0.25 V时的输出特性曲线。当Vds很小时,漏电流 Ids将随着Vds上升而迅速增大,输出特性曲线的斜率较大。在一定栅极偏置条件下随着Vds不断增加,漏电流开始饱和,是由于亚阈值区沟道反型层存在载流子浓度梯度,靠近源端高,靠近漏端低,电流以扩散电流为主。

图2 40nm MOSFET输出特性曲线

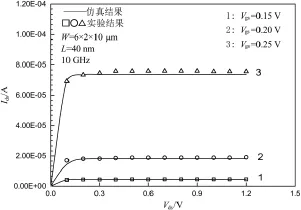

图3为亚阈值区MOSFET转移特性曲线,图3(a)为线性坐标,图3(b)为半对数坐标。从图中130 nm和40 nm MOSFET漏电流对比分析可以看出,在亚阈值区,漏电流很小且随着 Vgs的减小,其值以指数形式急剧下降,是由于在亚阈值区漏电流以扩散电流为主导,由源漏两端的电荷浓度差决定,而亚阈值区源端电荷浓度和Vgs呈指数关系,因此漏电流和 Vgs呈现指数关系,具有很强的偏置依赖性。仿真结果与实验结果的良好吻合,证明了该模型的准确性,同时也说明本文漏电流模型等比例缩小的可行性。

图3 亚阈值区MOSFET转移特性曲线

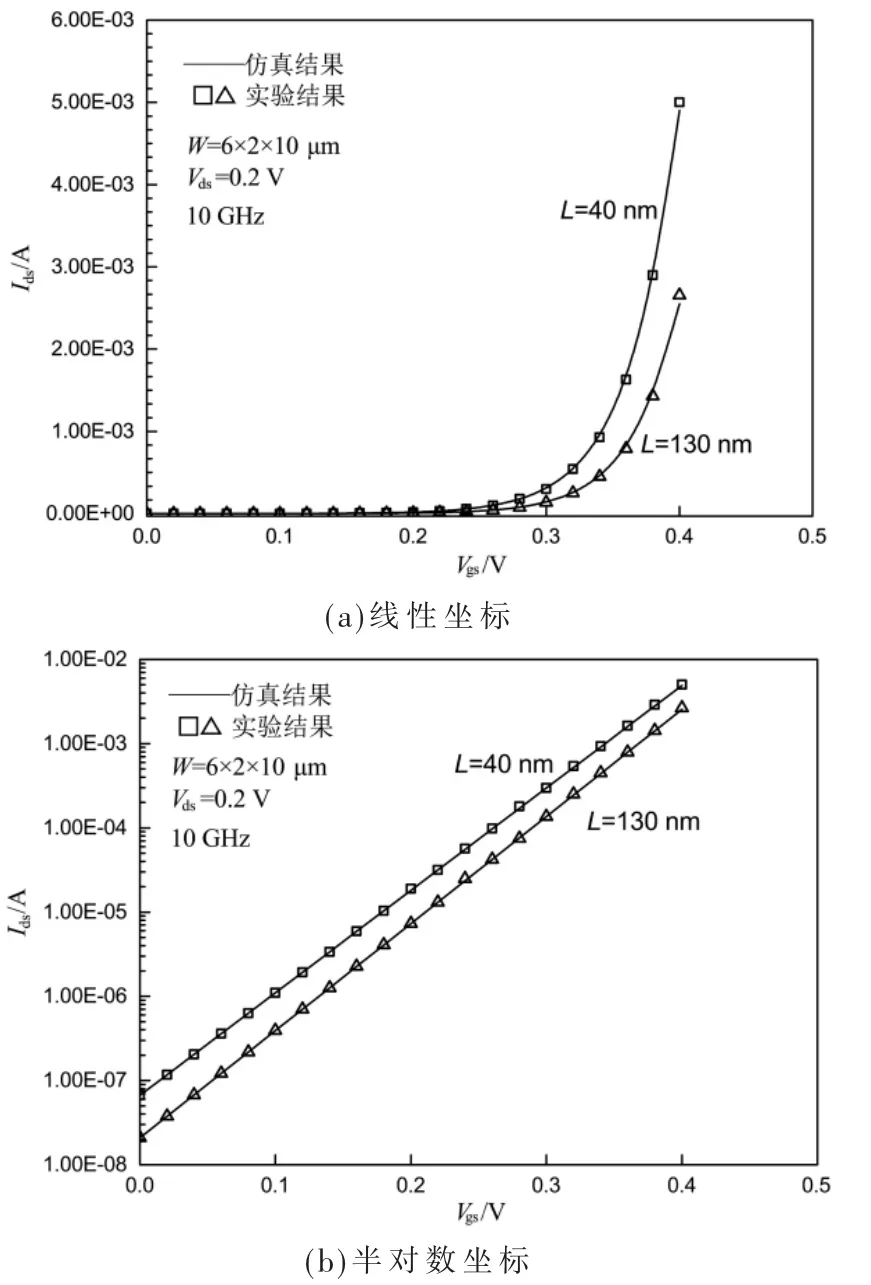

图4为亚阈值区MOSFET栅感应电流随栅极偏压的变化曲线,图4(a)为线性坐标,图4(b)为半对数坐标。通过图中130 nm和40 nm MOSFET漏电流对比分析可以看出,沟道越短,亚阈值区漏电流越大,Ig随着 Vgs的增大以指数形式增加。这是由于随着沟道长度的减小,使得源漏极耗尽区在沟道中的比重增大,反型层所占比重减小,本征载流子浓度提高,沟道反型层电子密度提高;同时 Vgs增大,导致氧化层电场增强,致使沟道表面电子的耦合效应以及碰撞频率均增大。分析发现,栅感应电流与漏电流相比,Ig具有跟随性。

图4 亚阈值区MOSFET栅感应电流Ig随栅极偏压变化的关系

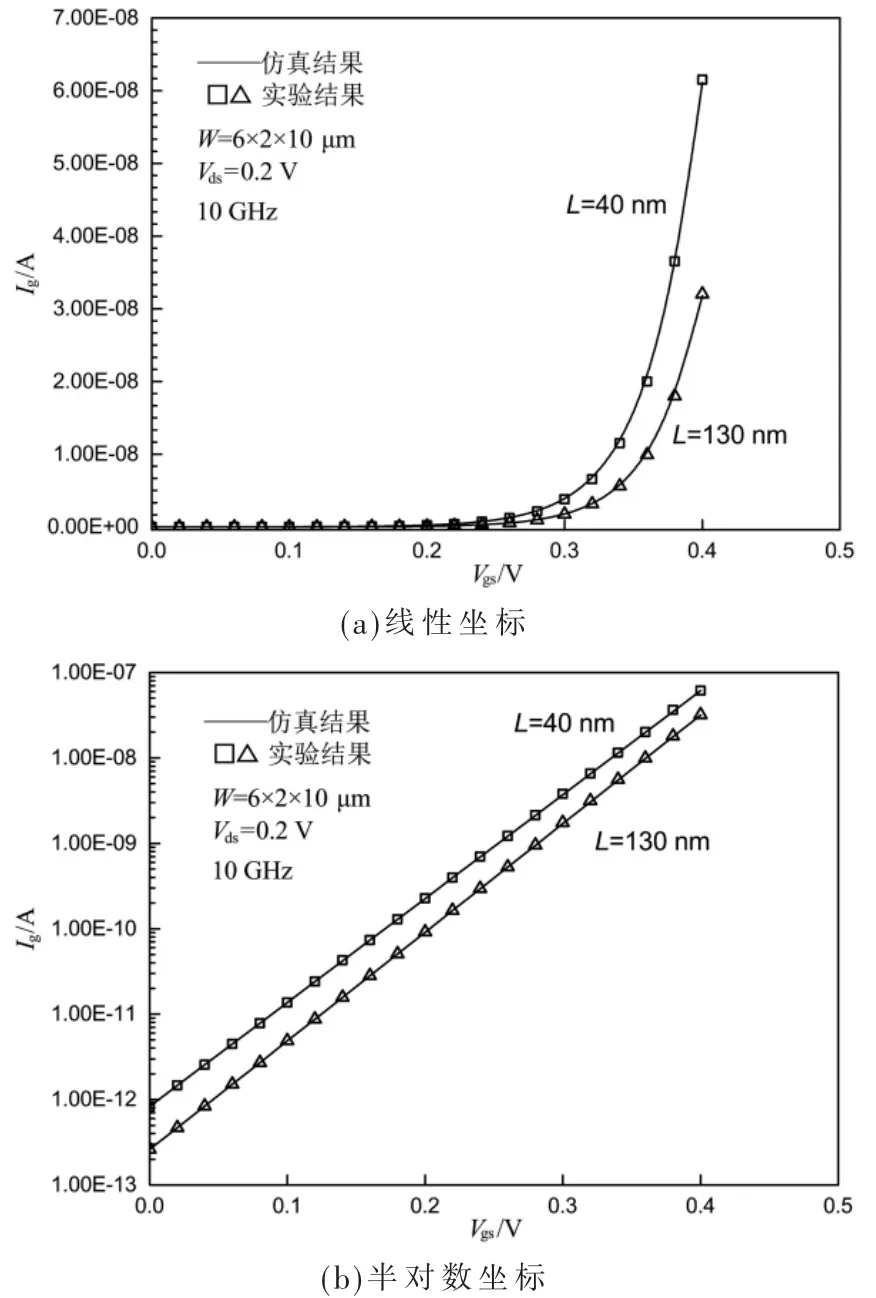

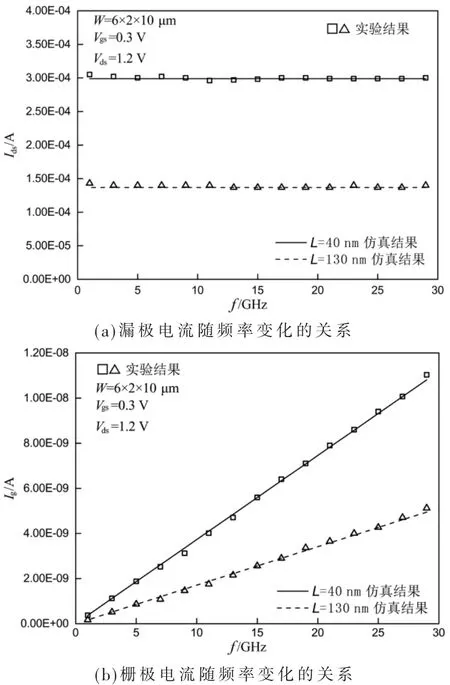

图5为亚阈值区电流随频率变化的关系,图5(a)为漏电流随频率变化的关系,图5(b)为栅感应电流随频率变化的关系。从图中可以看出,一定偏置条件下漏电流具有频率独立性,而栅感应电流具有强烈的频率依赖性,与频率成线性比例。在亚阈值区,当频率升高时,沟道纵方向上载流子的热运动加剧,耦合效应和碰撞频率就越明显,感应栅极电流噪声也就越高,而横向方向上,主要由沟道电子面密度所决定。

图5 亚阈值区电流的频率依赖性

3 结论

本文针对纳米级MOSFET器件物理结构,运用漂移扩散原理分别建立了亚阈值区漏极电流模型和栅极电流模型。其中模型引入了频率与偏置依赖性来反映器件电流特性,同时将所建模型的仿真结果与实验测量结果相比较,验证了模型准确性。并且对于亚阈值区电流模型,基于亚阈值区反型电荷,而不是采用传统的有效沟道厚度近似的概念,从而提高了模型的精度。通过不同偏置条件下的对比分析表明亚阈值区漏极电流模型具有等比例缩小的可行性,栅极电流具有跟随性和频率依赖性。

[1]CHAUHAN Y S,VENUGOPALAN S,CHALKIADAKI M A,et al.BSIM6:Analog and RF compact model for bulk MOSFET[J].IEEE Transactions on Electron Devices,2014,61(2):234-244.

[2]PARVIZI M,ALLIDINA K,EL-GAMAL M N.A sub-mW, ultra-low-voltage,wideband low-noise amplifier design technique[J].IEEE Transactions on Very Large Scale Integration Systems,2015,23(6):1111-1122.

[3]CHALKIADAKIM A,ENZ C C.RF small-signal and noise modeling including parameter extraction of nanoscale MOSFET from weak to strong inversion[J].IEEE Transactions on Microwave Theory&Techniques,2015,63(7):1-12.

[4]拉扎维.模拟 CMOS集成电路设计[M].西安:西安交通大学出版社,2003.

[5]ARORA N.Modeling hot-carrier effects[M].MOSFET Models for VLSI Circuit Simulation.Springer Vienna,1993:366-401.

[6]TRIANTIS D P,BIRBAS A N,PLEVRIDIS S E.Induced gate noise in MOSFETs revisited:The submicron case[J].Solid-State Electronics,2010,41(12):1937-1942.

[7]CHAN L H K,YEO K S,CHEW K W J,et al.Highfrequency noise modeling of MOSFETs for ultra low-voltageRF applications[J].IEEE Transactions on Microwave Theory &Techniques,2015,63(1):141-154.

[8]ARORA N.Mosfet modeling for vlsi simulation:theory and practice(International series on advances in solid state electronics)[M].World Scientific Publishing Co.Inc.2007.

[9]TSIVIDIS Y.Operation and modeling of the MOS transistor[M].McGraw-Hill,Inc.1999:25-39.

[10]吕懿,张鹤鸣,胡辉勇,等.单轴应变 Si n型金属氧化物半导体场效应晶体管源漏电流特性模型[J].物理学报,2015(19):272-277.

[11]VAN L R,PAASSCHENS J C J,SCHOLTEN A J,et al.New compact model for induced gate current noise[C].Electron Devices Meeting,2003.IEDM′03 Technical Digest.IEEE International.IEEE,2003:36.2.1-36.2.4.

表1 国外先进单片集成接收机的性能指标

参考文献

[1]MAHON S J,CONVERT E,BEASLY P T,et al.Broadband integrated millimeter-wave up-and down-converter GaAs MMICs[J].IEEE Transactions on Microwave Theory& Techniques,2006,54(5):2050-2060.

[2]VAUDESCAL O,LEFEBVRE B,COUTURIER A M,et al.A highly integrated MMIC chipset for 28 GHz LMDS Applications[C].Microwave Conference,2000.European.IEEE,2000:1-3.

[3]SINGH P K,BASU S,LIAO K H,et al.Highly integrated Ka-band sub-harmonic image-reject down-converter MMIC[J].Microwave&Wireless Components Letters IEEE,2009,19(5):305-307.

[4]RAO N,PARFITT A,DADELLO A,et al.A low noise Kaband down converter for space applications[C].Microwave Conference,2000.30th European.IEEE,2000:1-4.

[5]苗俊刚,郑成,胡岸勇,等.被动毫米波实时成像技术[J].微波学报,2013,29(Z1):100-112.

[6]陈立福,万国龙.被动毫米波辐射成像系统中的通道误差研究[J].电子测量技术,2008,31(12):45-48.

[7]GUNNARSSON S E,EMRICH A,ZIRATH H,et al.A single-chip 53 GHz radiometer front-end MMIC for geostationary atmospheric measurements[C].Radio and Wireless Symposium.2008:867-870.

[8]LIU T,HAN K,YE Y,et al.A V-band radiometer MMIC for geostationary atmospheric[C].Wireless Symposium.IEEE,2015.

[9]JOHANSEN T K,KROZER V.An InP HBT sub-harmonic mixer for E-band wireless communication[C].Microwave Integrated Circuits Conference(EuMIC),2010 European.IEEE,2010:198-201.

(收稿日期:2016-07-14)

作者简介:

文潇凡(1992-),男,硕士研究生,主要研究方向:射频集成电路设计。

夏同生(1976-),通信作者,男,博士,副教授,主要研究方向:射频集成电路、微纳米尺度下的量子输运等,E-mail:xiatongsheng@buaa.edu.cn。

苗俊刚(1963-),男,博士,教授,主要研究方向:微波遥感理论与技术、微波毫米波成像技术等。

A model of subthreshold current characteristics for the nanoscale MOSFET

Wang Dandan,Wang Jun,Wang Lin

(College of Information Engineering,Southwest University of Science and Technology,Mianyang 621010,China)

Based on nano-metal-oxide-semiconductor field-effect transistor(MOSFET)device structure,starting from the basic driftdiffusion equation,the subthreshold drain current model and gate current model were established.Especially,the frequency and bias dependence is explicitly included in the current models.Through comparative analysis showed subthreshold drain current model with the feasibility of scaling and gate current has followed and frequency-dependent.Meanwhile the simulation results of the model are compared with the extracted experiment results to verify the accuracy of the model.

nano-metal-oxide-semiconductor field-effect transistor;subthreshold;drain current;gate current;frequency dependence

TN386.1

A

10.16157/j.issn.0258-7998.2016.12.004

王丹丹,王军,王林.纳米级MOSFET亚阈值区电流特性模型[J].电子技术应用,2016,42(12):19-22,26.

英文引用格式:Wang Dandan,Wang Jun,Wang Lin.A model of subthreshold current characteristics for the nanoscale MOSFET[J].Application of Electronic Technique,2016,42(12):19-22,26.

2016-07-10)

王丹丹(1989-),男,硕士研究生,主要研究方向:射频集成电路设计、纳米MOSFET建模。

王军(1970-),通信作者,男,教授,主要研究方向:射频电路设计、微弱随机信号处理,E-mail:1429772696@qq.com。

王林(1990-),男,硕士研究生,主要研究方向:射频电路设计、纳米MOSFET建模。

国家自然科学基金(69901003)