HDMI接收端的数据同步模块设计

李 新,梁春明

(沈阳工业大学,辽宁 沈阳 110870)

HDMI接收端的数据同步模块设计

李 新,梁春明

(沈阳工业大学,辽宁 沈阳 110870)

在分析HDMI协议以及数据并串、串并转换过程中数据流的连续性的基础上,针对HDMI接收端,提出了一种能同时完成数据边界定位和不同通路数据对齐的数据同步模块的设计方案。利用可综合的Verilog语言完成电路的设计,通过NC-Verilog仿真验证,并集成到HDMI的系统中。该数据同步模块同时实现数据定位和数据对齐,可有效地提高HDMI接收端的数据处理能力。

HDMI;数据连续性;数据同步

在大数据量、高速传输的技术需求下,高清数字媒体接口技术成为当下消费电子行业研发的重点,各种各样的数字传输接口也开始逐渐出现在人们的日常生活中,HDMI接口成为现代数字接口传输高清视频的主要代表之一[1]。HDMI高清多媒体接口是由日立、松下、飞利浦、Silicon Image、索尼、汤姆逊、东芝7家公司共同推出的数字显示接口标准。2002年12月9日,HDMI Founders推出HDMI 1.0版接口标准,当前最新版本为2013年9月发布的HDMI 2.0版接口标准[2]。

本文基于HDMI 1.4b版本,根据HDMI不同周期下数据编码的特点,以及串行输出数据的要求,研究了数据串并转换时数据流的连续性,采用可综合的Verilog语言完成HDMI接收端的数据同步模块设计,并集成到HDMI系统中。

1 HDMI接口简介

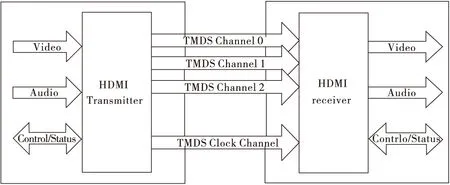

HDMI系统由HDMI发射端和HDMI接收端两部分组成,两者之间主要由4条TMDS通路连接,1条TMDS时钟通路和3条TMDS数据通路,如图1所示。3条数据通路主要用来传输编码之后的视频数据、音频数据以及辅助信息和控制信息[3]。

图1 TMDS系统结构图

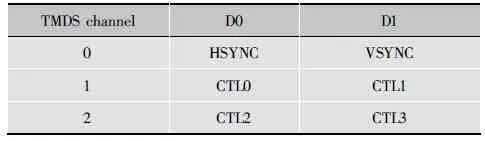

HDMI有3种不同的传输周期,分别是视频周期、数据岛周期和控制周期,每种传输周期的数据都有其独特的编码方式。视频周期数据采用TMDS编码方式,将8 bit的数据编码成10 bit的数据;数据岛周期传输音频数据和辅助信息,采用TERC4编码方式将4 bit数据编码成10 bit数据[4];控制周期传输控制信号,用来指示下一周期是视频周期还是音频周期。3个通路的控制信号如表1所示,每个通路的2 bit数据的编码方式如表2所示。

表1 控制信号

表2 控制信号编码方式

在一个TMDS时钟周期内,3个TMDS数据通路会各自串行输出10 bit数据。在数据的传输过程中,最低位将被最先传输,最高位将被最后输出[5]。

2 并串、串并转换数据的连续性分析

HDMI发送端把编码之后的数据以串行的形式输出,在经过串并转换作为接收端的输入。以HDMI编码之后的10 bit数据为例来分析并串、串并转换后对数据连续性的影响。

数据的串行输出不外乎两种情况,高位先出和低位先出。在理想的情况下,高位先出和低位先出的串行数据经过串并转换之后得到的数据是相同的,都是串行转换之前的HDMI编码数据。在实际的HDMI系统中,由于时序原因,从数据输入HDMI发送端到串行输出需要一定数量的时钟周期。在编码数据到来之前,并串转换模块已经开始工作,产生一系列的“无效数据”,这些“无效数据”在串并转换时就会对数据的连续性有一定的影响。

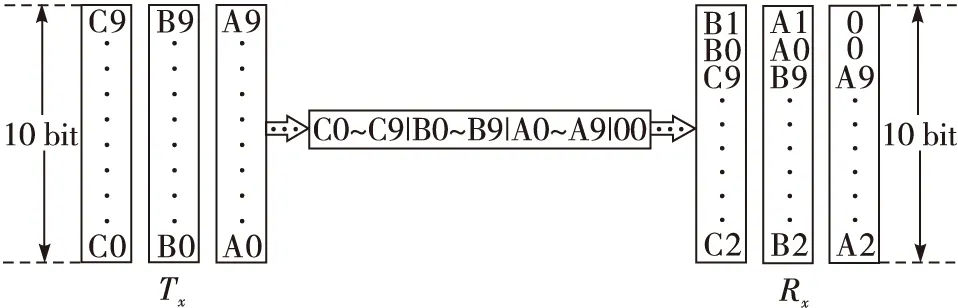

高位先出的情况:由于在串行的编码数据之前会有不确定数量的“无效数据”,这里用“0”表示,假定有2个“0”,那么在串并转换的时候这2个“0”也会参与其中,并占据并行数据的高位,如图2所示。这就会导致还原回来的每组10 bit数据不再是串行之前的HDMI编码数据。但从总体上看,在数据边界定位时,并没有破坏数据的连续性,相对于理想情况,变化的只有数据的相对位置。

图2 高位先出示意图

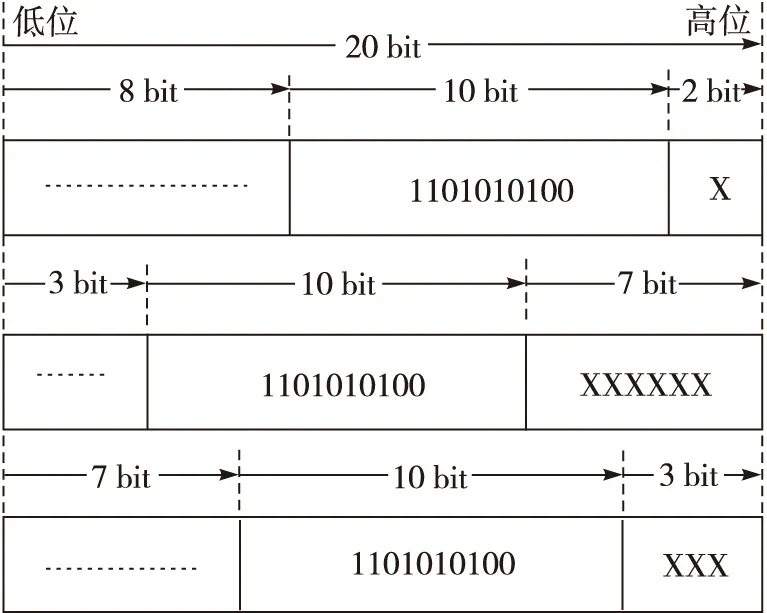

低位先出的情况:与高位先出的情况相同,在串行的编码数据之前也同样会有不确定数量的“0”,同样也假定“0”的数量为2,那么在串并转换的时候,这2个“0”就会占据并行数据的低位,后面的数据依次排列,如图3所示。这同样会导致还原回来的每组10 bit数据不再是原有的HDMI编码数据。与高位先出情况不同,在数据边界定位时,数据的连续性被破坏。

图3 低位先出示意图

3 HDMI数据同步模块设计

数据同步需要特定的可识别序列,在HDMI的编码数据中,视频周期的数据不具备这一特点,数据岛周期的编码数据虽然有一定的特征,但是一共有16种情况,数量较多,如表3所示。控制周期的编码数据在前面已经提到过,其编码方式简单,序列特征明显,并且只有4种编码,因此用于各通道的数据同步。

表3 数据岛周期编码

3.1 数据连续性处理

HDMI的编码数据在串行输出的过程中最低位将被最先传输,最高位将被最后输出。由上面对并串转换中低位先出情况的分析可知,HDMI接收端接收到的并行数据已经失去了原有数据的连续性,如图3所示。但是要进行数据同步必须保持数据整体的连续性。数据的连续性是由于低位先出而被破坏的,此时如果对图3中的数据进行低位先出的串行变化,那么数据还是连续的。为了保证数据整体的连续性,要对输入的并行10 bit数据进行翻转,即原本的A7~0,B7~A8变为0~A7,A8~B7,如图4所示,这样就保持了数据的连续性。

图4 数据处理示意图

3.2 检测序列长度分析

HDMI接收端的输入数据为并行的10 bit数据,经过翻转的处理之后保持了数据整体的连续性。数据这样处理之后,控制周期原有的编码方式将不再适用。为了能使数据同步,控制周期的编码方式也要有所变化,只需将原控制周期编码之后的数据进行翻转即可,新的编码方式如表4所示,可以与表2进行对比。

表4 控制周期新编码方式

由于在数据串行传输的过程中真正的数据前有不确定数量的“0”,因此经过倒置的10 bit数据的每一位都有可能是控制周期新编码序列的首位。最理想的情况下,当前10 bit数据的首位即为新编码序列的首位,那么这10 bit数据就为新的编码序列;另一种情况下,当前10 bit数据的末尾是新编码序列的首位,那就需要接下来的9 bit数据;最坏的情况下,当前10 bit数据不含新编码序列的首位,那么就需要接下来的10 bit数据。由以上可知,想要准确地鉴别出控制周期序列需要20 bit的数据,因此检测序列的最短长度为20 bit。

3.3 数据同步与通路对齐

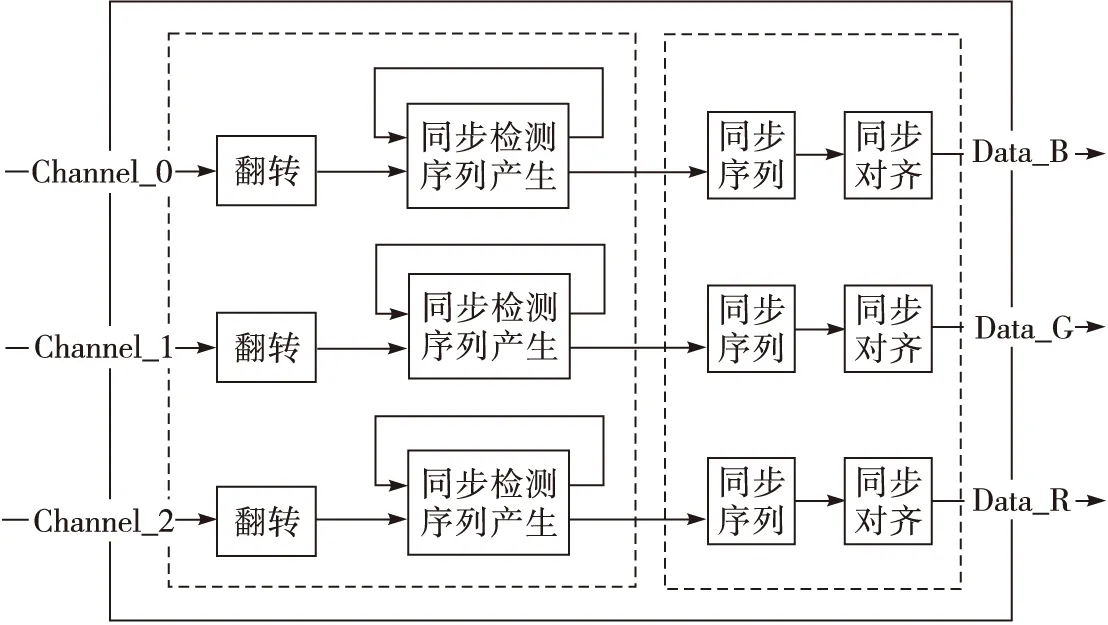

数据同步只需要找到特定的同步字符,在上面已经确定基本的方案。HDMI发送端和HDMI接收端之间有3条TMDS通路,但是由于不可能保证PCB的布线长度完全一致,噪声等对3条通路的影响完全相同,因此3条数据通路会有不同程度上的相对延时。通路对齐就是为了在HDMI接收端的内部消除3条数据通路的相对延时,对齐之后的数据用于HDMI数据解码。将数据的同步与通路数据对齐在同一模块中完成,电路的结构如图5所示。

图5 数据同步模块电路结构

控制周期新编码方式如表4所示,编码之后的数据有这样的特点:第9位和第8位是相同的;从第8位到第1位每相邻的任意两位都不同。根据这个特点可以更为简便地判断特征序列,不用再去与表4中的序列直接比较,只需按照上述序列特点进行相邻数位的比较,就可以识别出来特征序列。特征序列识别出来之后,就要进行不同通路的数据对齐。

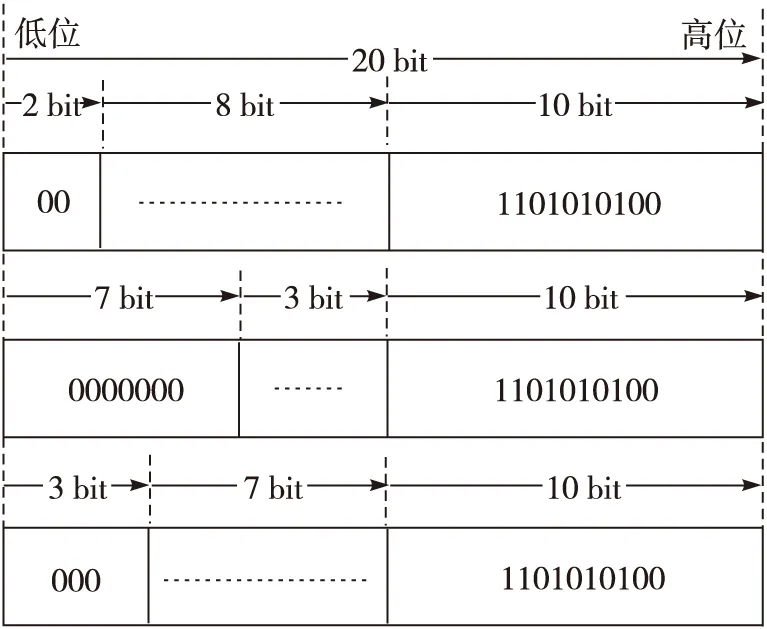

由上述可知,每条通路的同步序列中的特征序列的位置不同,即特征序列的首位可能出现的位置是不确定的,这是3条通路相对延时的表现,如图6所示。为了能够在20 bit的同步序列中定位特征序列,同步序列的每一组连续的10 bit序列都要进行相邻数位的比较。为了实现上面的描述,采用for循环结构,有限次数的for循环是可以综合的。用“n”来指示同步序列的每组连续10 bit序列的首位,其余位依次为n+1,n+2,n+3,…,n+8,n+9,n值的不同决定了特征序列的位置。在图6中,由上到下分别为3条通路的同步序列。每条通路的10 bit特征序列在同步序列中的位置是不同的,在图6中依次为2 bit,7 bit和3 bit,因此每条通路的n值分别为2,7,3。当n值确定之后,要对n值进行锁定,然后20 bit的同步序列根据n值向右移位,得到移位数据,如图7所示,将移位之后数据的高10位输出。这样既完成了对数据的同步,同时也完成了对不同通路的数据对齐,消除了后续模块中不同通路的相对延时。

图6 同步序列示意图

图7 对齐之后的序列

4 电路仿真及结果分析

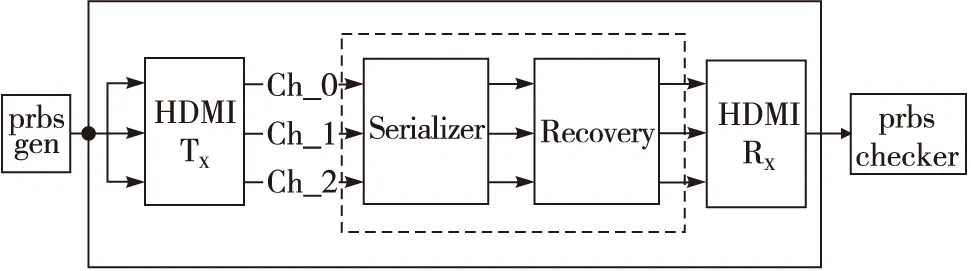

为了对数据同步模块进行验证,采用了如图8所示的仿真平台,仿真工具采用Cadence NC-Verilog。仿真平台由HDMI_Tx,HDMI_Rx,Serializer,Recovery,prbs_gen和prbs_checker组成。HDMI_Tx,HDMI_Rx为测试平台的核心部分,数据同步模块包含在HDMI_Rx中,为主要的验证对象。Prbs_gen和prbs_checker用来验证主体数据的正确性。Serializer和Recovery模块用来实现数据的并串转换和串并转换。由于仿真平台为数字系统,为了模拟真实情况,在这两个模块之间的每条通路都做了不同的延时处理,在图8中没有体现。

图8 仿真平台示意图

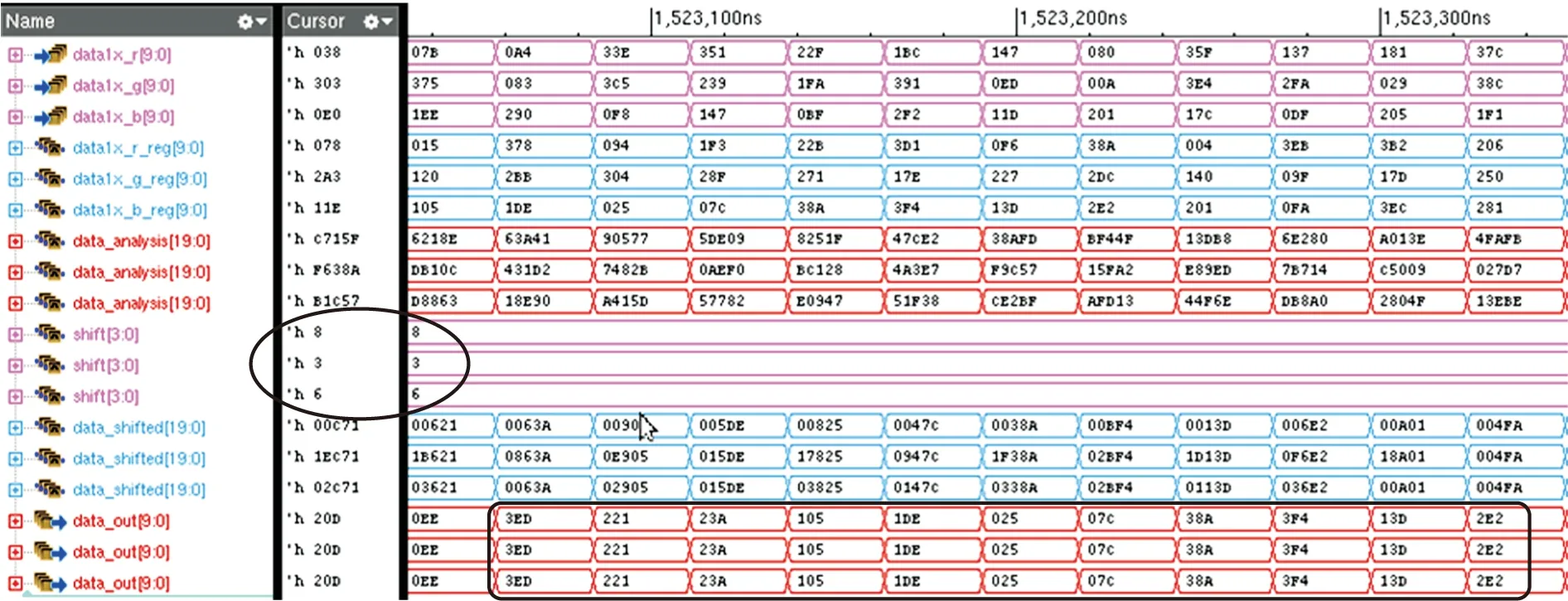

3条通路的视频数据都是由prbs_gen产生,完全相同。这样便对不同通路的数据进行分析验证。数据经过并串、串并转换之后,在经过数据同步模块,3条通路应得到完全相同的10 bit视频数据。图9为数据同步模块相关数据的仿真结果,图中的shift值为同步序列移位的n值。由图可知,不同通路的移位是不同的,分别为8位、3位和6位;data_out是移位之后的10 bit输出。仿真结果显示,数据同步模块的3条通路输出的视频数据是完全相同的,这与用同一个prbs_gen产生数据相吻合。因此说明该模块实现了预期的功能。

图9 数据同步模块的仿真波形(截图)

完整的数据流验证是由prbs_checker完成的。Prbs_gen产生12 bit的视频数据,在HDMI_Tx中经过色深编码、数据编码;在HDMI_Rx中经过数据解码、深色解码,输出12 bit的数据。3条数据通路的视频数据是完全相同的,因此只对一条通路进行检测。prbs_checker的检测结果如图10所示,图中same信号用来指示数据是否匹配,same信号呈现周期性的变化。视频数据是由prbs_gen产生的,因此在视频周期same的值为高电平,表示数据正确。在非视频周期,传输相对固定的数据,不是prbs序列,因此same信号为低电平。same信号的周期性变化是合理的,验证了数据通路的正确性,说明数据同步模块完全适用于HDMI系统。

图10 prbs_checker的仿真波形(截图)

5 结论

依据HDMI协议不同周期的编码特点以及数据传输连续性的特点,采用可综合的Verilog语言完成了数据同步模块的设计。采用NC-Verilog仿真工具,在同步模块和HDMI系统两个层次上进行验证。验证结果表明,设计的数据同步模块实现了预期功能,同时也适用于HDMI系统,能有效地提高HDMI接收端数据处理的能力。

[1]郭名坤.基于FPGA光纤与1_4标准HDMI接口转换方法[D].沈阳:沈阳工业大学,2014.

[2]冯传岗.HDMI_4K时代的高性价比视音频信号接口[J].数码影像时代,2014(3):100-107.

[3]High-definition multimedia interface specification version 1.4b[S].2011.

[4]刘文杰.HDMI接口编解码传输模块ASIC设计[J].微电子学,2014(12):763-766.

[5]陈文娟.HDMI标准在高清视频编码SoC设计中的应用[J].电视技术,2008,32(8):74-75.

李 新(1974— ),博士后,副教授,主要从事微电子技术研究;

梁春明(1991— ),硕士生,主研集成电路设计。

责任编辑:闫雯雯

Design of data synchronization module in HDMI receiver

LI Xin, LIANG Chunming

(ShenyangUniversityofTechnology,Shenyang110870,China)

Based on the analysis of HDMI protocol and the continuity of the data flow in the data parallel/serial,serial/parallel conversion,a solution is proposed to find the data boundary location and align different data paths at the same time for HDMI receiver. Designed with synthesized Verilog and verified the functionality by NC-Verilog and integrated to HDMI system. The data synchronization module achieves data location and data alignment,which can effectively improve data processing capabilities for HDMI receiver.

HDMI;continuity of data;data synchronization

李新,梁春明. HDMI接收端的数据同步模块设计[J].电视技术,2016,40(11):30-34. LI X, LIANG C M. Design of data synchronization module in HDMI receiver[J]. Video engineering,2016,40(11):30-34.

TN919.3

A

10.16280/j.videoe.2016.11.006

2016-04-20