CMOS集成电路ESD保护技术研究

董培培,张海涛

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.中国人民解放军95979部队,辽宁,沈阳110045)

CMOS集成电路ESD保护技术研究

董培培1,张海涛2

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.中国人民解放军95979部队,辽宁,沈阳110045)

介绍了ESD保护原理、测试方法及典型的ESD保护电路,针对2000V的HBM模型ESD保护指标要求,采用CSMC 0.5μm 25V(VGS)/25V(VDS)DPTM工艺模型和GGMOS器件进行了全芯片的ESD保护电路设计,并对ESD保护管的输出驱动级做了探索,在保证输出级ESD保护能力的同时,提高了输出端口的带负载能力。鉴于ESD保护结构工艺移植性较差,保护性能与工艺密切相关的特点,结合具体版图设计实践,总结了ESD保护结构版图设计的通用原则。这些原则旨在提高ESD保护结构的抗静电能力或提高ESD保护器件的工作可靠性,与具体的实现工艺无关。流片后的ESD实验表明,设计的ESD保护结构可以承受2000V HBM ESD攻击。

ESD保护;GGMOS器件;电路设计;版图设计;通用原则;工作可靠性

1 引 言

随着电路设计和制造工艺水平的发展,CMOS集成电路工艺尺寸不断缩小,单芯片集成度不断变大,且电路结构越来越复杂,极大提高了集成电路的性价比。与此同时,栅氧化层厚度不断减小、LDD与Salicide等先进工艺的应用、高分子材料的广泛应用等等,也加剧了集成电路ESD保护的严峻形势。

ESD保护的基本原理是为ESD放电提供快速的泄放路径,泄放路径不但要能均匀吸收ESD电流,避免局部过热,还要能钳位工作电路的电压,避免工作电路因电压过载而受损。ESD保护电路的移植性比较差,即在不同工艺条件下,相同电路结构实现的保护能力也会有显著不同,所以ESD保护是一个与电路结构及加工工艺均密切相关的技术难题。

旧学院入口处的建筑顶部,有一个巨大的穹顶,穹顶部分是1887年修建的,与原有的院落型建筑完美地结合在一起,可谓画龙点睛的一笔。穹顶上还有一座镀金雕像,名为“青春”,是苏格兰雕塑家约翰·哈奇森的作品。

2 常用ESD保护电路

在元件制造、使用到维修的整个电子产品生命周期内,任何一个环节都可能产生ESD事件。ESD引起芯片失效的原因主要有三个[1]:局部过热、电流密度过高或者电场过强,以上三个原因可同时发生作用。

2.1ESD模型与测试

对于集成电路而言,ESD保护电路的有效性取决于保护电路的结构及具体的ESD模型。根据ESD产生的原因及放电方式的不同,ESD模型通常分为四种:人体模型(HBM,Human-Body Model)、机器模型(MM,Machine Model)、器件充电模型(CDM,Charged-Device Model)和电场感应模型(FIM,Field-Induced Model)。四种ESD模型中,最为通行的是HBM模型,一般的商用芯片,都要求通过2kV人体模型的ESD保护检测[2]。

在实际应用中,芯片任意一个引脚都可能发生ESD事件,在进行ESD测试时,任意两个引脚之间都应该进行放电测试,每次放电检测都要包含正负两种极性[3],故ESD放电情况大致可以分为四种:①所有I/O引脚对地引脚正极性放电(PS)或负极性放电(NS);②所有I/O引脚对电源引脚正极性放电(PD)或负极性放电(ND);③所有I/O引脚(一次一根)对其它所有I/O引脚正或负极性放电;④电源引脚到地引脚的正或负极性放电。

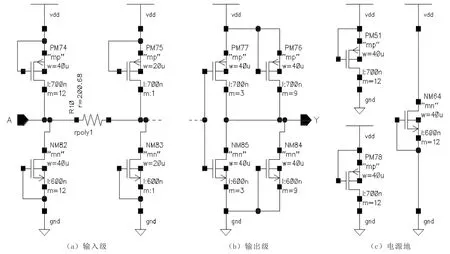

图4(c)为电源地ESD保护结构,在基本GGNMOS保护管结构的基础上,增加一个GDPMOS保护管,提高了电源地端口的ESD保护能力。

主要研究人体模型(HBM)的ESD保护方法,依据ESD保护原理及测试方法可知,ESD保护电路设计就是要建立对应四种ESD放电情况的ESD电流低阻泄放通路。ESD事件是一个高压、大电流的快速事件,用于ESD保护的器件必须能够快速吸收泄放ESD大电流,常用的ESD保护器件包括电阻、二极管、三极管、MOS管以及SCR(Silicon Controlled Rectifier)结构[1,4]。

芯片的ESD保护不是某个芯片引脚的问题,需要从芯片全局结构来整体考虑。全芯片ESD保护通常包括:输入级保护电路、输出级保护电路、电源地保护电路[3]。

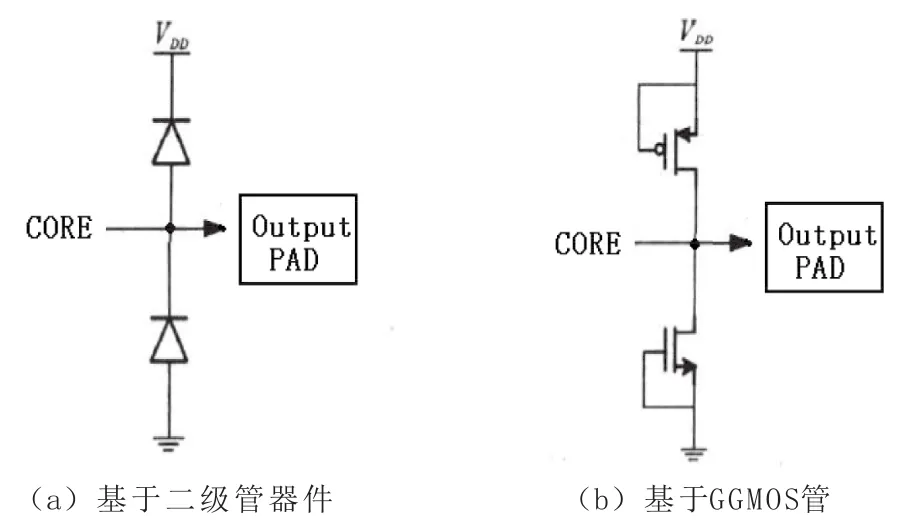

典型的输入级ESD保护电路如下图1所示。

图1 三种典型的输入级ESD保护电路

图1(a)使用二极管提供了PD、NS模式下ESD电流泄放通路,但对于ND、PS模式,二极管处于反偏状态,反偏箝位电压过高,电流泄放能力较弱。图1(b)使用GGMOS器件(包含GGNMOS和GDPMOS,GGNMOS为栅接地的NMOS器件,GDPMOS为栅接电源的PMOS器件),相对于二极管器件,它利用寄生三极管的回扫特性,提高了ND、PS模式下的ESD电流泄放能力,并有较低的箝位电平。当ESD电流很大时,GGMOS的衬底、金属线电阻都不能忽略,不能很好箝位住输入接收端电压(CORE侧),这就产生了图1(c)所示的主次两级ESD保护结构,主级结构(P1、N1)为ESD电流提供主要泄放路径;次级结构为紧靠接收输入端的一对小尺寸GGMOS管,用于大ESD电流时对输入接收端的栅电压进行箝位,电阻Rs通常取200~400Ω。

典型的输出级ESD保护电路如下图2所示。

图2 两种典型的输出级ESD保护电路

图2(a)与图1(a)的ESD保护原理、工作特点相同;图2(b)与图1(b)的ESD保护原理、工作特点相同。此外,在一些加工工艺中,图2(b)的保护管P3、N3可以合并成芯片的输出Buffer结构。典型的电源地ESD保护电路如图3所示。

3.2ESD保护版图设计

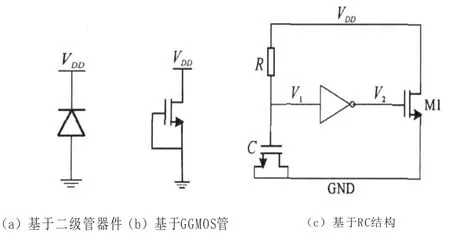

图3 三种典型的电源地ESD保护电路

图3(a)使用二极管做为电源地ESD保护器件,当电源受到负极性ESD攻击时,二极管正向导通,提供电流泄放通路,并进行电压箝位;当电源受到正极性ESD攻击时,二极管反向击穿,将电源电压箝位在一定电平,由于二极管反向击穿电压较高,且产生热量较大,极易损坏二极管保护器件。图3(b)采用一个GGNMOS器件做为电源地的ESD保护器件,利用寄生NPN三极管的回扫特性,提高了ESD电流的泄放能力,降低了箝位电平,只是在版图上占用面积较大。图3(c)是基于RC的ESD检测电路[5-6],利用电容感应ESD,开启NMOS管对ESD电流进行泄放。

3 ESD保护结构设计

研制的芯片有2000V HBM模型的ESD保护指标,选用CSMC 0.5μm 25V(VGS)/25V(VDS)DPTM工艺进行设计流片。

少数民族基础数学教育和普通数学教育有区别。少数民族学生在思维与语言上具有独特性,教师在备课时就要考虑到这些因素,在运用资源时要有创新性和针对性。“互联网+教育”只是一种辅助,教师才是课堂教学的主要引导者。

ESD保护管的沟宽很大,通常画成叉指结构。绘制叉指结构保护管需要注意:①源、漏端接触孔、通孔的间距及数量要相等,保证源端和漏端结中电流的均匀性;②在面积允许且满足芯片速度指标的前提下,适当加大保护管沟宽。

如果大学生创业者拥有一项或多项受保护的专利技术,风险投资家对其重视程度就会更高。领先或受保护的技术可以使初创企业跨入壁垒较高的行业优势区域,利用自身优势创造长期超额利润。Dormi实现了销售方面的整合,但缺乏相应的技术优势,因此难以跨入垄断竞争市场。从经济角度分析,如果未来Dormi不能在设计或材料方面有突破性创新,容易被市场淘汰。

图4 ESD保护电路

图4(a)为输入级ESD保护电路,采用主次两级ESD保护结构,PM74、NM82构成的主级结构提供输入端口对电源、地的主要ESD放电路径。当ESD电流很大时,PM75、NM83构成的次级保护结构能更好实现输入接收端的电压箝位。

(1)叉指结构

图4(b)输出级采用GGMOS保护管结构,GGMOS管的一部分“指头”用作输出驱动级,在保留GGMOS管ESD保护能力的同时,提高了芯片输出端口的带负载能力,这是输出级ESD保护结构的一个特色。

2.2典型ESD保护电路

此外,凤凰新华印务运用数字和网络技术,以科技的力量打造CCPP中国云出版印刷平台,实现出版“零距离”、印刷“零差异”、发行“零库存”、版权“零担忧”,以及“凤凰定制”等功能,大大简化了以往繁复的业务处理过程,实现了面对专业出版客户、大众客户的在线随时随地印刷服务。

(1)尽量避免设备空载运行,当部分设备发生故障或检修时,预计在短时间内不能恢复运行,必须关闭其他设备,既减少设备磨损,又节约电能损耗。同时,合理组织选煤生产,缩短设备停机时间,杜绝开空机运行。从制度管理上规定超过20 min钟的设备故障检修,必须停止其他空载设备,并在监控上进行量化监督,落实考核。

ESD保护结构的版图设计,必须按照所选工艺的ESD保护版图设计规则进行,总结ESD保护版图设计实践,有以下几个通用原则:

本研究施加零价铁导致土壤pH上升,这可能是由于零价铁氧化过程产生 OH-导致的(Fe0+O2+2H2O→2Fe2++4OH-),该过程有利于镉的吸附固定;氧化过程产生的Fe2+进一步通过微生物作用形成无定形铁(Qiao et al.,2018),有利于砷和镉吸附固定。

采用GGMOS管进行ESD保护电路设计,设计的全芯片ESD保护结构如图4所示。

3.1ESD保护电路设计

(2)保护管沟长选取

若工艺相同,栅长增大,GGNMOS保护管的抗静电能力降低;栅长过小又容易造成GGNMOS保护管的非均匀触发以及热载流子可靠性等问题[7-8]。故ESD保护管采用保护管设计规则推荐的最小栅长。

(3)对称设计

当前,如果将大型体育赛事在电视转播权方面的问题理解为赛事运作管理问题,倒不如在深层角度上将其理解为赛事运作管理的环境问题。在这个方面,运作大型体育赛事时要注意积极争取政府的大力支持,尽可能实现电视转播权的自主销售;在人员接待、资源供给方面为广播电视台提供更优质的服务,与广播电视台建立良好的合作关系;与广播电视台加强谈判,实现大型体育赛事转播销售模式的多元化;不断开发、利用、包装以资源置换得到的广告时段或其他节目资源,从而使资源产生的效益最大化;对具有完全自主销售权或转播权的大型体育赛事,应积极开拓海外电视转播市场,由此实现大型体育赛事电视转播权在我国以外的国际市场销售。

采用多个同类型的保护管(如图4中PM51、PM78)对电源地端口进行ESD保护时,要将保护管做成单元,并保证各个保护管相对保护端口的连接对称性,以实现ESD事件发生时各个保护管同时导通工作。

(4)栅源串接电阻

在中国翻译史上,合作翻译推动了佛教场域、基督教场域、西学场域在中国文化场域中的建构。合作翻译的译者构成变迁呈现一定的规律:早期以外来译者为主体,随后本土译者规模逐渐扩大,最后开启了独译历程。这种变迁一定程度上折射了源语文化和译语文化权力关系,反映了翻译场域与相邻场域及权力场域的互动关系。当译语文化处于强势地位时,译语文化以自我为中心,对外来文化持漠视态度,翻译场域处于边缘地位,译语文化知识分子对翻译不感兴趣。源语文化译者往往是翻译发起者,并可能在很长一段时间占据主导地位。

GGMOS保护管的栅、源间可以串联一个1~2K的电阻,以保证芯片引脚受到ESD攻击时,叉指结构ESD保护管的所有“手指”均导通工作,即提高了ESD保护管工作的可靠性。

4 结束语

介绍了ESD保护的原理、测试方法及典型电路,结合CSMC 0.5μm 25V(VGS)/25V(VDS)DPTM工艺设计了具体的ESD保护电路,并总结了ESD保护器件版图设计的通用原则。流片后的ESD实验表明,设计的ESD保护电路可以承受2000V HBM ESD攻击,对CMOS集成电路ESD保护设计具有一定的指导意义。

[1]陈志钧.CMOS集成电路ESD保护技术的研究和设计[D].成都:电子科技大学,2012:5-9.Chen Zhi-jun.Research and Design of CMOS lntegrated Circult ESD Protection Technology[D].ChengDu:University of Electronic Science and Technology of China,2012: 5-9.

[2]王大睿.CMOS电路中ESD保护结构的设计[J].中国集成电路,2007(6):37-41.WANG Da-rui.Construction Strategy of ESD Protection Circuit[J].China lntegrated Circult,2007(6):37-41.

[3]向洵,刘凡,杨伟,等.基于CMOS工艺的全芯片ESD保护电路设计[J].微电子学,2010,40(3):396-399.XIANG Xun,LIU Fan,YANG Wei,et al.Design of All Chip ESD Protection Circuit Based on CMOS Process[J].Microelectronics,2010,40(3):396-399.

[4]李冰,杨袁渊,董乾.基于SCR的ESD器件低触发电压设计[J].固体电子学研究与进展,2009,29(4):561-564.LI Bing,YANG Yuan-yuan,DONG Qian.Low-triggering Voltage Design of SCR-based ESD Protection Circuits[J].RESEARCH&PROGRESS 0F SSE,2009,29(4):561-564.

[5]MERRILL R,ISSAQ E.ESD design methodology[C].Proc EOS/ESD Symp.Lake Buena Vista,FL,USA,1993:233-237.

[6]KER M-D.Whole-chip ESD protection design with efficient VDD-to-VSS ESD clamp circuit for submicron CMOS VLSI[J].IEEE Trans Elec Dev,1999,46(1):173-183.

[7]郑若成,刘澄淇.ESD保护结构设计[J].电子与封装,2009(9):28-30.ZHENG Ruo-cheng,LIU Cheng-qi.ESD Protection Structure Design[J].ELECTRONICS&PACKAGING,2009(9):28-30.

[8]徐伟,冯全源.多指条形GG-NMOS结构ESD保护电路[J].微电子学,2009,39(1):58-60.XU Wei,FENG Quan-yuan.Multi-finger GG-NMOS ESD Protection Circuit[J].Microelectronics,2009,39(1):58-60.

Research on CMOS Integrated Circuit ESD Protection Technology

Dong Peipei1,Zhang Haitao2

(1.The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.Unit 95979 of Chinese People's Liberation Army,Shenyang 110045,China)

The principles,measurement methods and typical circuits of ESD Protection are introduced in this paper.Using CSMC 0.5μm 25V(VGS)/25V(VDS)DPTM Process and GGMOS devices,the ESD protection circuits of the whole chip are designed to achieve 2000V HBM ESD protection ability,and output driver designed with ESD protection FETs is explored to raise the driving ability of output pin while keeping the ESD protection ability.Because technology portability of ESD protection circuits is bad and ESD protection ability is highly related with technology,combined with layout design practice,the general principles of ESD layout design are presented.The principles,regardless of technology,aim at raising the protection ability or reliability of ESD protection structure.The ESD experiment of the fabricated chip shows that the designed ESD protection structure can endure 2000V HBM ESD attack.

ESD protection;GGMOS device;Circuit design;Layout design;General principle;Work reliability

10.3969/j.issn.1002-2279.2016.05.003

TN4

B

1002-2279(2016)05-0009-04

董培培(1984-),男,河南省新郑市人,工程师,主研方向:CMOS集成电路设计。

2015-10-20