适用于1553总线协议的内建自测试实现

印 琴,朱晓宇,于宗光,蔡洁明

(中国电子科技集团公司第58研究所,无锡214035)

·大规模集成电路设计、制造与应用·

适用于1553总线协议的内建自测试实现

印琴,朱晓宇,于宗光,蔡洁明

(中国电子科技集团公司第58研究所,无锡214035)

提出了一种适用于1553总线协议的内建自测试实现方法。该方法在传统协议处理器基础上,增加了用于存储测试向量的ROM、自测试逻辑电路及测试寄存器,能实现1553总线协议处理器的协议逻辑自测试、编解码自测试、RAM自测试,并将测试结果存储到内建自测试状态寄存器1CH中,用户通过访问该寄存器可以随时了解当前自测试的状态或结果。采用理论结合仿真的方法分析了协议处理器的自测试响应,仿真结果表明该协议处理器实现了内建自测试功能,内建自测试结果说明1553协议处理器的协议逻辑和RAM的读写功能均正常。该测试方法有效提高了测试覆盖率,降低了电路测试程序开发的难度。

1553总线;内建自测试;协议逻辑;编解码;RAM自测试;覆盖率

1 引 言

随着集成电路设计方法与工艺技术的不断进步,单个芯片实现的功能越来越复杂,集成电路的可测性问题越来越受到重视[1-2]。可测性设计中的内建自测试通过在芯片内部集成少量逻辑电路实现对整个芯片的测试。它的基本思想是由电路生成测试向量或预先将测试向量植入内部电路中,并依靠自身逻辑来判断测试[3-4]。1553数据总线因其高可靠性等诸多优点被广泛应用于航空、航天等多个领域。在上一代1553B系列产品的协议处理器中,虽然预留了部分用于自测试的寄存器,但测试向量还需要由外部CPU输入,繁重的工作量严重影响了产品的测试效率。为了解决这一问题,设计实现了一种无需从外部施加测试向量的内建自测试方法。

2 协议处理器自测试实现原理

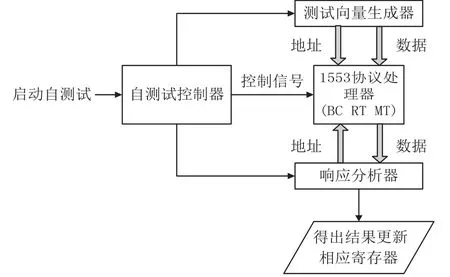

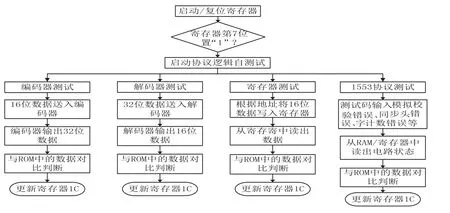

1553协议处理器的内建自测试属于离线自测试,即只有当协议处理器未处理消息时,才能启动自测试,其实现原理框图如图1所示。

图1 1553协议处理器内建自测试实现原理框图

实现内建自测试需要在芯片内部增加的电路主要有三部分:测试控制器、向量生成器、响应分析器[5-8]。一般通过测试控制器启动被测电路进入BIST模式,从而启动向量生成器,将预先设计好的各种测试向量施加给1553协议处理器,响应分析器捕捉电路各测试状态的反馈,将其与预定的测试向量做比较,分析记录测试结果。协议处理器中的自测试共分为两大部分,分别是4K×16大小的RAM自测试和协议自测试。其中协议自测试又具体细分为寄存器测试、编解码测试、协议逻辑测试。自测试的类型选择由自测试控制器在启动时通过对相应寄存器的配置实现。

3 协议处理器自测试启动

协议处理器的内建自测试启动有两种方式,分别是上电自启和通过启动/复位寄存器启动。其中上电自启只启动协议逻辑自测试,RAM自测试在上电后不会自启,需要在一定的条件下通过对寄存器03H的配置启动RAM自测试。

上电自启的协议逻辑测试期间,对寄存器/RAM进行的任何读写操作都会受到影响,所以在此期间,一旦进行了读写操作,会导致上电协议自测试中断,并且数据也不会正常的写入或读出。1553协议处理器中用于启动自测试的是一个地址为03H的启动/复位寄存器。当协议处理器工作在BC模式时,查看配置寄存器#1的第1位BC FRAME IN PROCESS可以确定BC是否在处理消息,如果该位置“0”,表示BC空闲,协议处理器将响应自测试控制器发出的自测试命令,进入自测试模式。同样,当协议处理器工作在RT/MT模式时,也是通过相应的判断方法在确认其空闲时才能成功启动自测试命令。

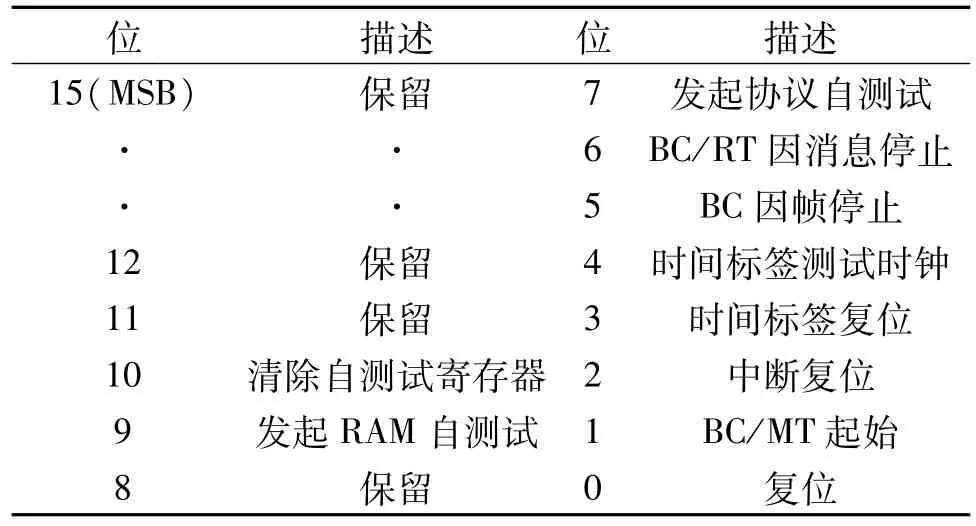

启动/复位寄存器(03H)中每一位的具体描述如表1所示。可以通过该寄存器的第7位发起协议自测试,通过第9位发起RAM自测试。第10位用来清除自测试寄存器,自测试寄存器中记录了测试结果,所以在启动新的测试时,一般要将该寄存器置为初始状态,以便记录当前发起的自测试结果。

表1 启动/复位寄存器

4 协议处理器的测试向量生成器

如前所述,协议处理器的测试分为两类,RAM自测试和协议自测试。对于RAM自测试,其测试向量生成器是由简单的逻辑电路产生两种测试码实现的。两种测试码分别是:写入的数据=当前地址、写入的数据=当前地址取反。而协议处理器的测试向量生成器是嵌在协议芯片内部的一块大小为4K×24的只读存储器ROM。完成所有的协议测试需要输入的测试向量大约为4000条,该4000条测试向量是参照DDC公开发表的1553协议测试码开发完成的,按照DDC的官方说法,其测试覆盖率可以达到99%。设计电路时,将所有测试向量预先存储在该只读存储器ROM中,启动测试后,将测试向量在控制信号的控制下写入被测试电路,开始测试。

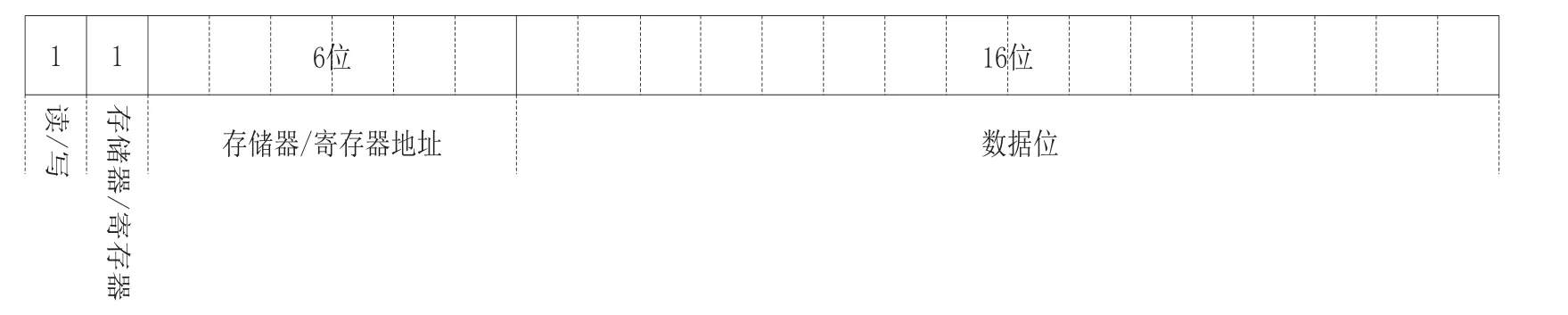

ROM测试向量定义如图2所示。ROM中定义的测试向量一共有24位,从高到低依次是读/写、存储器/寄存器、存储器/寄存器地址的低六位、数据位。读/写位置“0”,表明测试向量正写入寄存器或存储器,置“1”表明数据正从寄存器或存储器中读出并与ROM中标准的数据向量进行比较。存储器/寄存器位表明测试向量正写入或读出寄存器还是存储器,若该位置“0”则表示写入或读出的对象是寄存器,反之则为存储器。存储器/寄存器地址的低六位占据了ROM测试向量的第16至21位,其高10位地址存储在寄存器3EH中。ROM测试向量中的最后16位数据是向被测试寄存器/存储器写入的测试向量,或是与从被测试寄存器/存储器中读出结果进行比较的标准值。

图2 ROM测试向量定义图

5 协议处理器测试流程

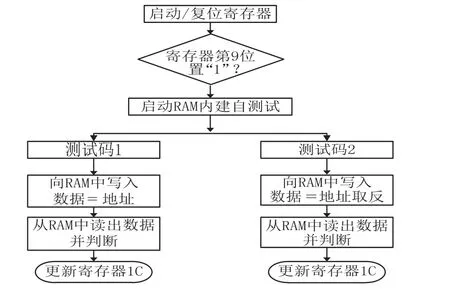

当启动/复位寄存器的位9置“1”时,电路启动RAM自测试。RAM自测试主要完成全片4K×16位RAM空间的写入与读出比较。在RAM自测逻辑的控制下,RAM测试向量生成器产生的测试码依次写入RAM各地址中,写入工作完成后再顺序将各地址中的数据读出,并与原写入数据进行比较。测试结果将体现在寄存器1CH对应的数据位中。RAM自测试是一种破坏性测试,原来存储在RAM中的数据将被测试数据覆盖,不可恢复。RAM自测试流程如图3所示。

当启动/复位寄存器的位7置“1”,且同时满足其他启动条件时,电路启动协议逻辑自测试。协议逻辑自测试主要完成协议处理器中寄存器、曼彻斯特编码器、曼彻斯特解码器、1553协议逻辑的全面测试。测试启动后,从测试向量生成器ROM中取出测试向量写入协议处理器电路,电路产生的测试响应会被存储在相应的寄存器或存储器中,将响应结果取出并与测试向量中的结果进行比对,比对结果将反应到寄存器1CH对应的数据位中。自测试设计时将协议处理器中的7个非配置寄存器用作测试寄存器,这些测试寄存器记录了测试状态,如果测试不通过,测试寄存器的相应位会被锁存,用来标记第一次发生错误时测试向量的读写状态、寄存器错误还是存储器错误、自测试ROM的地址值、寄存器/存储器地址、寄存器/存储器数据。通过查看测试寄存器中的数据即可定位到协议处理器中发生错误的点,实施改进措施。协议逻辑自测试流程如图4所示。

图3 RAM自测试流程图

图4 协议逻辑自测试流程图

6 协议处理器自测试响应分析

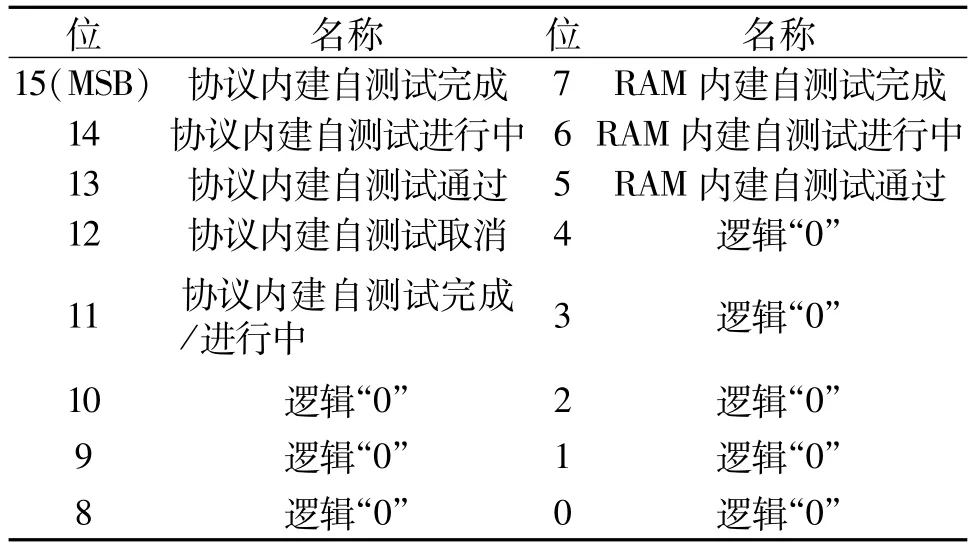

无论是RAM自测试还是协议自测试,其测试结果都会记录在内建自测试状态寄存器1CH中,用户可以随时通过读取该寄存器的值得到当前自测试的状态及结果。1CH中各个位的定义有协议内建自测试完成、协议内建自测试进行中、协议内建自测试通过、协议内建自测试取消、RAM内建自测试完成、RAM内建自测试进行中、RAM内建自测试通过。寄存器1CH的描述如表2所示。

以内建自测试完成为例对寄存器各位的描述做简单功能介绍。协议内建自测试完成后,1CH寄存器的最高位会置“1”,用户读取1CH值将得到的是8000H。通过启动/复位寄存器的第10位清除自测试寄存器或启动下一次协议内建自测试,该位可以复位,否则该位将一直保持为置“1”的状态。用户可随时通过读取内建自测试状态寄存器1CH的当前值,查看到当前自测试的状态。对设计实现的带内建自测试功能的协议处理器做以下几个功能仿真,以便能从仿真结果中直接明了的说明寄存器1CH所反映的自测试状态。

表2 内建自测试状态寄存器(1CH)

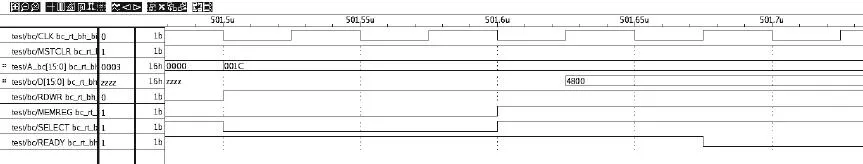

首先对协议自测试进行两个时间点的仿真,第一个时间点的功能仿真如下:在20MHz的时钟频率下,协议处理器硬件复位启动后大约500μs之后,对寄存器1CH进行读操作。理论上分析,协议逻辑自测试时,完成一个测试向量写入及比较的时间为8个时钟周期,4000条测试向量需要8×4000=32000个时钟周期,则在20MHz时钟条件下完成自测试需要的时间为1.6ms,所以在自测试开始500μs后,协议内建自测试应该还处在进行阶段。该仿真得到如图5所示,由波形图可知,自测试后500μs时寄存器1CH的值为4800H,对应的寄存器1CH中的第14位和第11位置“1”,其余位置“0”,表明协议内建自测试正在进行中,与理论分析相符。

第二个时间点的功能仿真如下:在20MHz的时钟频率下,协议处理器硬件复位启动后大约1.8ms之后,对寄存器1CH进行读操作。理论分析可知,1.8ms之后,协议内建自测试应该完成。得到的协议自测试仿真波形见图6,由波形图可知,自测试1.8ms之后寄存器1CH的值为A800H,对应的寄存器1CH中的第15位、第13位及第11位置“1”,其余位置“0”,表明协议内建自测试完成且通过,从而证明了协议处理器内部协议逻辑正确。

图5 协议自测试仿真波形a

图6 协议自测试仿真波形b

接着对RAM自测试进行功能仿真。对RAM自测试的仿真操作如下:在协议上电自测试完成后,向寄存器03H中写入0400H,先将寄存器1CH清零,再向寄存器03H中写入0200H,发起RAM自测试。RAM内建自测试设计时,将一个地址写入时间设为3个时钟周期,一个地址的读出时间设为2个时钟周期,完成全地址的写入读出需要4K×5个时钟周期,两种测试码共需4K×5×2=40960个时钟周期。所以第一种RAM自测试仿真是在启动RAM自测试大概20000个时钟周期时读取1CH内的值,仿真波形图如图7所示。由波形图可知,此时读取到的1CH的值为0040H,对应的寄存器1CH中的第6位置“1”,其余位置“0”,表明RAM内建测试正在进行,与理论预期的仿真结果相符。

图7 RAM自测试仿真波形a

第二种RAM自测试仿真是在启动RAM自测试大概41000个时钟周期时读取1CH内的值,仿真波形图如图8所示。由波形图可知,此时读取到的1CH的值为00A0H,对应的寄存器1CH中的第7位和第5位置“1”,其余位置“0”,表明RAM内建自测试完成且通过,从而证明了协议处理器内部RAM逻辑能正确的完成读写功能。

图8 RAM自测试仿真波形b

7 结束语

阐述了适用于1553总线的内建自测试实现原理、自测试的启动、自测试的向量生成器及测试流程,其中测试向量生成器ROM中预先存储的4000条测试向量使得测试覆盖率达到了99%,有效减轻了测试工作量,提高了测试效率,最后通过理论结合仿真分析了协议处理器的自测试响应。从仿真结果上说明了协议内建自测试的实现,并通过了协议内建自测试仿真,测试实现了1553协议处理器的协议逻辑和RAM的读写功能。

[1]魏淑华,禚永.基于内建自测试的测试向量生成方法[J].电脑与电信,2014,20(6):44-46.Wei Shuhua,Zhuo Yong.Test Vector Generation Methods Based on BIST[J].Computer&Telecommunication,2014,20(6):44-46.

[2]路思安,史峥,严晓浪.面向系统芯片的可测性设计[J].微电子学,2001,31(6):440-442.Lu Sian,Shi Zheng,Yan Xiaolang.SOC-Oriented Design for Testability[J].Microelectronics,2001,31(6):440-442.

[3]廖寅龙,田泽,赵强,刘敏侠.软件与MBIST协同的片内SRAM测试方法研究[J].计算机技术与发展,2015,25(6):155-161.Liao Yinlong,Tian Ze,Zhao Qiang,Liu Minxia.Research on SRAM Testing Integrated in SoC of Software and MBIST[J].Computer Technology and Development,2015,25(6):155-161.

[4]桂江华,钱黎明,申柏泉,等.SOC中的MBIST设计[J].电子与封装,2011,11(1):26-28.Gui Jianghua,Qian Liming,Shen Baiquan,et al.The MBIST Architecture for SOC[J].Electronics&Package,2011,11(1):26-28.

[5]涂吉,王子龙,李立健.BIST测试激励的聚类压缩方法[J].计算机辅助设计与图形学学报,2014,26(6):983-990.Tu JI,Wang Zilong,Li Lijian.Clustering Compression of Test Pattern for BIST[J].Journal of Computer-Aided Design&Computer Graphics,2014,26(6):983-990.

[6]孟觉,樊晓光,邬蒙,等.芯片级BIST控制器的设计与实现[J].计算机工程,2011,37(21):238-251.Meng Jue,Fan Xiaoguang,Wu Meng,et al.Design and Implementation of Chip-level BIST Controller[J].Computer Engineering,2011,37(21):238-251.

[7]段军棋.基于边界扫描的测试算法和BIST设计技术研究[D].成都:电子科技大学,2004.Duan Junqi.Study Design Technology on DFT and BIST[D].Chengdu:University of Electronic Science and Technology of China,2004.

[8]Tehranipour M H,Navabi Z.An Efficient BIST Method for Testing of Embedded SRAMs[C].//Proc.of IEEE InternationalSymposiumonCircuitsandSystems.Sydney,Australia:IEEE Computer Society Press,2001.

Built-in Self Test Realization for 1553 Bus Protocol

Yin Qin,Zhu Xiaoyu,Yu Zongguang,Cai Jieming

(No.58 Research Institute of China Electronics Technology Group Corporation,Wuxi 214035,China)

This paper proposes a method of realizing build-in self test for 1553 bus protocol.On basis of traditional protocol processor,ROM for store test vector,self test logic circuit and test registers are added to complete protocol logic self test,CODEC self test and RAM self test,and store the test results into the build-in self test register 1CH so as to get the state or results of current self test by accessing the register 1CH at any time.The results of the theory analysis and the simulation show that the function of build-in self test is achieved by this protocol processor,and the test results indicate that the protocol logic circuit and read-write ability of RAM are correct.The test method improves the test fraction of coverage effectively and reduces the difficulty of exploiting circuit test procedures.

1553 bus;Build-in self test;Protocol logic;CODEC;RAM self test;Fraction of coverage

10.3969/j.issn.1002-2279.2016.05.001

TN492

A

1002-2279(2016)05-0001-05

印琴(1989-),女,江苏省泰兴人,硕士,助理工程师,主研方向:数字集成电路设计。

于宗光(1964-),男,山东潍坊人,博士,教授,博士生导师,主研方向:集成电路设计开发。

2016-04-26