IP核打包及验证方法研究

刘 佳,屈 艳

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.辽宁省医疗器械检验检测院,沈阳110179)

IP核打包及验证方法研究

刘佳1,屈艳2

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.辽宁省医疗器械检验检测院,沈阳110179)

IP核是集成电路设计的升华,是超大规模SoC电路设计不可或缺的物质基础。IP核打包是IP核发布给用户之前一个非常重要的环节。目前,IP核的格式比较灵活,有coreKit、IPXACT等。考虑到IP核的完整性,以coreKit格式为例,借助于coreTools EDA工具对IP核打包及验证方法进行了较为详细的研究。先从IP核的数据准备开始,指出需要提供HDL配置和接口定义两个相关的辅助文件;再从打包过程的七个步骤:建立打包流程、启动coreBuilder工具、输入设置、存储器映射、验证、综合设置和打包等,对其进行一步一步阐述;最后通过IP核发布和IP核集成对IP核打包的结果加以验证,证明IP核包的正确性和实用性。

IP核;打包;发布;综合策略;约束;集成;验证

1 引 言

目前,IP核在集成电路设计中已经成为SoC产品快速研发的基础,其地位也变得越来越重要。为便于IP核交易,IP核打包是其中不可缺少的一步,因此,借助主流的EDA工具,开展对IP核打包及验证方法的研究。

2 IP核数据准备

IP核是RTL源代码、相关说明文档、仿真环境、脚本等多种信息的集合,必须通过代码质量分析、仿真验证、逻辑等效性检查等方式确认数据的正确性,部分IP核数据组织结构如图1所示。

图1 部分IP 核数据组织结构

同时还需要准备两个文件,一个是HDL配置文件[1],如图2所示。

图2 部分HDL配置文件

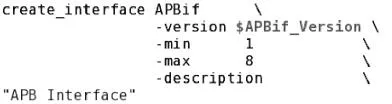

另一个是接口定义文件,使用create_interface、create_interface_parameter、set_interface_parameter_ attribute、create_interface_port、complete_interface_ definition等命令进行声明,如图3所示。

图3 部分接口定义文件

3 打包过程

IP核打包过程可以使用coreBuilder及类似的EDA工具,将IP核数据打包成Synopsys公司的coreKit格式或第三方的IP-XACT格式。具体方法如下:

(1)建立打包流程

IP核打包流程主要包括三部分:IP核数据准备、IP核打包和IP核验证(见图4)。

图4 IP核打包流程

(2)启动coreBuilder工具

在命令行提示符中输入coreBuilder&启动图形界面,如图5所示。在菜单File下选择New Workspace创建新的工作区,名称为can_coreKit,同时在Output Format域选择coreKit或是IP-XACT Component[2],如图6所示,再点击OK按钮,出现如图7所示的图形窗口。

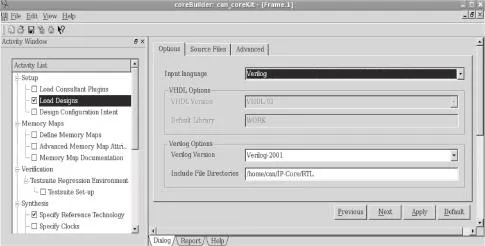

(3)输入设置(Setup)

在图5左边的Activity List窗口中,选中Load Designs标签,在右边的窗口中将出现Options、Source Files和Advanced选项卡。①在Options选项卡中,在设置输入语言类型栏选中Verilog;在Verilog版本栏选择Verilog-2001;在包含文件目录中输入目录地址;再单击Apply按钮。如图5中右边区域所示。②在Source Files选项卡中,单击“Append to HDL Files From Directory…”按钮,将RTL目录中的全部代码添加到工作区;再单击Apply按钮。③在Source Files选项卡中,在Tcl intent search path栏中通过点击方框按钮将所需要的Tcl文件目录加入到工作区中;在Extra link library栏中通过点击方框按钮将所需要的库文件加入到工作区中;再单击Apply按钮。

图5 coreBuilder图形界面

如果在该过程中输入的数据和相关设计正确,则在Load Designs标签前面的方框中出现“√”;否则需要根据图3中Console Windows中出现的信息进行修改,直至方框中出现“√”为止。

在左边的Activity List窗口中,选中Design Configuration Intent标签,在右边的窗口中将出现相关的配置信息,包括参数名称、缺省值、只读参数、顺序等,根据设计情况如实填写,再单击Apply按钮。

图6 输出格式选择

图7 can_coreKit工作区

(4)存储器映射(Memory Maps)

根据设计情况,如需要设置存储器映射,则要在图5左边的Memory Maps窗口中对Define Memory Maps、Advanced Memory Map Attribute和Design Configuration Intent标签进行相关设置。

(5)验证(Verification)

IP核的验证环境是IP核设计中一个非常重要的部分,目的是在数据提取后验证IP核的正确性。在图5左边的Activity List窗口中,选中Verification标签的Testsuite Set-up标签,在其右边窗口中对测试组、测试配置等进行设置。

2012年9月到2017年2月选择在我院诊治的胸段食管癌患者172例,纳入标准:病理证实的胸段食管癌患者;接受放疗者;患者知情同意本研究;都采用新型颈胸膜固定;卡氏评分≥70分者;放疗前临床相关检查排除远处转移者;研究得到医院伦理委员会的批准。排除标准:复发癌或已呈恶病质患者;精神疾病患者;妊娠与哺乳期妇女。根据放疗时双手放置方式的不同分为观察组72例与对照组100例,两组患者的性别、年龄、病灶部位、体重指数、临床分期、组织学分化情况等对比无明显差异(P>0.05)。见表1。

(6)综合设置(Synthesis)

在图5左边的Activity List窗口中,选中Synthesis标签,设置如下:①在Specify Reference Technology标签中,将设置max.db为目标库;将max.db、min.db、RAM_max.db、RAM_min.db等设置为链接库;将min.db、RAM_min.db设置为最快时序库[3]。②选中Specify Clocks标签,在图3中底部coreBuilder>右边空白区域内输入read_sdc Script/cnst/constraints.tcl命令,读入时钟约束[4]。③选中Specify Synthesis Methodology标签,根据设计的具体情况对综合过程中的策略控制、综合指示、综合控制、形式验证等内容进行相应设置。④选中Specify Test Methodology标签,根据设计的可测试性结构包括测试时钟周期、扫描方法、自动修复策略、内建自测试、测试点插入等内容。⑤在Specify Timing Exception标签中,声明IP核中的伪路径、多周期路径、最大延迟、最小延迟等。如果约束保存在constraints.tcl文件中,则②中的命令将读入对应约束信息,需在窗口中完成约束信息的确认。⑥在Specify Ports Constraints标签中,声明IP核中的输入输出端口延迟、输出负载、输入斜率等。如果约束保存在constraints.tcl文件中,则②中的命令将读入对应约束信息,需在窗口中完成约束信息的确认。⑦在Verify Intents标签中,通过工具完成对所有综合约束完整性和一致性的确认。

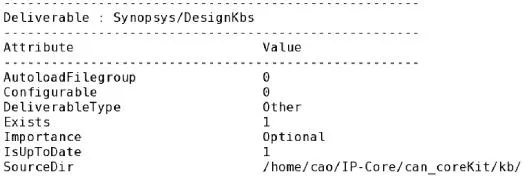

(7)打包(Package)

最后的打包过程分五步完成,①在Create Integration Workspace标签中指定根目录、工作区、文件组等内容;②在SoC Assembly Intent标签中,添加载入接口定义、添加接口等信息,为SoC集成作必要的准备[5];③在Create Bill of Materials标签中,添加文件组配置文件、自动载入等信息,点击Apply按钮生成BoM文件,部分BoM文件内容如图8所示;④在Set Up Help Menu标签中,添加MenuText、Description等相关信息;⑤在Build coreKit标签中,设置coreKit名称、版本、供应商名称、实现工具等信息。生成的coreKit目录如图9所示。

图8 部分BoM文件

图9 coreKit目录

4 结果验证

在验证IP核打包结果之前,需要使用coreConsultant工具将coreKit数据提取出来,然后再进行功能验证、形式验证和静态时序分析,以确保数据的可重用性[6]。

在命令行提示符中输入coreConsultant&启动图形界面,通过File菜单下Install coreKit…窗口安装IP核,再根据使用手册进行配置生成满足应用要求的设计数据[7]。

(1)功能验证

在设计数据的Verification/VCS目录下,运行VCS-f file.f-l tb.log命令产生可执行文件simv,再运行simv产生仿真报告来验证功能的正确性[8];

(2)形式验证

在设计数据的Script/lec目录下,运行fm_ shell-f lec.tcl命令产生形式验证的报告来确认RTL代码、门级网表的一致性及lec.tcl文件的正确性[9];

(3)静态时序分析

在设计数据的Script/sta目录下,运行pt_ shell-f sta.tcl命令产生静态时序分析报告来确认sta.tcl文件的正确性[10]。

5 结束语

CAN IP核是一个比较简单的设计,文章仅对其打包及验证方法进行了较为详细的研究。工程师在进行IP核打包时,应根据设计的具体情况,增加或调整相应的配置参数以达到IP核的可重用性。

[1]Synopsys Customer Education Services.coreBuilder Tutorial[M].Beijing:Synopsys Inc.,2015.

[2]Synopsys Customer Education Services.coreBuilder User Guide[M].Beijing:Synopsys Inc.,2015.

[3]Synopsys Customer Education Services.Design Compiler User Guide[M].Beijing:Synopsys Inc.,2015.

[4]Synopsys Customer Education Services.Synopsys Timing Constraints and Optimization User Guide[M].Beijing:Synopsys Inc.,2015.

[5]coreAssembler User Guide[M].Beijing:Synopsys Inc.,2015.

[6]许柯.可重用IP核验证方法研究[J].科技资讯,2008(26):26-27.Xu Ke.The Research Of Reusable IP Core Verification Method[J].Science&Technology Information.2008(26):26-27.

[7]Synopsys Customer Education Services.coreConsultant User Guide[M].Beijing:Synopsys Inc.,2015.

[8]Synopsys Customer Education Services.VCS MX/VCS MXi User Guide[M].Beijing:Synopsys Inc.,2015.

[9]Synopsys Customer Education Services.Formality User Guide[M].Beijing:Synopsys Inc.,2015.

[10]Synopsys Customer Education Services.PrimeTime User Guide[M].Beijing:Synopsys Inc.,2015.

Study of IP Core Package and Verification Methods

Liu Jia1,Qu Yan2

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.Liaoning Medical Device Test Institute,Shenyang 110179,China)

IP Core,as the sublimation of IC designs,is the basis for design of very large scale SoC circuits.IP package is one of very important link before IP core is released to users.The formats of IP Core such as coreKit and IP-XAC are flexible.In consideration of the completeness of IP Core,coreKit format is used as an example to make more detailed studies on the method of IP core package and verification by means of coreTools EDA tool.Firstly,for data preparation,two related and auxiliary files i.e.HDL configuration and interface definition are required.Then,the process of packaging,seven steps such as setting up package flow,invoking coreBuilder tool,input setup,memory maps,verification,synthesis setup and package,is described accordingly.Finally,the result of IP core package is verified through IP core release and IP core integration,which proves the correctness and practicability of IP core package.

IP Core;Package;Release;Synthesis strategy;Constraint;Integration;Verification

10.3969/j.issn.1002-2279.2016.05.004

TN4

A

1002-2279(2016)05-0013-04

刘佳(1982-),女,辽宁省沈阳市人,工程师,主研方向:科研管理。

2015-03-15