DDR3-SDRAM控制器设计及FPGA实现

李元兵 姚远程 秦明伟

(西南科技大学信息工程学院1,四川 绵阳 621010;特殊环境机器人技术四川省重点实验室2,四川 绵阳 621010)

DDR3-SDRAM控制器设计及FPGA实现

李元兵1,2姚远程1,2秦明伟1,2

(西南科技大学信息工程学院1,四川 绵阳 621010;特殊环境机器人技术四川省重点实验室2,四川 绵阳 621010)

针对自适应接收机中高速A/D采样数据对高带宽和大容量的需求,提出一种DDR3控制器设计方案。采用在MIG IP核的基础上添加用户接口控制程序的设计方法,利用ZC706评估板实现了DDR3的读写控制。设计方案具有较高的可移植性和简单的用户接口,可以灵活地应用到不同的工程中。仿真和板级测试表明,DDR3可在800 MHz的接口频率工作,传输速度可达1 600 MT/s,验证了系统的可行性和正确性,其将有助于解决海量数据的高速缓存问题。

存储器 控制器 FPGA 高带宽 大容量 用户接口 数据模块 模数转换

0 引言

当前,在诸多通信芯片和系统的研发中,经常用到各种大容量、高速读写存储器件。同步动态随机存储器(synchronous dynamic random access memory,SDRAM)以其价格低、速度快、容量大等特点,广受开发者的青睐[1]。其中,DDR2和DDR3发展成熟、应用广泛。DDR3在DDR2的基础上有了进一步的发展和改进,因此更具优势,已成为工程人员的首选方案。由于DDR3不能直接识别处理器的访问请求[2],所以有必要设计一个DDR3控制器,以控制DDR3的读写。

基于ZC706评估板,针对高速数据通过DDR3缓存的应用背景,利用Xilinx官方的MIG IP核,实现了DDR3控制器的设计,并在板上完成了验证。在评估板上,融合了ARM Cortex-A9处理器和Xilinx Zynq-7000系列FPGA芯片XC7Z045。在存储方面,FPGA连接了一条容量为1 GB的SODIMM式内存条,充分满足设计需要。

1 DDR3-SDRAM介绍

设计中使用的DDR3-SDRAM(以下简称DDR3)为镁光公司的MT8JTF12864HZ-1G6内存条。该内存条由8颗128 MB的内存颗粒构成,它们组合在一起构成单RANK,存储容量为1 GB。每颗存储颗粒的数据位宽是8 B,8颗放在一起组成了数据位宽是64 B的存储条,再加上设置其突发长度为8,所以每次读写的数据位宽可以达到512 B,很大程度上提高了DDR3的读写效率。每个存储颗粒拥有8个逻辑BANK,对应3根BANK选择线,所有存储颗粒复用14根行地址线、10根列地址线。

DDR3较上一代DDR2有一些重要改进和新的特点:预取能力变为8 B,是DDR2预取能力的两倍,有效地克服了核心频率较低的问题;新增加ZQ校准功能;数据总线和控制总线使用独立的参考电压,以提高系统数据总线的信噪等级;突发长度(burst length,BL)由DDR2的4变为8;增加了突发突变(burst chop,BC)模式等[3-4]。

在功耗方面,DDR3的功耗不到DDR2的75%,功耗明显降低,其最显著的表现就是DDR3的核心电压从DDR2的1.8 V降为1.5 V。除了电压降低以外,DDR3还有许多节能方面的改进,如:重置、温度自刷新(self refresh temperature,SRT)、局部自刷新(partial array self-refresh,PASR)等。重置功能是DDR3新增加的,这简化了DDR3的初始化处理。当重置信号激活时,DDR3不会进行任何操作,仅保持最少的活动量来节省功耗;温度自刷新功能通过芯片的温度来选择刷新频率,在确保数据不遗漏的情况下,降低刷新频率,减少功耗;局部自刷新使得DDR3只需刷新某些逻辑BANK,避免全部刷新,从而尽量减少自刷新功耗。

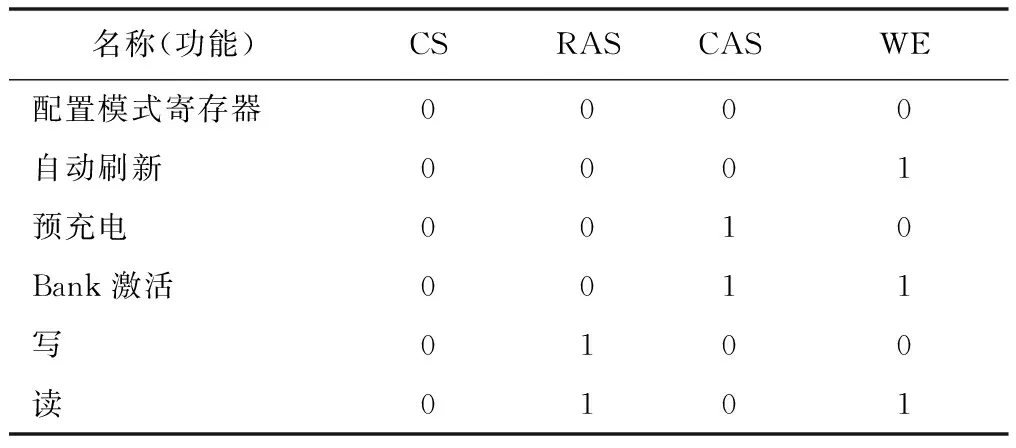

配置DDR3芯片的方法是设置其内部的模式寄存器和扩展寄存器,不同的配置将导致DDR3在不同的模式下工作。决定其工作状态的操作指令有片选信号(chip select,CS)、行地址选择信号(row address strobe, RAS)、列地址选择信号(column address strobe,CAS)和写使能信号(write enable,WE),它们的组合决定了DDR3的工作方式,如表1所示。

表1 操作指令集

表1中:1代表高电平,0代表低电平。控制器必须为DDR3提供满足时序要求的这些控制信号,才能准确地控制DDR3的各种不同操作。

DDR3上电后,一定要遵从标准协议的规定进行初始化,并配置一些基本参数,否则会导致DDR3的工作状态不确定。在初始化的过程中,对寄存器进行设置,同时可以完成CAS延迟、突发长度、突发类型、片上端接电阻(ODT)值等参数的设定[5]。只有在初始化完成后,DDR3才能在就绪状态工作,等待相应的操作指令;进入正常工作状态后,用户才能控制其读写。

2 DDR3 SDRAM控制器设计

2.1 总体设计

由于DDR3的控制逻辑复杂,为了缩短工程人员的开发周期,Xilinx公司为开发人员提供了可以用来生成DDR3控制器的MIG IP核。开发人员只要通过IP核的GUI选择内存芯片,并设置控制器的相关参数,便可在IP核自动生成设计所需的RTL文件、用户约束文件以及网表文件。用户通过更改一些接口,即可生成测试工程,并进行DDR3读写测试。设计将控制器的系统时钟和参考时钟都设置为200 MHz。

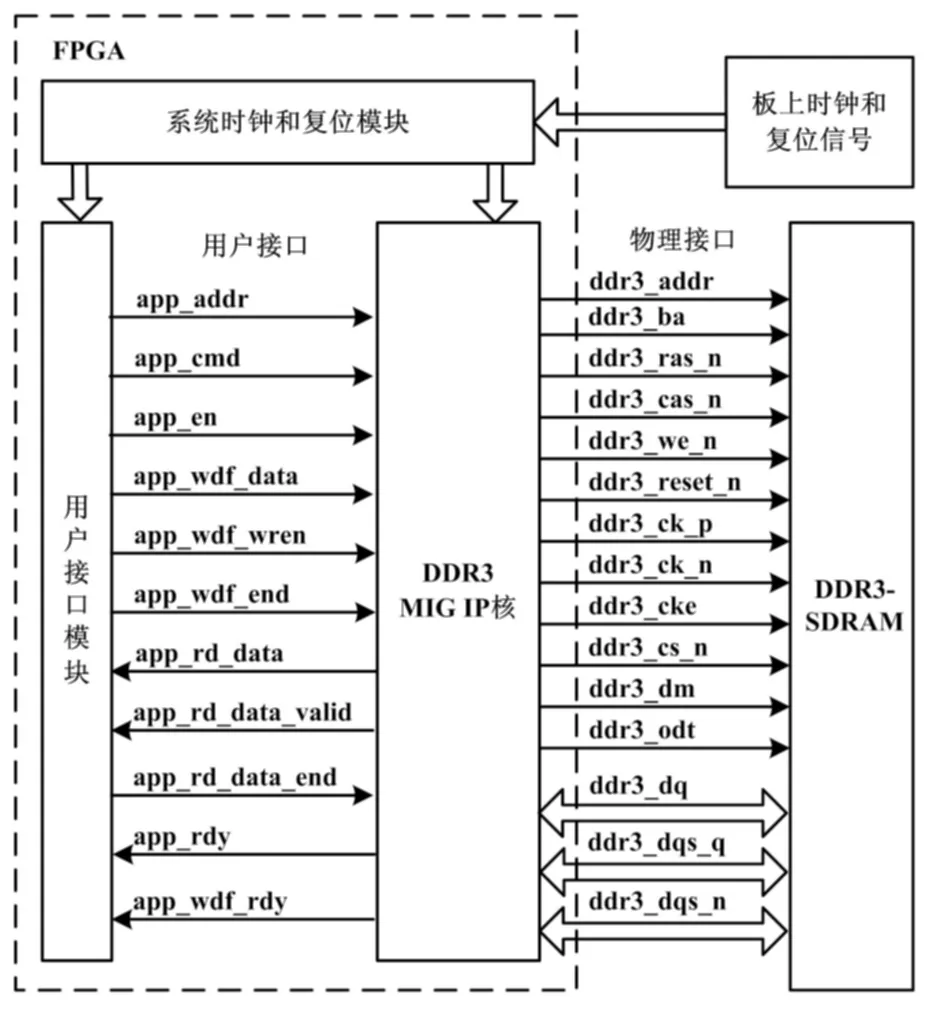

控制器由系统时钟和复位模块、用户接口模块、MIG IP核生成的控制器接口模块组成,其结构如图1所示。

图1 控制器结构图

图1中:板上系统时钟为200 MHz差分时钟,经过MIG IP核中的锁相环倍频到800 MHz,作为控制器的主时钟频率。由于DDR3能够在时钟的上下沿都传输数据,因此,其传输速度达到1 600 MT/s。DDR3控制器封装了用户逻辑到存储器逻辑的转换,所以用户只需进行用户接口设计,按照MIG的读写时序向控制器发送命令、地址和数据[6-7]。MIG的读写时序相对简单,利于用户实现。因此,用户接口模块是DDR3控制系统的核心内容,也是设计的重点。

2.2 用户接口模块设计

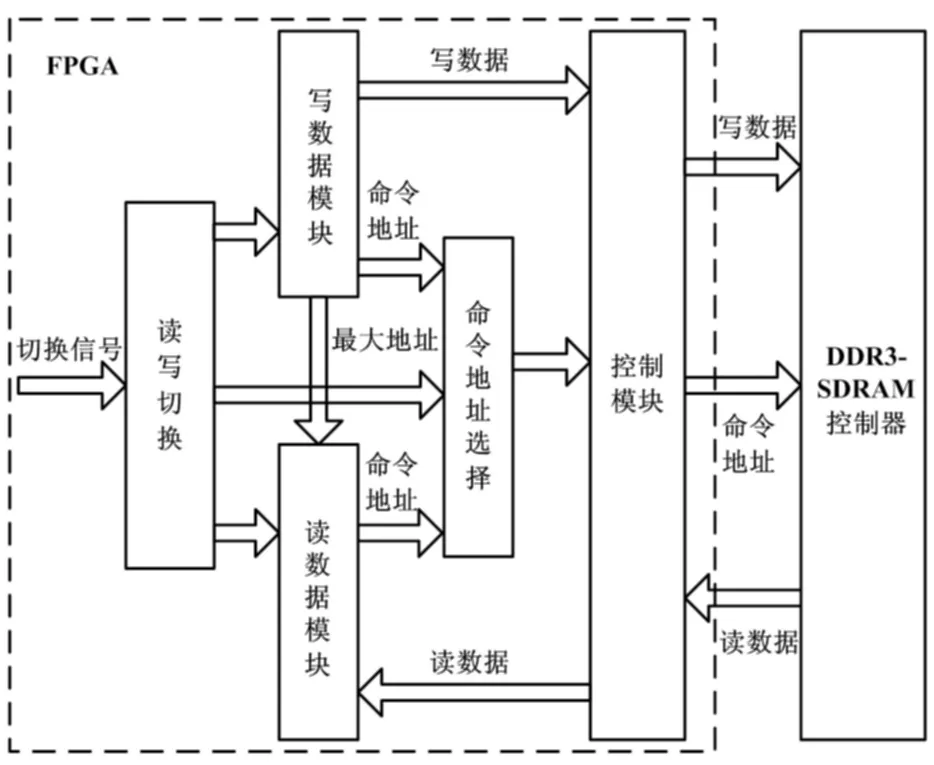

用户接口是用户控制DDR3的直接操作端口,需由用户根据工程的数据量大小、数据位宽、数据速率、缓存深度等参数自行设计。用户接口设计方案如图2所示,主要包括写数据模块、读数据模块和控制模块。考虑到DDR3只包含一套地址结构,因此读写不能同时进行。

本文采用将读写数据通道分开的设计思想,对DDR3进行分时操作。根据工程中数据量的大小和DDR3的容量大小计算读写的时间,并按照这个时间产生外部切换信号,由外部切换信号来控制DDR3的读写;根据切换信号,分别将读写的命令、地址和数据发送给控制模块,在控制模块内部通过FIFO缓存的方式[8]完成数据的跨时钟域处理,以避免产生亚稳态,确保数据完整性[9]。

图2 用户接口框图

当对DDR3进行写操作时,由写数据模块产生命令、地址和数据,通过地址命令选择器后传送给控制模块;同时,将数据传送到控制模块,控制模块完成跨时钟域处理后,再将数据传送到DDR3控制器,进行写操作。在进行写操作时,将写地址进行覆盖寄存。当检测到切换信号的切换沿时,将寄存的最大写数据地址发送给读数据模块,读数据模块将此地址作为读数据最大地址。

当根据切换信号对DDR3进行读操作时,读数据模块把从写数据模块接收到的最大写地址作为最大读地址传送给控制模块,由控制模块处理后传送给DDR3控制器,以确保数据全部读出;读出的数据由控制模块处理后返回给读数据模块,供用户分析。通过这种读写方式,可以按需更改每次DDR3读写的数据量,增加了控制器系统的灵活性。

写数据模块的主要信号有app_cmd、app_addr、app_en、app_wdf_data、app_wdf_wren、app_rdy和app_wdf_rdy。app_cmd是操作命令信号,3′b000表示写入,3′b001表示读出;app_addr是操作地址;app_en是操作地址使能,只有当app_en为高电平的时候,对应的操作地址才是有效的;app_wdf_data是写入的数据接口;app_wdf_wren是写入数据的使能信号,只有当app_wdf_wren为高电平时,写入的数据才是有效的;app_rdy和app_wdf_rdy是DDR3 IP核反馈给控制模块的信号,当DDR3准备好接收写数据地址和写数据命令时,app_rdy为高电平,此时用户需置高app_en,发送的地址才是有效的;当DDR3准备好接收写数据时,app_wdf_rdy为高,此时用户需置高app_wdf_wren,发送给DDR3控制器的数据才是有效的。只要将地址系统和数据系统按照时序关系图对应,就可以将数据写入DDR3。

读数据模块的主要信号有app_cmd、app_addr、app_en、app_rdy、app_rd_data和app_rd_data_valid,读操作没有数据总线信号对应使能信号。其中:app_cmd、app_addr、app_en和app_rdy这4个信号的作用与写数据模块一样,分别是DDR3 IP核反馈给控制模块的读出数据和数据有效信号。当用户发送命令和地址后,每隔一段时间都将拉高读数据有效信号,同时传出读数据。

3 系统测试与分析

3.1 仿真分析

控制器生成以后,将代码加入到Vivado2015.1软件中,以进行控制器功能验证。代码中包含了一个测试模块,该模块能够随机地对DDR3进行一系列读写,并且能对比读写数据,以便验证控制器的正确性。仿真过程中,大约经过55.4 μs的仿真时间,init_calib_complete的值由0变为1,说明DDR3初始化已经成功。由于设计时将DDR3的突发长度设置为8,所以地址以8为单位进行增长。当用户给出一个地址,控制器就可以连续读取8个地址的数据。由于数据总线的宽度为64位,所以每次读写操作的位宽达到512位。该测试模块带有数据出错标志位tg_compare_error,可通过这个信号比较控制器读写是否一致。当有数据出错的时候,tg_compare_error的值为1。仿真结果表明,tg_compare_error信号的输出一直为0,说明没有数据出错,控制器的功能验证通过。

3.2 硬件测试

为了验证所设计的控制器能否工作,要对控制器进行FPGA板级的下板测试,以确保设计的可行性与可靠性。系统综合实现后,把bit文件加载到ZC706评估板上进行板级调试。为了便于分析,由Xilinx提供了FPGA片上调试工具[10],它可以捕获和显示实时信号,观察在系统设计中硬件和软件之间的相互作用。控制器将实时采集到的数据存储到FPGA片内的RAM中,并通过JTAG接口传送到软件中显示,使用非常方便。由于RAM容量和一次采样到的数据都有限,因此在硬件测试时,以循环读写的方式进行。DDR3工作的主时钟频率为800 MHz,数据传输速度达到1 600 MT/s。读写比较信号dbg_cmp_error输出始终为低电平,说明写入和读取的数据相同,控制器能够正常工作,由此完成硬件测试。

4 结束语

通过对DDR3技术特点和原理的分析,利用Xilinx公司提供的Vivado软件和MIG IP核,设计了DDR3控制器系统,并且在ZC706评估板上予以实现。通过仿真和下板测试,证明了该控制器能够稳定地对DDR3内存条进行读写。控制器的主时钟工作在800 MHz,数据传输速率达到1 600 MT/s,表明了设计的可行性和正确性,可以将其运用到自适应接收机中,对高速A/D采样数据进行高速缓存。通过IP核设计的DDR3控制器具有较好的适用性和灵活性,消耗逻辑资源较少,移植方便。以MIG IP核为基础进行系统开发,减少了系统的开发成本,同时也缩短了系统的开发时间。

[1] 李宪强.FPGA项目开发实战讲解[M].北京:电子工业出版社,2015:175-178.

[2] PAN G T,LUO L,OU G D,et al. Design and implementation of a DDR3-based memory controller[C]//2013 Third International Conference on Intelligent System Design and Engineering Applications,2013:540-543.

[3] JEDEC Organization. JEDEC Standard DDR3 SDRAM Specification[S].2010.

[4] 马志超.DDR3控制器的设计与验证[D].西安:西安电子科技大学,2013.

[5] 丁宁,马游春,秦丽,等.基于FPGA的DDR3-SDRAM控制器用户接口设计[J].科学技术与工程,2014,14(17):225-228.

[6] 张刚,贾建超,赵龙.基于FPGA的DDR3 SDRAM控制器设计与实现[J].电子科技,2014,27(1):70-73.

[7] 李晋文,胡军,曹跃胜,等.DDR3时序分析与设计[J].计算机科学,2012,39(4):293-296.

[8] 马其琪,鲍爱达.基于DDR3 SDRAM的高速大容量数据缓存设计[J].计算机测量与控制,2015,23(9):3112-3114.

[9] ZHOU R J,HAO Y Y,HU J S. Quick system-level DDR3 signal integrity simulation research[J].Journal of Electronic Science and Technology,2013,11(3):286-290.

[10]黄云翔.DDR3 SDRAM控制器的设计和验证[D].广州:华南理工大学,2012.

Design of DDR3-SDRAM Controller and FPGA Implementation

Aiming at the requirements of high bandwidth and large capacity for high-speed A/D sampling data in adaptive receiver,a design scheme of double data rate 3 (DDR3) controller is put forward. The design method of adding a user interface control program based on MIG IP core is adopted,and the controller is realized using ZC706 evaluation board. The design has better flexibility,high transplantability,and simple user interface,which can be flexibly applied into different projects. Through the simulation and board level test,the interfacing frequency of DDR3 can work at 800 MHz,and the transmission speed is up to 1 600 MT/s,which verifies the feasibility and correctness of the system,and will have a significant impact to solve the problem of massive data cache.

Memory Controller FPGA High bandwidth Large capacity User interface Data module Analog-digital conversion

国防基础科研计划基金资助项目(编号:B3120133002)。

李元兵(1991—),男,现为西南科技大学电子与通信工程专业在读硕士研究生;主要从事高速并行信号处理的研究。

TH7;TP332

A

10.16086/j.cnki.issn 1000-0380.201608002

修改稿收到日期:2016-05-05。