基于FPGA的IRIG-B编解码设计与实现

田 园,李大鹏,蒲 恺,李玉发

(中航工业计算所,西安 710119)

基于FPGA的IRIG-B编解码设计与实现

田 园,李大鹏,蒲 恺,李玉发

(中航工业计算所,西安 710119)

随着系统间时间同步要求的提高,IRIG-B码被越来越多的应用于系统间的时统模块中;针对传统的单片机及专用芯片实现方法已经不能满足产品的可靠性和可移植性的问题,对基于FPGA的IRIG-B编解码设计和实现方法进行了研究;提出了一种将BCD码和二进制码之间相互转换的迭代算法;结合FPGA设计方法对IRIG-B编码和解码方法进行了研究;通过对实验方法进行仿真,结果表明该方法能够正确有效的对时间信息进行IRIG-B格式的解码和编码,并且FPGA内部的实现形式可以大大减少外部芯片及电路的使用,从而大幅提升产品的可靠性和可移植性。

IRIG-B;FPGA;编码;解码

0 引言

伴随通信设备应用的发展,时间同步技术应用于越来越多的系统中,用于同步系统间不同设备或分系统的时间,例如信息分发系统、测控系统、定位系统。RIG时间序列码是一种常用于时间系统中的串行时间码,它是由美国靶场间仪器组(inter-range instrumentation group,简称IRIG)在1959年设计,特点是可靠性高、传输距离远、具有标准接口及使用方法灵活[1]。IRIG码有A、B、D、E、G、H六种,它们的区别是码流速率不同及所表示的时间信息不同,IRIG-B应用最为广泛[2]。目前,IRIG_B广泛应用于气象、通信、远程控制、测量等设备中,全球定位系统(global positioning system)的接收设备就是采用IRIG_B码作为标准。

现场可编程门阵列(FPGA)作为设计的核心,应用于目前大多数产品的设计中,往往一片FPGA就可以完成所有软硬件的功能。以往很多IRIG-B的设计都是基于单片机或专用解码芯片实现,使用不够灵活,且精度不高。需要一种能够融合到FPGA的IRIG-B设计方法,使得设计更加灵活、精度更高且易移植。

1 IRIG-B码原理

IRIG-B码有支流(DC)码和交流(AC)码两种存在形式。DC码是以脉冲宽度编码方式[3]。AC码是对DC码以1 kHz的正弦波进行幅度调制后形成的,用以适合远距离传送。本文对DC码进行研究。

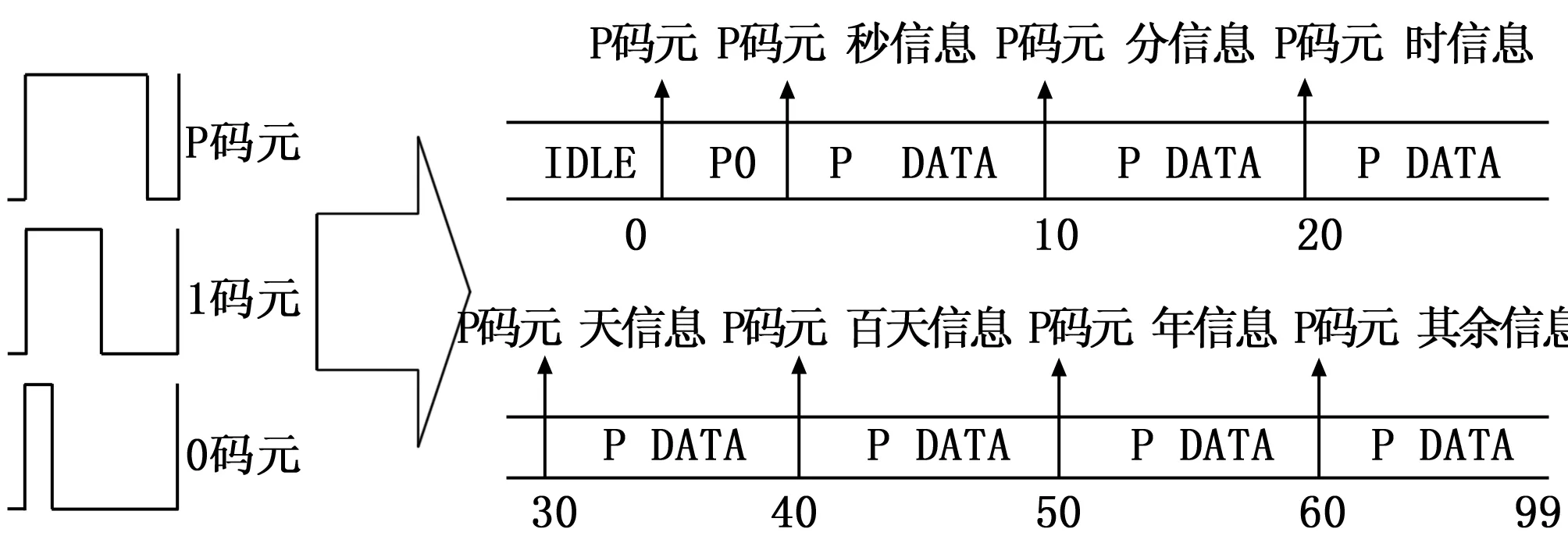

IRIG-B码格式示意图见图1。IRIG-B码有3种码元,分别为P码、1码和0码。每个码元占时10 ms,用高电平的时间来区分各种码元,P码、1码和0码分别对应的高电平时间为8 ms、5 ms和2 ms。P码是用于编解码时对码流进行定位,1码和0码分别对应逻辑“1”和逻辑“0”。每个B码是以连续的两个P码作为开始,第一个P码是位置码,第二个P码是秒脉冲(PPS),秒脉冲的上升沿是该B码的准时刻参考点(on-time reference point)。IRIG-B码为每秒一帧,每帧分为10个字段,每个字段10个码元,就是10个bit信息,共100个码元100位信息[4]。将100个码元按照0~99进行编码,则码元中时间信息的具体分布为:第0、9、19、29、39、49、59、69、79、89为10个位置P码,分别为P0~P9;P0和P1之间为“秒”时间区域;P1和P2之间为“分”时间区域;P2和P3之间为“时”时间区域;P3和P4之间为“天”时间区域;P4和P5之间为“百天”时间区域;P5和P6之间为“年”时间区域;P6和P8之间为控制信息区域;P8和下一个P0之间为TOD(Time Of Day)时间区域,TOD是指当前时刻是当天的第多少秒。P0~P8之间为BCD编码,最后的TOD时间为标准二进制编码。

图1 IRIG-B码示意图

2 IRIG-B码设计

传统的IRIG-B码编解码电路通常采用单片机的A/D接口结合外围电路实现[5]。现有使用单片机的通信设备很少,大部分设计中采用FPGA作为设计核心,所以可以将IRIG-B码单片机实现的全部工作合并进FPGA,使得设计更加紧凑、合理。

2.1 BCD码转换

IRIG-B码中除TOD信息是二进制编码外,其余时间信息都是使用BCD(Binary-Coded Decimal)码标准。BCD码也叫二/十进制码,含义是指二进制编码的十进制码。BCD码的每个十进制数字用一串单独的二进制比特来存储,较为常见的是4个比特位标识一个十进制数字,最终德BCD码对外表现形式为二进制,表达的是十进制数字。

年份的编码在IRIG标准和IRIG-B时间编码的文档中,进对年份的十位和个位进行编码。例如2015年,IRIG-B码的年份为15年。时间信息格式如15年200日12时30分40秒,需要转换为8421格式的BCD码才能为IRIG-B接收端接收。FPGA内部使用的编码方式是二进制,因此需要一种FPGA可实现的将二进制时间信息与BCD码相互转换的方法。

假设一二进制数为X,将其转换为8421格式的BCD码Y(初始值设为0)的过程如下:

1) 如果X>=80,则Y=Y&&1,且Y左移1位,X=X-80;

2) 如果X>=40,则Y=Y&&1,且Y左移1位,X=X-40;

3) 如果X>=20,则Y=Y&&1,且Y左移1位,X=X-20;

4) 如果X>=10,则Y=Y&&1,且Y左移1位,X=X-10;

5) 如果X>=8,则Y=Y&&1,且Y左移1位,X=X-8;

6) 如果X>=4,则Y=Y&&1,且Y左移1位,X=X-4;

7) 如果X>=2,则Y=Y&&1,且Y左移1位,X=X-2;

8) 如果X>=1,则Y=Y&&1,且Y左移1位,X=X-1。

BCD码转换Y为二进制数X的方法如下:

1) 如果Y[0]=1,则X=X+1,Y右移1位;

2) 如果Y[0]=1,则X=X+2,Y右移1位;

3) 如果Y[0]=1,则X=X+4,Y右移1位;

4) 如果Y[0]=1,则X=X+8,Y右移1位;

5) 如果Y[0]=1,则X=X+10,Y右移1位;

6) 如果Y[0]=1,则X=X+20,Y右移1位;

7) 如果Y[0]=1,则X=X+40,Y右移1位;

8) 如果Y[0]=1,则X=X+80,Y右移1位。

2.2 IRIG-B解码

IRIG-B解码的过程就是将一个IRIG-B码的波形解码为最终的时间信息,所以需要将B码的波形先转换为BCD码,再将BCD码转换为二进制码。

针对波形的解码是基于单独码元的解码。IRIG-B的码元占时均为10 ms,P码元、0码元和1码元分别占用高电平时间为8 ms、2 ms和5 ms。从以上描述可知,码元识别的最小分辨率为1 ms,因此检测一个码元必须以1 kHz或更快的时钟频率对IRIG-B的波形进行采集才能将P码元、0码元和1码元进行区分。设计中不需要采用外部输入源的方式进行时钟获取,可采用FPGA内部锁相环(PLL)将内部使用始终变换为可用频率的时钟。例如将25 MHz变换为1 MHz,再利用逻辑代码将1 MHz转换为1 kHz的时钟频率。设计中为提高码元的精确识别,使用1 MHz频率的时钟对IRIG-B进行码元采集。解码时对P码元、0码元和1码元的采集计数值分别为8 000、2 000和5 000。这样做的原因是如果时钟信号存在漂移,采用1 kHz的时钟频率采集计数时分别为8、2、5,如果始终存在漂移或因其他行为,很容易造成码元识别错误。针对时钟漂移的问题[6],采用1 MHz的时钟,可以采用范围鉴别的方法识别码元,例如9000~7000计数识别为P码元,1000~3000识别为0码元,4000~6000识别为1码元。

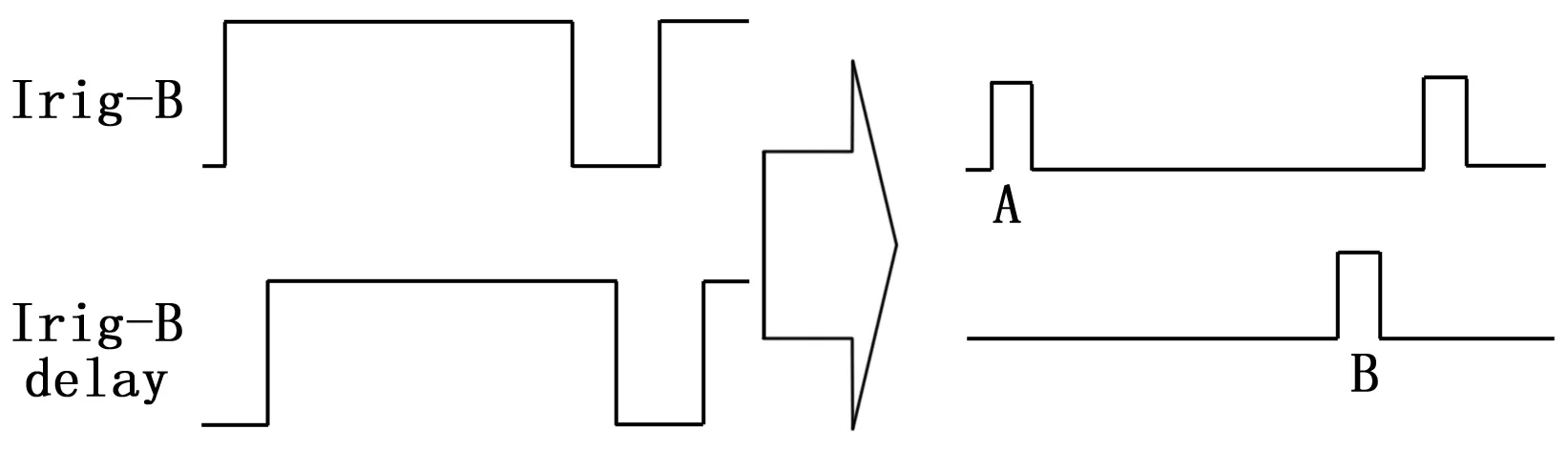

解码时首先从码元的识别开始,将IRIG-B码的波形使用1 MHz的时钟进行一个时钟周期的延迟,延迟后利用原波形与延迟后的波形(Irig-B-delay)产生新的A脉冲和B脉冲,如图2所示。A脉冲及B脉冲生成条件如下:

Pulse A = irig-b=’1’ and irig-b-delay=’0’

Pulse B = irig-b=’0’ and irig-b-delay=’1’

A脉冲表示B码中单个码元的开始,B脉冲表示B码单个码元高电平的结束。设置循环计数器从A脉冲开始计时至下一个脉冲值,使得计数在0到9999之间循环。每当检测到B脉冲的存在,记录下计数值为cnt,判断cnt是否为3种码元范围识别中的一种,如果是则可分别判断当前码元属于P码、1码或0码,若计数值不为8、5、2中的一种可认为码元无效。

图2 码元解码示意图

在单个码元提取的基础上可以实现对B码中时间信息的提取。连续出现2个pps秒脉冲则认为是一个B码完整帧的开始,因此需要先对两个连续的P码进行定位后,再对B码中其余码元表示的信息进行提取和解析。提取完两个P码后,后续的B码波形可分为10个类似的部分:第一部分代表秒时间段;第二部分代表分时间段;第三部分代表时时间段;第四部分代表天时间段;第五部分代表百天时间段;第六部分代表年时间段;后续代表控制字段和TOD字段。每个时间段占时100 ms,并且以P码开始。使用寄存器将B码中的BCD码保存下来。为了产生一个连续解码的效果,需要从解析到第一个P码开始计数,当计数到99时,加上之前解析的P码共100个码元占时1微秒代表一个完整IRIG-B帧解析完成。设计状态机如图3所示。各状态描述如下:

图3 解码状态机

IDLE状态:①检测到P码元进入P0状态,否则继续在IDLE状态等待P码元。

P0状态:②检测到1码元、0码元或不可识别的码元则进入IDLE状态;③检测到P码元进入P状态。

P状态:④检测到P码元继续处于P状态,⑤检测到1码元或0码元进入REV状态,⑥检测到不可识别码元进入IDLE状态继续等待帧头。

REV状态:⑦检测到1码元或0码元,且计数器小于99,继续处于DATA状态;⑧检测到P码元且计数值小于99,进入P状态;⑨检测到不可识别码元,或检测到1码元或0码元且计数值大于等于99,进入IDLE状态;⑩检测到P码元,且计数器大于等于99,则进入P0状态。

在REV状态中,依据当前B码码元数计数判断当前处于哪个信息的采集时间。若码元计数值小于10时,处入秒信息读取状态,若码元计数值小于20大于10时,处入分信息读取状态;若码元计数值小于30大于20时,处入时信息读取状态;若码元计数值小于40大于30时,处入天信息读取状态;若码元计数值小于50大于40时,处入百天信息读取状态;若码元计数值小于60大于50时,处入年信息读取状态。将收集到的BCD码格式的秒、分、时、天、百天、年信息存放于寄存器中,再使用3.1描述的方法转换为2进制格式即可用于上层软件直接调用。

2.3 IRIG-B编码

IRIG-B编码的过程类似于IRIG-B解码的逆过程,如图所示,先对时间信息进行检查,再将符合要求的时间信息进行二进制码到BCD码的转换,最终将BCD码发出。

时间信息的检查主要目的是通过检查时间信息的数据是否合理性,滤除不合理的时间,避免接收端收到错误的时间信息。时间信息使用寄存器格式存放,在初始是二进制码格式的。检查时间信息是否合理主要是检查年信息是否超过99,日信息是否超过356,时信息是否超过24,分信息和秒信息是否超过60。如果存在上述任意一种情况则该时间数据就不合理,不能发送。将合理的二进制时间信息同过3.1中所述的迭代方式,变化为8421BCD码存放于6个8位寄存器中。与解码类似,第一个代表秒时间段,第二个代表分时间段,第3个代表时时间段,第4个代表天时间段,第5个代表百天时间段,第6个代表年时间段。

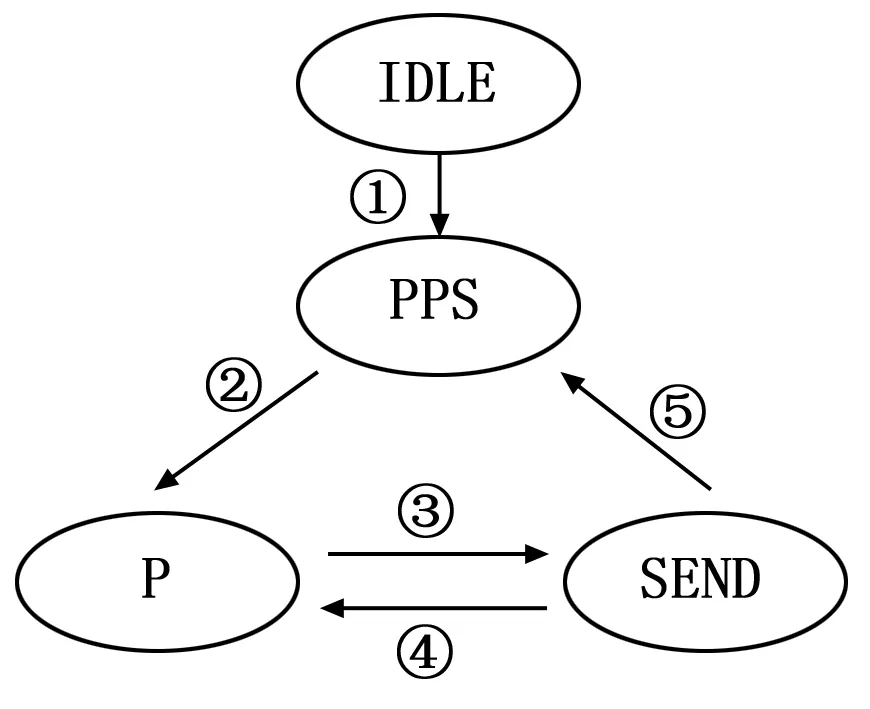

设计状态机对时间信息进行发送,见图4。对P码元、1码元和0码元的发送采用1 kHz进行0-9的循环小计数发送,控制输出电平的高低。采用一个0-99的大循环计数控制状态的迁移,计数从PPS状态开始,各状态描述如下。

IDLE状态:①发送P码元进入PPS状态。

PPS状态:②发送P码元进入P状态,设置计数值为0。

P状态:③发送P码元,进入SEND状态,计数值增1。

图4 编码状态机

DATA状态:当计数值小于10时,依次对秒信息各位进行发送;当计数值小于20大于10时,依次对分信息各位进行发送;当计数值小于30大于20时,依次对时信息各位进行发送;当计数值小于40大于30时,依次对天信息各位进行发送;当计数值小于50大于40时,依次对百天信息各位进行发送;当计数值小于60大于50时,依次对年信息各位进行发送。④当计数为9、19、29、39、49、59、69、79、89时进入P状态,⑤当计数为99进入PPS状态。

3 仿真验证

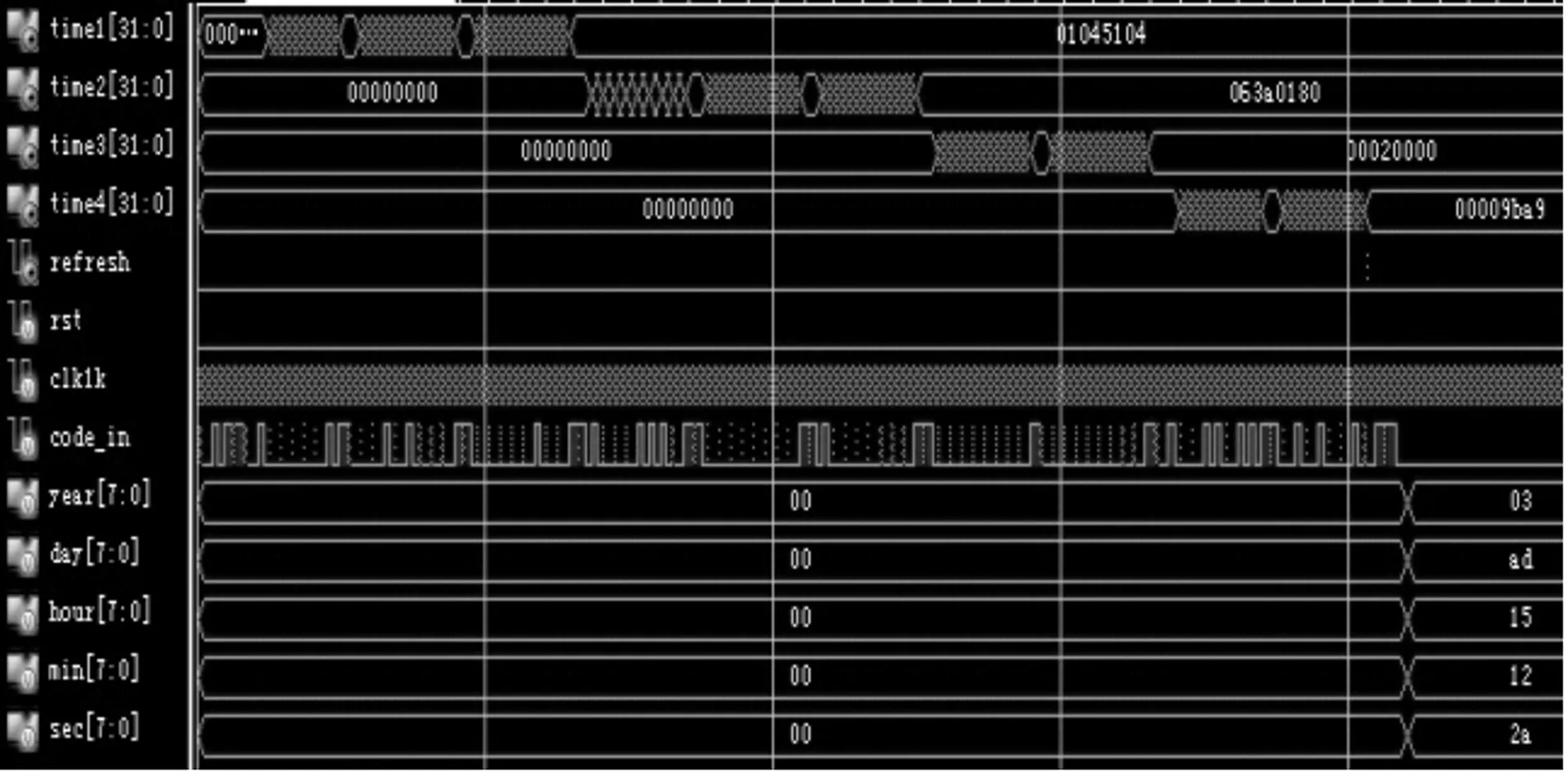

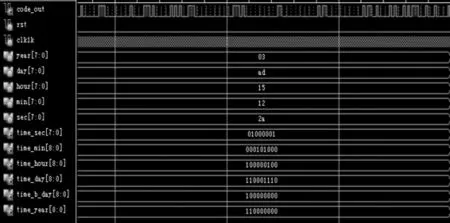

采用xilinx的FPGA进行功能验证。使用verilog进行编码,仿真结果见图5和图6。图中cycle为每个信息段的0-9计数,big_cnt为每个B码帧的0-99计数,year、day、hour、min、sec分别代表二进制格式的年、天、时、分、秒。图5中code_in为外界输入B码,time1、time2、time3、time4为保存B码的8421BCD格式码的寄存器。图6中time_sec、time_min、time_day、time_bday、time_year分别代表秒、分、时、天、百天、年的BCD格式码,code_out为B码输出。仿真结果表明,该方法能够正确有效的对IRIG-B码进行解码和编码,并可正确的进行时间信息的二进制码格式与BCD格式码相互转换。

图5 解码过程仿真图

图6 编码过程仿真图

4 结论

本文通过对IRIG-B码原理进行分析,基于FPGA提出了一种基于二进制与BCD码相互转换,结合内部状态机进行IRIG-B码编码和解码的方法,并采用xilinx的FPGA进行了仿真验证。仿真结果表明,该方法能够满足基于正确有效的对该时间码进行解码和编码,并且FPGA内部的实现形式可以大大减少外部编解码芯片电路的使用,从而大幅提升产品可靠性。

[1] 郭 彬,单庆晓,肖昌炎,等.电网时钟系统的北斗/GPS双模同步技术研究[J].计算机测量与控制,2011,19(1):139-141.

[2] 张 斌,张东来,王 超.基于FPGA的IRIG-B(DC)码同步解码设计[J].测控技术,2008,27(2):45-47.

[3] Telecommunications and Timing Group Irig Standard 200-98[S].Secretariat Range Commanders Council,1998

[4] 熊立智,唐普英.基于FPGA的IRIG-B解码电路设计与实现[J].通信技术,2010,43(8):231-235.

[5] 佟 刚,崔 明,曹永刚,等.MSP430F149在IRIG-B码解码中的应用[J].计算机测量与控制,2007,15(11):1597-1610.

[6] 任 宏,王志林,罗纯哲.时统对时精度测量设备的设计与研究[J].电子技术应用,2009,10:127-130.

Design and Implementation of IRIG-B Encoding and Decoding Based on FPGA

Tian Yuan, Li Dapeng, Pu Kai,Li Yufa

(China aeronautical Computing Technique Research Institute, Xi’an 710119,China)

With the increase of the time synchronization requirements of the system, the IRIG-B code is used more and more in the time system module; in view of the traditional single chip microcomputer and special chip implementation method cannot meet the reliability and portability of the product, the design and implementation of FPGA based on IRIG-B is studied;a new iterative algorithm is presented for converting between BCD codes and binary codes; research on IRIG-B encoding and decoding method based on FPGA design method; through simulation experiments, the results show that the proposed method can correct the time information of IRIG-B format decoding and encoding, and the implementation of FPGA can greatly reduce the use of external chips and circuits, thus greatly improving the reliability and portability of the products.

IRIG-B; FPGA; code; decode

2015-09-15;

2015-10-30。

田 园(1985-),男,陕西富平人,工程师,硕士,主要从事机载网络技术方向的研究。

1671-4598(2016)03-0218-03

10.16526/j.cnki.11-4762/tp.2016.03.059

TP15

A