NMOS管交叉耦合的能量回收电路设计

师建英,许衍彬,刘磊,门晋喜

(1.河北大学电子信息工程学院,河北保定 071002;2.河北科技学院机电系,河北保定 071000;3.95866部队无线电导航教研室,河北保定 071051)

NMOS管交叉耦合的能量回收电路设计

师建英1,许衍彬2,刘磊1,门晋喜3

(1.河北大学电子信息工程学院,河北保定071002;2.河北科技学院机电系,河北保定071000;3.95866部队无线电导航教研室,河北保定071051)

对NMOS(N-metaloxidesemiconductor)管交叉耦合逻辑(NMOS-transistorcrosscouplinglogic,NCCL)的能量回收电路进行了研究,PMOS(P-metaloxidesemiconductor)管作为输入管来降低纳米CMOS工艺中栅氧化层上的漏电流以减小功耗;在此基础上实现了绝热JK触发器电路.在90nmCMOSBSIM3工艺模型下,用HSPICE对NCCL反相器及其JK触发器进行了模拟分析,结果表明NCCL反相器的工作频率可达到1GHz;与ECRL(efficientchargerecoverylogic)反相器相比,当负载电容、时钟频率和电源电压中某一参数变化时,NCCL的功耗都出现不同程度的降低;在相同的工作条件下NCCLJK触发器的功耗约为ECRL的50%.

NMOS管交叉耦合;NCCL;NCCLJK触发器;低功耗

自从CMOS器件工艺进入纳米尺寸之后,功耗问题已经成为了特别重要的问题[1].从电路角度考虑,典型的降低功耗的方法是器件尺寸的减小、互连线的优化、栅极时钟结构、多电源技术和动态控制供电电源等[2].然而随着人们对便携式电脑、无线传感器和生物医学电子设备需求的增加,传统的低功耗设计技术已经无法满足这些应用中进一步降低电路功耗的要求,能量回收电路采用交变电压作为供电电压可以有效地降低电路的功耗.Moon等[3]提出的ECRL电路采用交叉耦合的PMOS管来存储电路的能量,结合交变电源电压实现能量的回收,但PMOS传输门自身的缺陷造成输出端的低电平不能为零,且电路中存在非绝热损失(与PMOS管的阈值电压有关);文献[4-6]所提出的电路都是对ECRL电路的改进,它们通过增加不同的能量回收路径来实现能量的完全回收,但是能量回收路径的增加,必然要增加新的MOS管,这些MOS管必然会增加新的功耗,从而部分抵消了能量回收的效果.文献[7]中报道的在纳米氧化栅CMOS工艺下PMOS管的漏电流比NMOS管的漏电流小1个数量级的结论可以用来进一步地降低电路的功耗;文献[8]中采用将地电平变换成电源电压的方法来降低电路的功耗.基于以上种种分析方法,在ECRL电路结构的基础上提出了1种采用NMOS管交叉耦合的能量回收电路.在90nmCMOSBSIM3工艺[9]下,HSPICE模拟得到,在不同的工作条件下与ECRL电路相比,NCCL反相器和JK触发器电路的功耗都得到了显著的降低.

1 NCCL的电路结构

1.1NCCL反相器

由于MOS管的栅漏电流随着栅氧化层厚度的减小成指数增长关系,在亚100nm工艺下,栅漏电流将成为MOS管关断电流的主要组成部分[10-11].在相同偏压、相同尺寸下,PMOS管的栅漏电流比NMOS管的栅漏电流小了一个数量级.这是因为NMOS管的栅漏电流主要是由导带中的电子隧穿引起的,PMOS管的栅漏电流主要是由价带中的空穴隧穿引起的,而空穴隧穿的势垒高度(4.5eV)大于电子隧穿的势垒高度(3.1eV),这是导致PMOS管的栅漏电流较小的原因[7],因此用PMOS做输入管可以有效地降低电路的功耗.

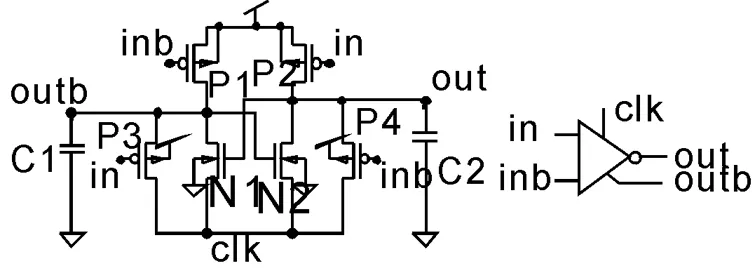

图1 NCCL反相器的电路图和符号Fig.1 NCCL circuit and the logic symbol

在绝热电路中,如果选用PMOS管来作为输入管,则应该选用NMOS管来作为交叉耦合存储管,其供电电压也要做相应的变化.采用PMOS管输入级和直流供电电压的NCCL反相器的电路及其逻辑符号见图1.与ECRL电路相同,NCCL电路仍然属于双轨逻辑绝热电路,它主要由2部分组成:输入模块和能量存储回收模块.

图2 NCCL反相器的级联形式和四相功率时钟Fig.2 Cascade form and four phase power clock of NCCL inverter

图1中P1和P2管是输入管,N1和N2管构成交叉耦合的能量存储结构,P3和P4管与N1及N2管分别构成CMOS传输门以实现能量的完全传输和回收,C1和C2为负载电容.输入信号的高电平值、时钟信号的高电平值以及电源电压值都是Vdd.NCCL电路采用四相功率时钟,其反相器链和功率时钟结构见图2,它的工作过程可以分为4个阶段:预充、保持、回收和等待.

图3 NCCL反相器的输入输出波形Fig.3 Waveform of NCCL inventor

图1中inb是in的反向信号,这里以in为“1”、inb为“0”为例对NCCL反相器电路的工作原理进行分析.在预充阶段(clk由地电平变化到高电平Vdd),P2和P3截止,P1和P4导通,outb为高电平Vdd.此时N2导通,N2和P4构成CMOS传输门使out端随时钟clk上升而上升;在保持阶段(clk保持高电平Vdd不变),out端保持Vdd电压不变;在回收阶段(clk由Vdd下降到地电平),out端上的能量又通过N2和P4构成的传输门完全回收至clk;在等待阶段(clk保持地电平不变),电路进入等待状态,等待下一个时钟周期的到来.

在Vdd为1.1V,功率时钟clk的周期为8ns(时钟频率为125MHz),负载电容都为1fF的条件下,用HSPICE工具,采用90nmPTM(predictivetechnologymodel)模型参数对NCCL反相器进行了模拟仿真,其输出波形见图3.由图3可知,输出端的电压变化情况与理论分析相同.

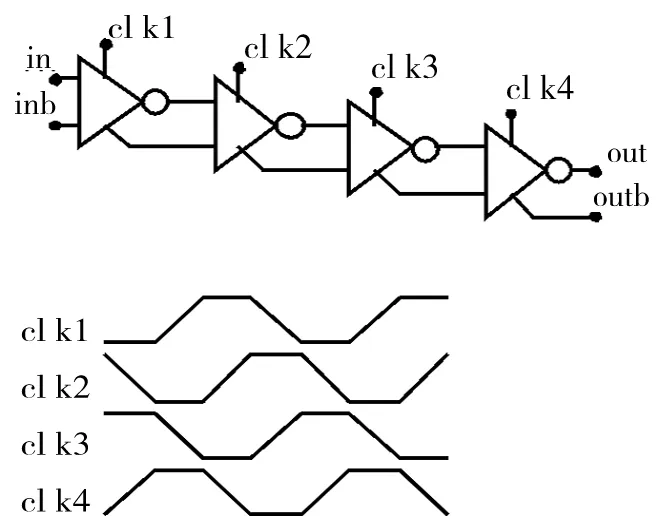

1.2NCCL JK触发器

JK触发器是数字时序逻辑中的重要结构单元.由1.1节分析可知,NCCL反相器电路的高电平输出为Vdd,地电平输出随时钟信号变化而变化;而ECRL电路的输出地电平为零,高电平随时钟信号变化而变化,这是NCCL电路与ECRL电路工作原理的不同之处.由NCCL电路构成的JK触发器的高电平和地电平输出情况与NCCL反相器电路相同,其电路结构如图4所示.

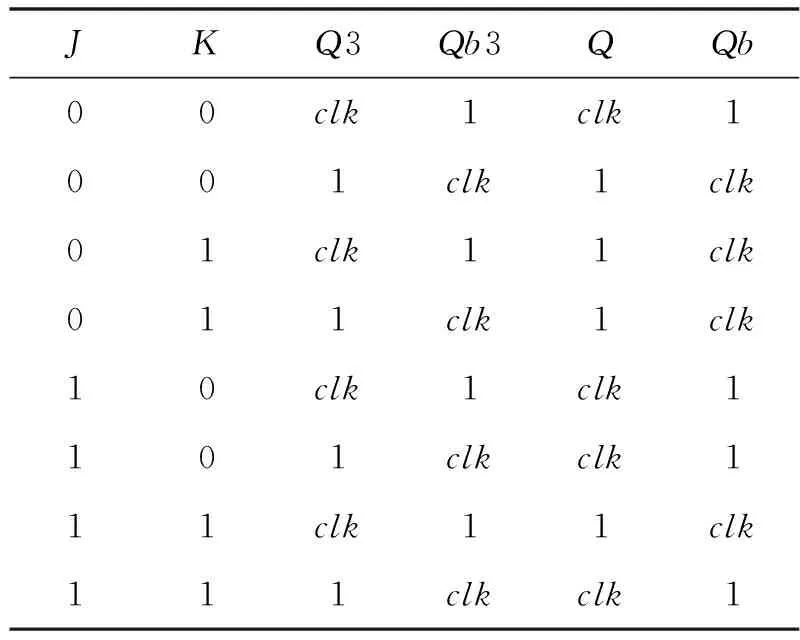

图4中Jb和Kb分别为J和K的反向信号;Q和Qb端的信号延时通过NCCL反相器链实现;Q3和Qb3为输出信号Q和Qb的前一个状态,并反馈到JK触发器中.此外,NCCL电路的输入管与电源电压Vdd之间有通路,而与地电平之间没有直接通路,这是与传统CMOSJK触发器和ECRLJK触发器之间的不同之处,其真值表见表1,表1中的‘clk’表示该端信号随时钟信号变化而变化.

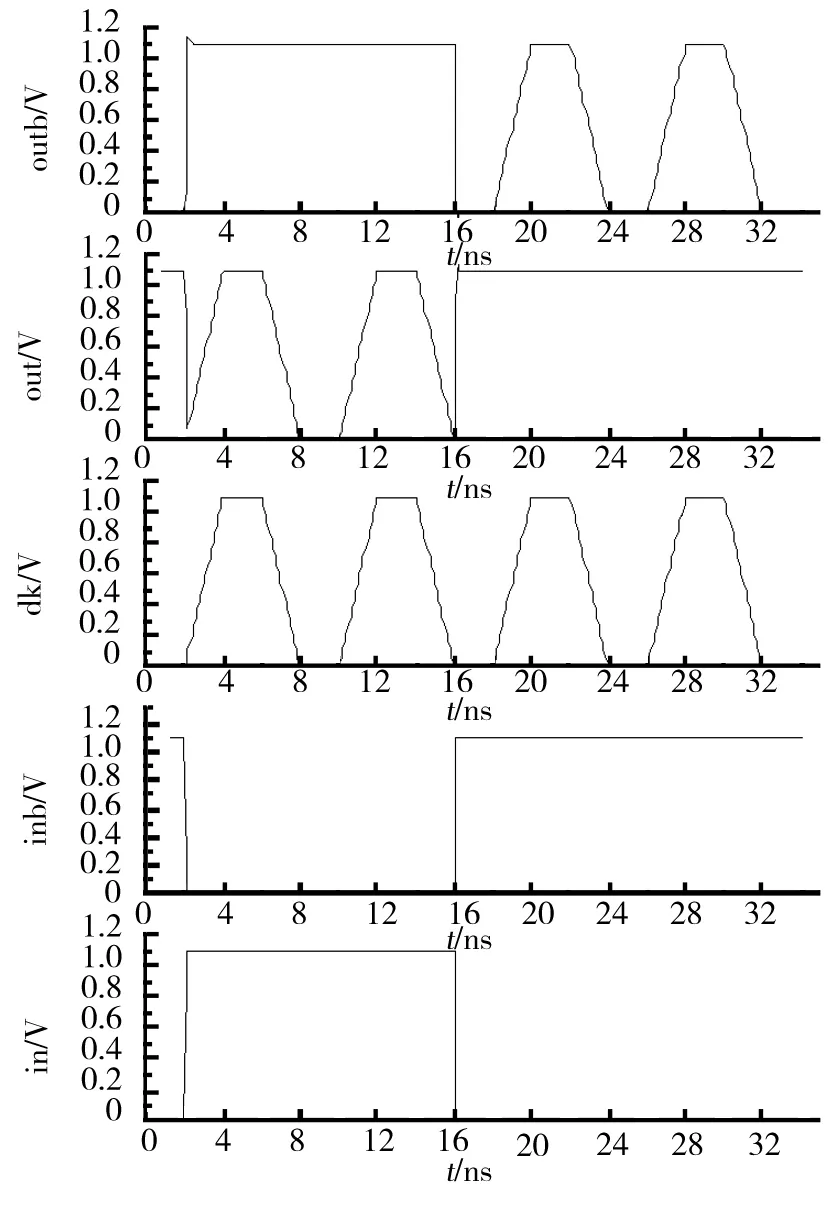

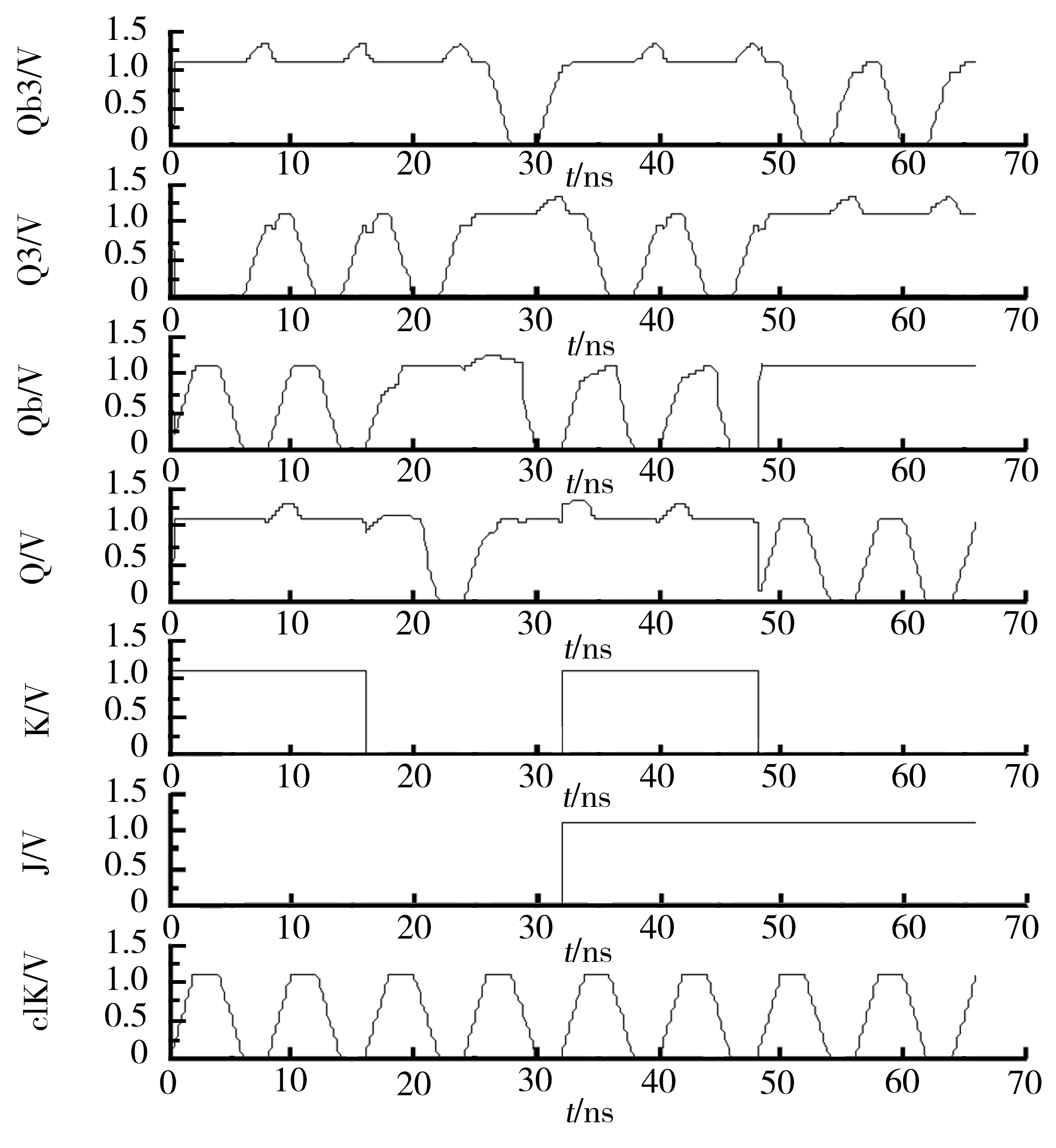

在Vdd为1.1V,时钟信号周期为8ns,负载电容为1fF的条件下,NCCLJK触发器的仿真波形见图5,其模拟结果与真值表的理论分析结果相同,需要注意的是当触发器在保持和翻转态时,Q和Qb的输出与Q3和Qb3的状态密切相关.

图4 NCCL JK触发器电路Fig.4 NCCL JK flip-flop

图5 NCCL JK触发器的输入输出波形Fig.5 Waveform of NCCL JK flip-flop

2 模拟结果分析

理论分析上,虽然NCCL电路中增加了直流供电电源,但是直流电源所引起的功耗与交变时钟信号相比很小,且它几乎不随外界条件变化;另外由于PMOS管的栅漏电流比NMOS的栅漏电流小了1个数量级,导致了由漏电流所引起的功耗也小了1个数量级,因此NCCL电路的功耗将小于ECRL电路的功耗.

2.1NCCL反相器与ECRL反相器的功耗比较

2.1.1负载电容变化

表1 NCCL JK触发器的真值表Tab.1 Truth table of NCCL JK flip-flop

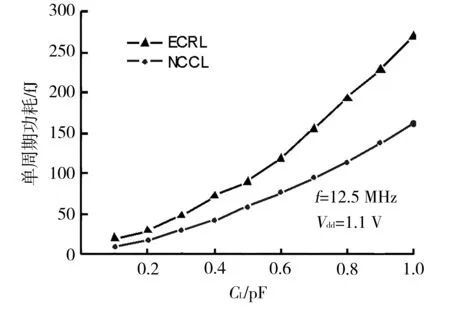

在频率为12.5MHz,Vdd为1.1V,负载电容从0.1pF变化到1pF的条件下,对NCCL和ECRL电路的功耗进行了模拟仿真,其结果见图6.模拟结果显示单个时钟周期内2种电路的功耗都随负载电容的增加而增加;在相同条件下,NCCL反相器的功耗约为ECRL反相器功耗的60%,这与理论分析相同.

2.1.2时钟频率变化

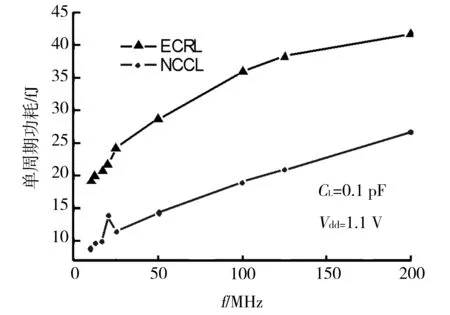

在Vdd为1.1V,负载电容为0.1pF,时钟频率从10MHz变化到200MHz的条件下,单个时钟周期内NCCL和ECRL反相器电路的功耗变化情况见图7.由图7可知,功耗随频率变化的曲线相对缓慢,在相同的工作条件下与ECRL电路相比,NCCL反相器的功耗大约降低了50%.

图6 负载电容变化时ECRL和NCCL反相器的功耗Fig.6 Power consumption of ECRL and NCCL inventor When load capacitance change

图7 时钟频率变化时ECRL和NCCL反相器的功耗Fig.7 Power consumption of ECRL and NCCL inventor when clock frequency change

2.1.3电源电压变化

负载电容为0.2pF,时钟频率分别为20、50和100MHz,电源电压从1V变化到1.5V的条件下,单个时钟周期内NCCL和ECRL反相器电路的功耗仿真结果见表2.由表2可知,ECRL和NCCL的功耗都随着电源电压的增加而增加,不同的是ECRL电路的功耗增加幅度明显大于NCCL电路的功耗增加幅度,或者说PMOS输入管有效地降低了电路的功耗.

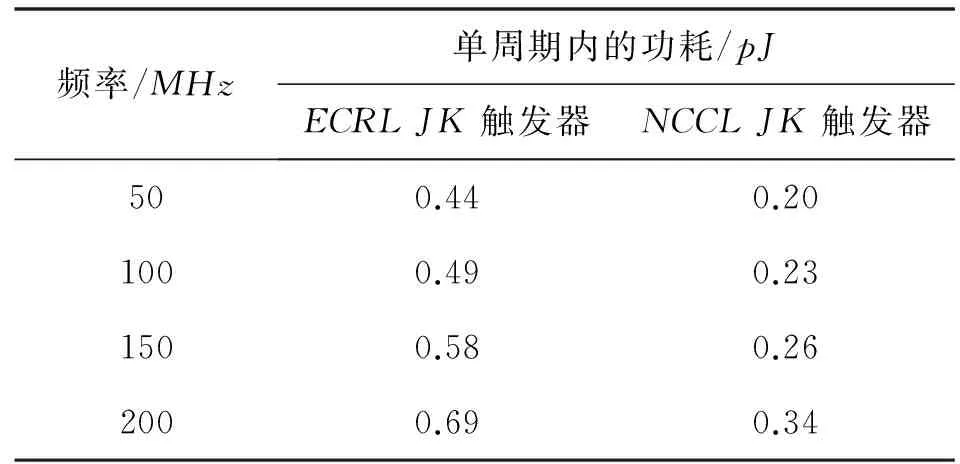

2.2NCCL和ECRL JK触发器的功耗比较

在负载电容为0.1pF,电源电压为1.1V的条件下,当时钟频率变化时,单个时钟周期内NCCL和ECRLJK触发器的总功耗见表3.由表3可知NCCLJK触发器比ECRLJK触发器节省了约50%的功耗.可见改进后电路的功耗得到了明显的降低,为更复杂的绝热逻辑电路的设计提供了设计思路和理论依据.

表2 不同频率下电源电压变化时所引起的功耗变化Tab.2 Power consumption when supply voltagechanges at different clk frequencies

表3 NCCL和ECRL JK触发器的功耗比较Tab.3 Power consumption of NCCLand ECRL JK flip-flops

3 结论

介绍了NMOS管交叉耦合的能量回收逻辑电路以及由其构成的JK触发器电路,分析了基本反相器电路和JK触发器电路的工作原理,阐述了NCCL电路与ECRL电路工作原理上的区别.在90nmBSIM3CMOS工艺下,用HSPICE软件仿真得到,在不同的参数变化条件下NCCL反相器的功耗约为ECRL反相器功耗的50%;与ECRLJK触发器相比,NCCLJK触发器的功耗也得到了显著的下降.

[1]MARKOVICD,WANGCC,ALARCONLP,etal.Ultralow-powerdesigninnear-thresholdregion[J].ProceedingsoftheIEEE,2010,98(2):237-252.DOI:10.1109/JPROC.2009.2035453.

[2]PAULBC,AGARWALA,ROYK.Low-powerdesigntechniquesforscaledtechnologies[J].Integration,theVLSIJournal,2006,39(2):64-89.DOI:10.1016/j.vlsi.2005.12.001.

[3]MOONY,JEONGDK.Anefficientchargerecoverylogiccircuit[J].IEEEJournalofSolid-stateCircuits,1996,31(4):514-522.

[4]郭宝增,张亚朋.基于改进型ECRL电路的触发器设计[J].微型机与应用,2010(2):23-26.GUOBaozeng,ZHANGYapeng.ImprovedECRL-basedflip-flopdesign[J].Microcomputer&ItsApplications,2010(2):23-26.

[5]张丽,郭宝增.基于ECRL电路的两种改进绝热电路[J].微型机与应用,2011,30(16):19-21.

ZHANGLi,GUOBaozeng.TwoimprovedadiabaticcircuitsbasedonECRL[J].Microcomputer&ItsApplications,2011,30(16):19-21.

[6]SHIJY,LIHY,XUYB.Designoftheapprovedlowpowerenergyrecoverylogiccircuit[J].AdvancedMaterialsResearch,2013,662:851-855.DOI:10.4028/www.scientific.net/AMR.662.851.

[7]YEOYC,LUQiang.Directtunnelinggateleakagecurrentintransistorswithultrathinsiliconnitridegatedielectric[J].IEEEElectronDeviceLetters,2000,21(11):540-542.DOI:10.1109/55.877204.

[8]HUJianping,LIUBinbin.Designsof2P-2P2Nenergyrecoverylogiccircuits[J].ResearchJournalofAppliedSciences,EngineeringandTechnology,2013,5(21):4977-4982.

[9]NanoscaleIntegrationandModelingGralpatASUPredictiveTechnologyModel(PTM)[S/OL].(2001-5-31)[2014-6-20].http://www.ptm.asu.edu.

[10]INUKAIT,TAKAMIYAM,NOSEK,etal.BoostedgateMOS(BGMOS):leakage-freecircuitsbydevice/circuitcooperationscheme[J].IntegratedCircuitsandDevices,2000,100(270):1-8.

[11]GHANIT,MISTRYK,PACKANS,etal.Scalingchallengesanddevicedesignrequirementsforhighperformancesub-50nmgatelengthplanarCMOStransistors[Z].SymposiumonVLSITechnology,Hawaii:2000.

(责任编辑:王兰英)

EnergyrecoverycircuitbasedonNMOStransistorcrosscouplinglogic

SHIJianying1,XUYanbin2,LIULei1,MENJinxi3

(1.ElectronicInformationEngineeringCollege,HebeiUniversity,Baoding071002,China;2.DepartmentofElectricalEngineering,HebeiCollegeofScienceandTechnology,Baoding071000,China;3.DepartmentofRadioNavigation,95866PLATroops,Baoding071051,China)

TheenergyrecoverycircuitbasedonNMOS(N-MetalOxideSemiconductor)-transistorcrosscouplinglogic(NCCL)isstudied.PMOS(P-MetalOxideSemiconductor)transistorsareusedastheinputtubetoreducetheleakagecurrentontheoxidegatelayerinnanometerCMOSprocess.NCCLJKflip-flopisconstructedbythesetechniques.ThecircuitsaresimulatedbyHSPICEin90nmCMOSBSIM3process,andthesimulationresultsshowthatNCCLinventor’soperationfrequencycanreachto1GHz.ComparedwiththeECRL(EfficientChargeRecoveryLogic)inventor,whenloadcapacityorclockfrequencyorpowersupplychanges,thepowerconsumptionsofNCCLinventordeclinetodifferentdegrees.Inthesameoperatecondition,thepowerconsumptionofNCCLJKflip-flopisabout50%oftheECRLJKflip-flop.

NMOStransistorcrosscoupling;NCCL;NCCLJKflip-flop;lowpowerconsumption

10.3969/j.issn.1000-1565.2016.03.017

2015-01-22

国家杰出青年基金资助项目(61204079); 河北省自然科学基金资助项目(F2013201196);保定市科学技术研究与发展指导计划项目(14GZ036);河北省科技计划自筹经费项目(15210409)

师建英 (1979-),女,河北邯郸人,河北大学讲师,主要从事集成电路的设计及其性能研究.

E-mail:hdsjy@126.com

TN

A