基于Nios Ⅱ的SOPC实验教学平台设计

陈晓静,吴爱平

(长江大学电子信息学院,湖北 荆州 434023)

基于Nios Ⅱ的SOPC实验教学平台设计

陈晓静,吴爱平

(长江大学电子信息学院,湖北 荆州 434023)

提出了以EP4CE30F248N FPGA为核心的SOPC实验教学平台设计方案,介绍了平台的硬件组成和软件开发工具,以定时中断为实验案例介绍了SOPC实验的具体流程。该平台由核心板、底板和扩展板组成,可实现的实验项目包括基本模块实验和创新型实验。其中基本模块实验类似于单片机实验,如定时器、键盘、数码管显示模块等,目的是帮助学生理解SOPC系统基本设计方法;创新型实验项目是将FPGA并行数据处理和Nios Ⅱ处理器灵活控制功能相结合的实验,如多通道数据采集、高精度频率计、频谱仪设计等,旨在帮助学生进一步掌握SOPC系统设计的精髓。该方案既能实现SOPC系统基本模块的实验,又能为电子设计竞赛和实际项目开发提供创新性平台,有助于培养学生的SOPC综合设计能力。

SOPC;Nios Ⅱ;FPGA;实验教学平台

SOPC(System On a Programmable Chip)即片上可编程系统,该技术使用FPGA(Field Programmable Gate Array)的逻辑单元以及植入FPGA内部的软核处理器、存储模块和DSP模块,设计出可裁剪、可扩充、可升级的嵌入式处理系统[1]。该系统不仅具有可编程系统的的灵活性,而且具有高速并行处理数据的能力。近年来,SOPC技术在数据采集、目标跟踪、电能质量监测等领域得到了广泛的应用[2~4]。

SOPC系统中的处理器通常有硬核和软核2种:硬核是指嵌入在可编程芯片内部的具有固定掩模版图的处理器内核,如ARM内核;软核是指以硬件描述语言文件的形式存在,需经过编译下载,最终固化到可编程芯片内部才可使用的处理器内核,如Altera公司推出的Nios Ⅱ嵌入式软核。虽然硬核的处理性能更高,但由于用户需支付额外的知识产权的费用,其推广应用受到限制。相比之下,Nios Ⅱ软核由Altera公司免费提供,用户只使用很少的逻辑资源就可获得一个功能强大的处理器,因此基于Nios Ⅱ软核的SOPC系统设计具有较大的实际应用价值。

近年来,为了使教学实验跟上高新技术发展的步伐,许多高校已经把SOPC技术引入到了教学实验中。文献[5]提出了基于Nios Ⅱ的SOPC实验平台的构建方法,在该平台上可以实现SOPC系统的基本模块实验比如PIO、定时器、中断等,但是由于FPGA芯片和外围设备被装配到同一块电路板上,系统检修和升级都不方便。文献[6]提出了EDA、单片机以及SOPC一体化实验的模式,硬件平台由FPGA核心板和功能底板组成,具有扩展灵活、升级方便的优点。但该实验平台主要是基于8051单片机IP(Intellectual Property)软核实现的,因此该实验系统本质上仍然是单片机实验,而不是SOPC系统实验,也没有利用到Nios Ⅱ软核的处理优势。为此,笔者设计了一种基于Nios Ⅱ软核的新型实验教学平台设计方法。

1 平台的硬件设计

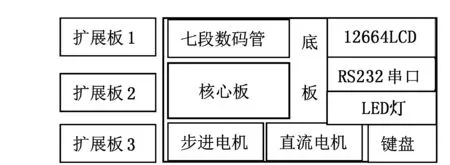

图1 SOPC实验教学平台的设计框图

根据易扩展、易升级的原则,SOPC实验教学平台由核心板、底板和扩展板3部分组成。其中核心板是一个FPGA最小系统,主要包括EP4CE30F248N FPGA芯片、64Mbit的EPCS64配置芯片、4Mbit SRAM存储器、256MbitSDRAM存储器、128MbitCFI FLASH存储器、主动编程AS接口、在系统编程JTAG接口;底板设计能够满足基本SOPC实验模块的实现,主要包括键盘、LED灯、七段数码管、12864LCD显示、RS232串口、步进电机驱动、直流电机驱动;扩展板是为扩展底板的功能使其满足某些创新型实验而设计,包括多通道数据采集板(板1)、多通道数模转换板(板2)、USB2.0扩展板(板3)。该平台的设计框图如图1所示,能够实现的实验项目及其硬件配置如表1所示。

2 实验项目设计流程

表1 实验项目及硬件配置

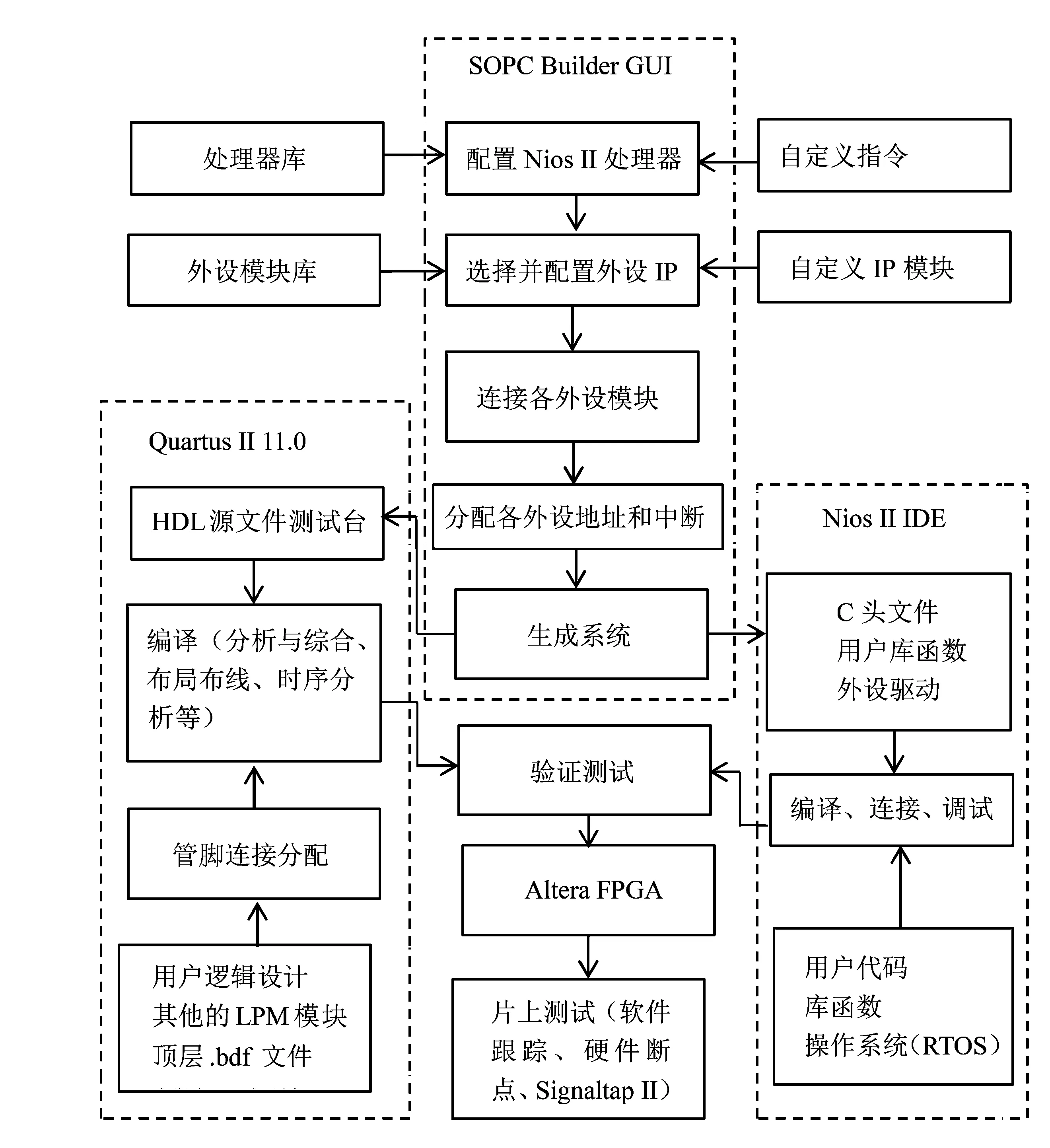

在上述硬件平台上,可以完成表1的每个实验项目的SOPC设计。不同于传统的嵌入式系统设计方式,SOPC系统是硬件和软件的协同设计,遵循如图2所示的流程。硬件设计使用Quartus Ⅱ 11.0和SOPC Builder软件,其中SOPC Buider可以通过Quartus Ⅱ中子菜单项启动。Quartus Ⅱ可完成基于Nios Ⅱ软核处理器的嵌入式系统的综合、优化、适配、下载和调试等,SOPC Builder可完成Nios Ⅱ系统的配置和生成,允许设计者在很短时间内创建高度定制的可编程片上系统。软件开发在Nios Ⅱ IDE集成开发环境中进行,该环境提供易用的图形用户界面和GCC编译器,并能根据Nios Ⅱ的硬件配置自动生成硬件抽象层HAL(Hardware Abstraction Layer)以提供底层硬件访问的驱动程序,并提供实时操作系统和TCP/IP协议栈的支持。从图2中还可以看出,SOPC设计与FPGA设计的区别在于多了对软核处理器和外设IP模块的配置步骤,体现了SOPC设计的可裁剪和可配置特性。

图2 SOPC设计流程

实验项目设计中一个关键的环节是外设IP模块的选择和配置。Nios Ⅱ系统的外设可以分为标准外设和自定义外设。标准外设是由Altera公司所提供的一系列免费使用的外设IP,也是其他微控制器系统中通常会用到的外设,如定时器、串行通信接口、通用I/O口等。自定义外设是指当标准外设不能满足用户的需求时,用户使用可编程逻辑资源自己定义外设集成到Nios Ⅱ系统之中。笔者所提出的实验项目中基本实验项目可以选择标准外设来设计,如流水灯实验可以选择PIO内核,定时器中断使用定时器内核,而创新型实验项目中没有现成的外设模块可以使用,因此需要用户自定义相应外设,如多通道数据采集和传输实验可以通过设计具有FIFO(First Input First Output,先进先出)存储结构和Avalon总线接口的外设模块实现,多通道任意波形发生器实验需要具有多路波形数字量的输出和锁存功能的外设模块。自定义外设IP设计是SOPC设计的难点,要求学生具有逻辑设计和接口设计的基础。

3 实验项目实例

为具体说明SOPC实验设计流程,笔者介绍一个具体的实验项目实例——定时器中断实验。该实验要求每定时1s,LED灯状态发生反转。

1)首先利用Quartus Ⅱ软件建立一个新的工程以及顶层.bdf文件。顶层文件用于描述Nios Ⅱ系统和LPM模块(Library of Parameterized Modules,参数化模块库)、用户逻辑设计模块之间的连接关系。

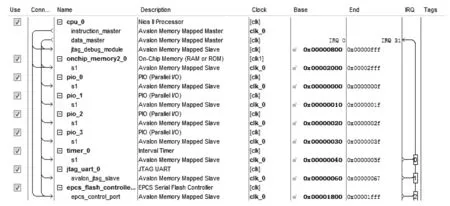

2)启动SOPC Builder构建一个Nios Ⅱ系统。从组件库中选取如下组件:1个Nios Ⅱ处理器、1个片上RAM存储器、4个PIO内核,1个定时器组件、1个在系统编程JTAG组件、1个EPCS控制器组件,各组件在SOPC Builder中互联情况如图3所示。组件加入后需对其属性进行配置,如Nios Ⅱ处理器选型和复位地址、异常地址的设置,RAM存储器的容量和数据位宽的设置,PIO内核的数据宽度和数据传输方向的设置,定时器Timer组件的计数宽度、初值和预置模式的设置等。组件加入并配置完毕后,进行自动分配地址和中断,最后点击generate按钮产生Nios Ⅱ系统。

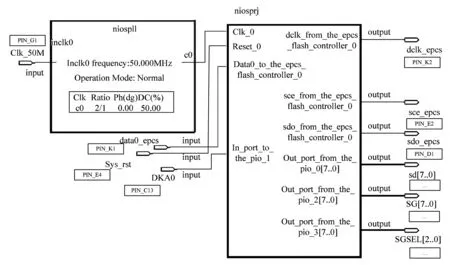

3)在顶层文件中加入锁相环符号niosp Ⅱ和Nios Ⅱ系统符号niosprj,锁相环可通过MegaWizard Plug-In Manager工具加入,用于对板上晶振50MHz进行倍频产生Nios Ⅱ系统的100MHz工作时钟。将锁相环和Nios Ⅱ系统连接,并进行引脚分配,结果如图4所示。接下来对Quartus Ⅱ工程进行编译,编译成功后生成.sof配置文件和.ptf硬件描述文件。最后利用Programmer工具将.sof配置文件下载到FPGA的RAM中形成SOPC系统的硬件电路部分,至此SOPC系统硬件平台已经生成。

图3 SOPC Builder中的组件连接和地址分配

图4 Quartus Ⅱ工程中的顶层文件

4)启动Nios Ⅱ IDE集成开发环境,建立新的工程C/C++Application,指定目标硬件为刚生成的ptf文件,并选择hello world模板;为实现定时中断控制LED灯反转,需改写hello world.c文件代码:

#include

#include“system.h”#include“altera_avalon_pio_regs.h”

#include“altera_avalon_timer_regs.h”

#include“sys/alt_irq.h”

Void Timer_init();

Void Timer_interrupts(void *context, alt_u32 id);

int i2=0;

Void Timer_init()

{alt_irq_register(TIMER_0_IRQ,0,Timer_interrupts); //中断注册函数

IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_0_BASE,0x0000); //清0定时器状态

IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER_0_BASE,0x5f5);

IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER_0_BASE,0x0e100);//定时1s

IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER_0_BASE,0x0007);//启动连续定时

}

Void Timer_interrupts(void *context, alt_u32 id)//中断服务函数

{IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_0_BASE,0); //清0定时器状态

i2=~i2; //状态变量取反

i2&=0x01;

IOWR_ALTERA_AVALON_PIO_DATA(PIO_0_BASE,i2); //状态变量输出

}

int main()

{

printf(“Hello from Nios Ⅱ!N”);

Timer_init();

while(1);

return 0;

}

该C文件中包含了标准C头文件,如输入输出头文件stdio.h,设备地址和中断号定义头文件system.h,内核寄存器访问头文件altera_avalon_pio_regs.h, altera_avalon_timer_regs.h,中断头文件sys/alt_irq.h。这些文件是由Nios Ⅱ IDE对文件进行编译后自动生成,用户无需对其进行修改。编译Nios Ⅱ工程将产生可执行.elf文件,若在用户应用程序文件夹上点击右键执行run as-Nios Ⅱ Hardware,可以观察Nios Ⅱ的C程序在目标硬件上全速执行的结果。

实验表明,不同的实验项目所遵循的实验流程大致相同,其主要区别体现在3点:①顶层文件所包含的模块和连接方式不同;②SOPC Builder中所加入的外设IP模块不同;③Nios Ⅱ IDE中的C程序设计不同。而这些区别也正好体现了SOPC软硬件设计的灵活性,学生的SOPC系统综合设计能力的不同也能在这3个方面的设计中得以体现。

4 实验项目开设方式

笔者所提出的SOPC实验教学平台在实践中通过2种开设方式使用:①随课实验,即在SOPC系统理论课程中设置部分实验学时;该部分实验难度不大,平台中的基本实验模块就能够满足需求,同时理论和实验相结合加深了对SOPC系统的理解,有利于学生的入门级学习。②创新型实验,这一部分作为SOPC设计竞赛的训练题目使用,安排在开放式创新实验室进行;该部分实验要求学生有较好的专业基础,并配以专任辅导教师进行辅导,其目的是提高学生运用先进的SOPC设计技术创造性解决实际问题的能力。

5 结语

提出了一种新型的SOPC实验教学平台的设计方法,介绍了该平台的具体硬软件设计,并提供一个具体的实验例程说明该平台实验项目的设计流程。该平台能够实现基本实验项目和创新型实验项目,这2类实验项目可以通过不同的实验开设形式进行开展,满足了不同层次的学生的需求,在高校SOPC实验教学中有良好的应用前景。

[1]韦思健,张驰,韩文龙,等.最新的SOPC技术与EDA实验教学[J].实验技术与管理,2006,23(1):113~115.

[2] 王锐,雷金奎.基于软核Nios Ⅱ的SOPC数据采集系统的设计[J].计算机测量与控制,2008,16(8):1199~1202.

[3] 贺明,王新赛.Nios Ⅱ的红外图像实时跟踪系统设计[J].电光与控制,2008,15(3):90~96.

[4] 金燕,葛远香,梁玲飞,等.基于SOPC的电能质量在线监测仪的设计[J].浙江工业大学学报,2008,36(6):664~668.

[5] 卓兴旺,李广军.基于NIOS的SOPC实验平台的构建[J].实验科学与技术,2004(4):30~33.

[6] 唐续,赵芳斌,王嘉.EDA与单片机及SOPC一体化实验教学平台研制[J].实验技术与管理,2013,30(1):73~77.

[编辑]洪云飞

2016-04-27

湖北省教育厅科学技术研究重点项目(D20141303)。

陈晓静(1980-),女,讲师,博士生,现主要从事电磁测量与仪器方面的教学与研究工作。

吴爱平(1977-),男,副教授,博士,现主要从事信号采集与处理方面的教学与研究工作;E-mail:wuaping@yangtzeu.edu.cn。

TP368.1

A

1673-1409(2016)22-0009-05

[引著格式]陈晓静,吴爱平.基于Nios Ⅱ的SOPC实验教学平台设计[J].长江大学学报(自科版),2016,13(22):9~13.