基于锁相环技术的UHF频段宽带频率源设计

赵秋明,肖 龙,许丰灵,王永琦(桂林电子科技大学信息与通信学院,广西桂林541004)

基于锁相环技术的UHF频段宽带频率源设计

赵秋明*,肖龙,许丰灵,王永琦

(桂林电子科技大学信息与通信学院,广西桂林541004)

针对UHF频段的通信系统,研制了一种UHF频段的宽带频率源。采用锁相环频率合成的方法,通过对器件选型、参数设定、环路滤波器等关键部分详细分析的方式,完成了UHF频段频率源的设计。测试结果表明,该频率源的工作频率范围为300MHz~350 MHz,步进频率为10 kHz,杂散抑制优于-45 dBc,相位噪声优于-50 dBc/Hz@100 kHz,输出功率大于-15 dBm,各项指标满足实际工程应用要求。

频率源;锁相环;UHF频带;宽带

频率源是现代短波射频通信系统的核心部件,对通信系统性能起着决定性作用,因此,频率源被人们喻为电子系统的“心脏”[1]。随着通信频率资源的日益紧缺,一种免通行证的ISM频段在通信领域内备受关注,而UHF频段作为ISM频段的一部分,因此,被广泛应用在工业、科学、医疗等无线通信领域中。目前,较为常用的频率源设计方法主要有直接数字频率合成和锁相环频率合成两种。其中采用锁相环设计的频率源具有输出频率高、频率稳定度高、频谱纯、低相位噪声、杂散抑制好等优点[2],广泛应用在无线通信系统本振的设计中。目前常用的锁相频率源,输出频率范围大多是单点或者窄带,设计宽带的锁相频率源仍然具有较强的挑战性[3]。正是基于这一点,并结合PLL的优点,研制了一种低相噪、杂散抑制度高、成本低、体积小的UHF频段宽带频率源。

1 锁相环频率合成原理介绍

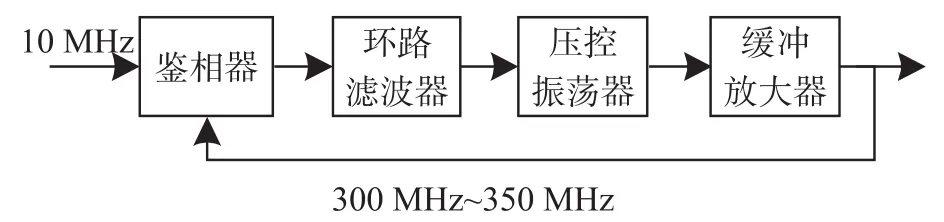

锁相环是一个传递相位的闭环反馈系统,它的基本电路单元如图1所示,主要由鉴相器、环路滤波器、压控振荡器3个部分组成[4]。

锁相环的基本工作原理:鉴相器比较参考时钟信号与压控振荡器反馈信号两者的相位差,经过环路滤波器得到与相位差信号成线性函数关系的误差电压,从而控制VCO输出特定频率,达到动态锁定[5]。

图1 锁相环结构示意图

如图1所示,环路锁定时,输出信号相位与参考时钟信号相位之间的相位差为零,即θt(t)=θo(t),且环路误差电压信号μc(t)为恒定值,从而控制VCO输出稳定的频率。

2 方案设计与分析

2.1频率源技术指标

频率源技术指标如表1所示。

表1 主要技术指标

2.2方案设计

频率源原理框图如图2所示,UHF频段宽带频率源主要包括鉴相器、环路滤波器、压控振荡器、缓冲放大器。

鉴相器采用Motorola公司的MC12202锁相环芯片,具有双充电泵输出功能。其工作电压范围为2.7 V~5.5 V,典型工作电流为5.8 mA,最高工作频率范围为1.1GHz,片内集成了4个可编程分频器,分别为前置分频器P,参考分频器R,整数分频器N,小数分频器A,可以满足300MHz~350MHz范围频率需求。数字接口采用简单的SPI接口,STM32f103处理器可以很方便地对其进行配置。

图2 频率源原理框图

环路滤波器采用一阶无源RC比例积分滤波器。其电路简单,不仅简化了环路滤波器电路的设计与调试,而且减小了环路锁定时间,有利于增强环路的稳定性[6]。

压控振荡器采用MAXIM公司的MAX2608集成振荡器芯片,其工作电压范围为2.7V~5.5 V,单端最佳匹配输出功率最大为-10 dBm。片上集成变容二极管,通过改变外围电路的电感值设置其起振频率,使得外部调谐电路更加简单,消除了过多无源元件引入的杂散[7]。起振信号的频率范围为300MHz~500MHz,满足频率源的频率范围设计要求。偏离中心频率100 kHz处的相位噪声为-100 dBc/Hz,满足频率源的相位噪声设计要求。

缓冲放大器采用Agilent公司的AT41511低噪声通用放大器,其工作电压为5 V,典型工作电流为25mA。工作频率500MHz时,噪声系数约0.8 dB,增益为20 dB,满足频率源的本振功率放大要求。

3 电路设计与分析

3.1鉴相器电路设计

鉴相器电路原理图如图3所示,其中BISW和D0为双充电泵输出,LD为环路锁定指示输出。假设频率源输出的频率为325MHz,而步进频率 f r为10 kHz,因此可以求得MC12202内部集成分频器总的分频比为325MHz/10 kHz=32 500。ARM控制器(STM32f103)通过3线SPI接口(图中LE、Din、CLK)向MC12202的内部分频器P、N、A、R中写入相应的分频值。

图3 鉴相器电路原理图

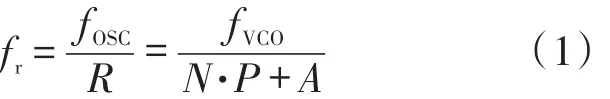

环路锁定时,输入信号与压控振荡器信号输出频差为零,相位差不再随时间变化,此时误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等[8],即

其中 fOSC为10MHz参考时钟信号,fVCO为合成频率信号。若前置分频器值P=64,依据式(1),则可以求得R=1 000,N=507,A=52。对于其它的频率信号,计算过程依此类推,不再赘述。

3.2环路滤波器电路设计

环路滤波器的设计是频率源设计的重要环节,其决定了合成器的杂散抑制、相位噪声、环路稳定性以及锁定时间等非常重要的环路参数[9]。环路滤波器电路原理图如图4所示,该模块选用一阶无源RC比例积分滤波器作为环路滤波器,鉴相器输出的相位误差信号最大为5 V,而MAX2608振荡器的电压调谐范围为0.4 V~2.4 V,满足电压调谐范围。

图4 环路滤波器电路原理图

环路滤波器的参数计算公式[10]满足:

其中N为反馈环路总分频数,ξ为环路阻尼因子,Vp为鉴相器充电泵的工作电压,ω为环路带宽。由于频率源的频率输出范围为300MHz~350MHz,因此相应地分频数N为30 000~35 000,工程应用中N取中点值32 500。鉴相器的充电泵电压Vp为5 V,压控振荡器的灵敏度为30MHz/V。一般取阻尼因子ξ=0.707,环路带宽ω≤fr/10[9-10]。

依据以上理论分析,若环路带宽为w=2πfr/50= 1 256 rad/s,电容C=0.1μF,则可以计算出R1=7.69 kΩ,R2=6.92 kΩ,取标称值R1=7.5 kΩ,R2=6.8 kΩ。

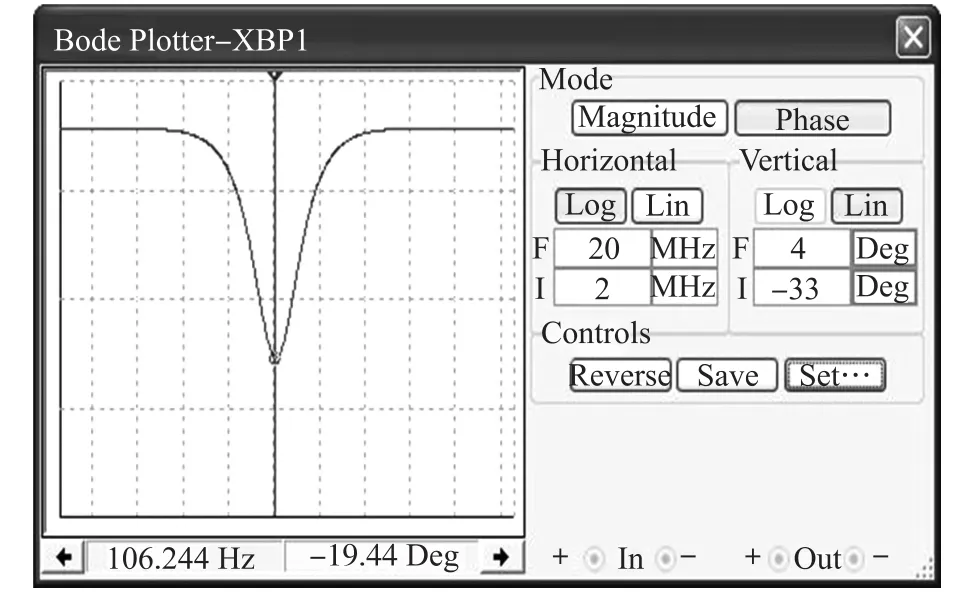

为了使得频率源在300MHz~350MHz范围均能锁定,经过反复调试优化后,实际的电阻取值分别为R1=10 kΩ,R2=10 kΩ。在Multisim 12.0中建立原理图,其相频特性仿真结果如图5所示。

图5 环路滤波器相频特性图

从图5中可以看出,环路滤波器在截止频率106.244 Hz处有19.44°的相位返回特性,增强了环路的稳定性。

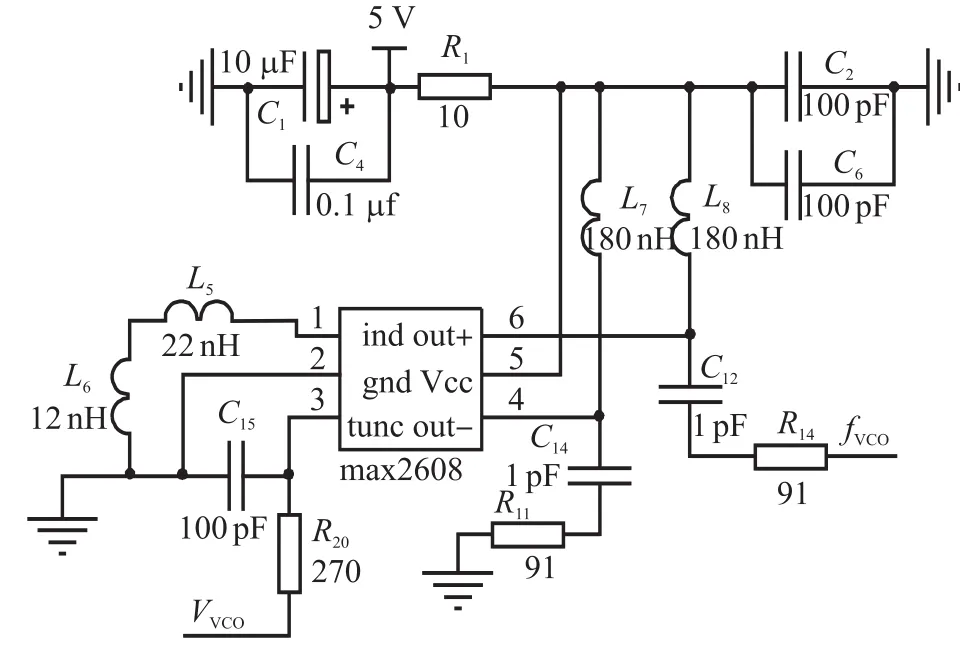

3.3压控振荡器电路设计

压控振荡器原理图如图6所示,因频率源合成的频率范围为300 MHz~350 MHz,根据MAX2608芯片手册的电感值对应表,选定中点值频率325 MHz所对应的电感值34 nH。由于该电感值并不是标称的电感值,因此该模块采用两个村田Murata系列的高Q值电感串联,图中L5和L6标准电感值分别为22 nH、12 nH。

图6 压控振荡器原理图

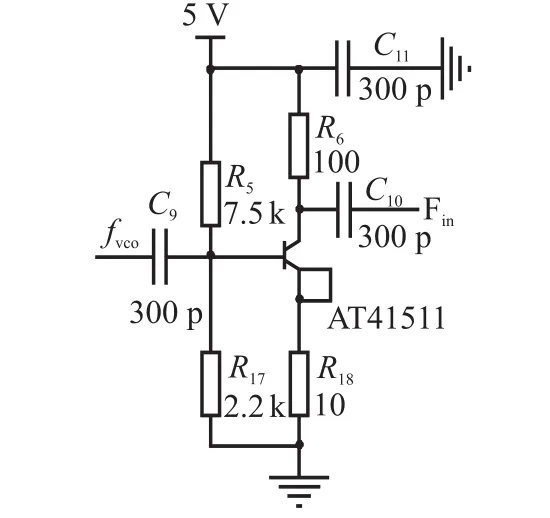

3.4缓冲放大电路设计

缓冲放大器原理图如图7所示,该模块采用A类共发射极放大电路,其中R5和R17为基极提供直流偏置电压,R16为集电极限流电阻,R18为发射极负反馈电阻,确保了放大器的稳定性。该方案电路简单、成本低,易于实现。

图7 缓冲放大电路原理图

4 性能测试与分析

软件开发工具主要是Keil Software公司提供的Keil uVision4以及 NI公司提供的 Multisim 12.0。编程语言主要为C语言,C语言是在基于STM32单片机的ARM Cortex-M平台上完成。UHF频段的宽带频率源实物制作图如图8所示,在该硬件平台上,主要是在实验室里,通过设定合成300 MHz~350MHz频率范围内不同的频率信号,在输出端连接至频谱分析仪(型号为AgilentN9344C)观察其合成信号的频谱中心频率、输出功率、杂散抑制度与相位噪声,测试主要包括以下3个部分:

(1)测试频率源的输出频率范围和输出功率是否正确,300MHz~350MHz之间连续步进为10 kHz,输出功率≥-15dBm。

(2)测试频率源输出整数频率信号和小数频率信号的杂散抑制是否优于-45 dBc。

(3)测试频率源输出300 MHz~350 MHz本振信号偏移中心频率100 kHz处的相位噪声是否优于-50 dBc/Hz。

图8 实物图

按照步骤(1),测试频率源的输出频率范围及输出功率,如图9所示。

图9 中心频率的频谱图

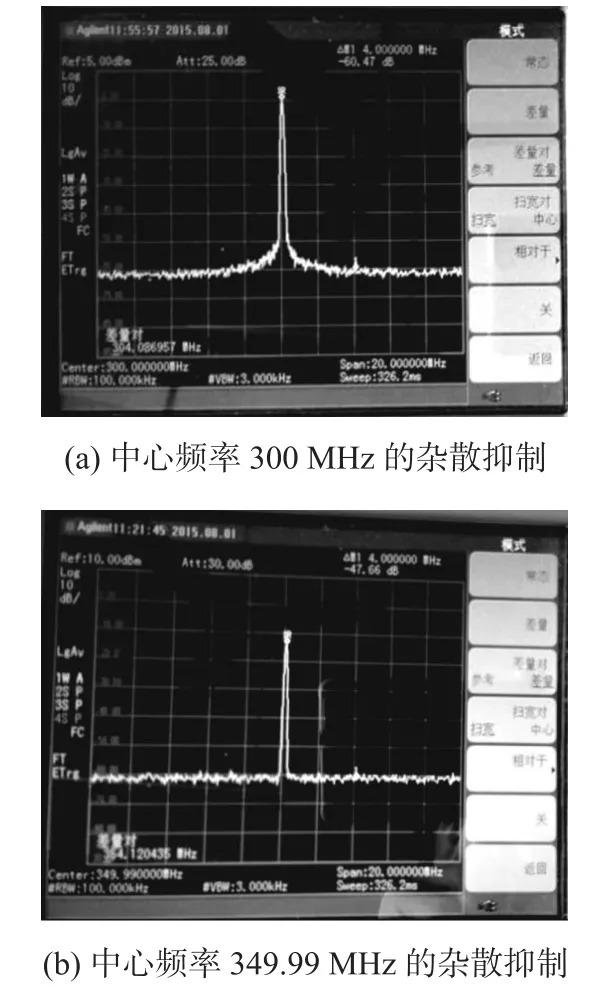

按照步骤(2),测试频率源整数频率信号和小数频率信号的杂散抑制,如图10所示。

图10 杂散抑制图

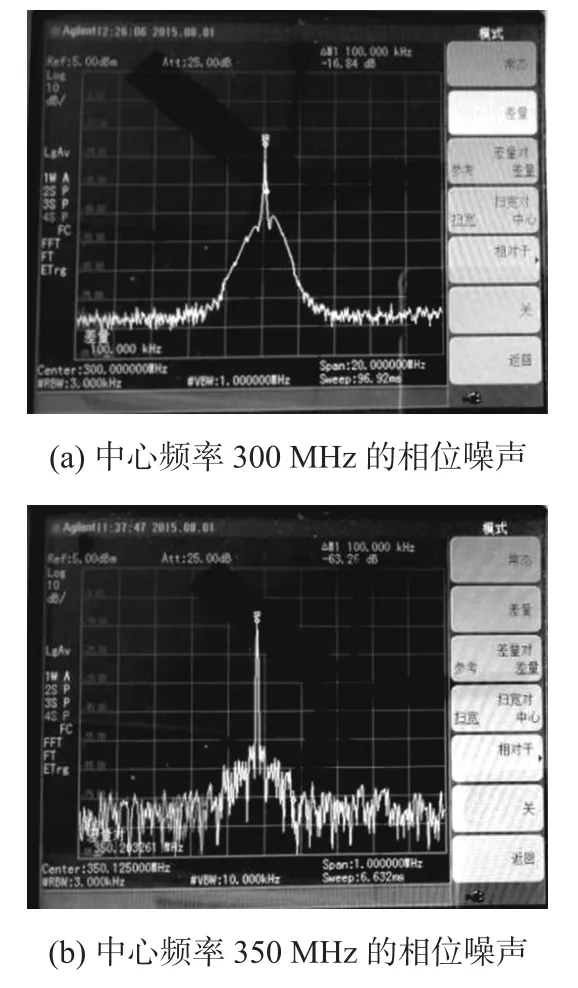

按照步骤(3),测试频率源偏移中心频率100 kHz处的相位噪声,如图11所示。

图11 相位噪声图

如图9所示,验证了频率源在300MHz~350MHz之间连续步进为10 kHz,输出功率≥-15 dBm。如图10所示,中心频率300MHz、349.99MHz的杂散抑制分别为-60.47 dBc、-47.66 dBc,验证了频率源的杂散抑制度优于-45 dBc。如图11所示,偏移中心频率300MHz、350MHz的100 kHz处的PNmark值分别为-16.84 dBc、-63.26 dBc,根据文献[2]中相位噪声计算公式PN=PNmark-10 lgRBW,其中RBW为频谱分析仪的分辨率带宽。因此,可以计算出偏移中心频率300MHz、350MHz的100 kHz处的相位噪声分别为-51.61 dBc、-98.03 dBc,验证相位噪声优于-50 dBc/Hz@100 kHz。

5 结束语

本文充分利用PLL的优点,给出了一种UHF频段的宽带频率源的实现方案。实测结果表明:该频率源具有电路结构简单、低相位噪声、杂散抑制度高、频带宽、成本低、体积小等优点,通过改变压控振荡器外部调谐电感和环路滤波器的参数,便可以实现合成300MHz~500MHz内更宽频率范围内的任何频率点信号,具有很好的带宽拓展性。该频率源达到了预期的设计目的,为宽带频率源的设计提供了一种工程实现方法,具有很高的工程应用价值。

[1] 梁孝彬,石玉,王轩.基于DDS技术L波段小步进低相噪频率源设计与实现[J].电子元件与材料,2015,34(5):54-57.

[2] 徐述武,汪海勇,唐云峰.基于ADF4350锁相频率合成器的频率源设计与实现[J].电子器件,2010,33(6):725-729.

[3] 管凝,卢起斌.李正详.基于ADF4001与MAX2620的宽带锁相频率源设计[J].电子器件,2011,34(4):424-427.

[4] 陈邦媛.射频通信电路[M].北京:科学出版社,2006.

[5] Ma Mingxiao,Wang Hao,Li Zhijun.Phase-Locked Frequency Source in the S-Band Transceiver System[C]//Communication and Technology(ICCT),2012 IEEE 12th International Conferenceon.IEEE,2012:924-928.

[6] Li Zhigang,Ren Pengfei.Design of an L-band PLL Frequency Synthesizer[C]//Mechatronic Sciences,Electric Engineering and Computer(MEC),Proceedings 2013 International Conference on. IEEE,2013:3244-3247.

[7] Cotter W Sayre.Complete Wireless Design,Second Edition[M]. Beijing:Publishing Houseof Electronic Industry,2010.

[8] 宋建辉,袁峰,振良,等.基于ADF4360-6和ECL分频的高精度时间测量模块设计[J].仪表技术与传感器,2009(5):63-65.

[9] 赵彦芬.频率合成器环路滤波器设计[J].无线电工程,2006,36(4):39-41.

[10]张涛,陈亮.电荷泵锁相环环路滤波器参数设计与分析[J].现代电子技术,2008(9):87-90.

赵秋明(1954-),男,汉族,广西桂林人,桂林电子科技大学硕士生导师,副教授,高级工程师,研究方向为无线通信、电路与系统;

肖龙(1988-),男,汉族,湖北黄冈人,桂林电子科技大学信息与通信学院硕士研究生,研究方向为无线通信,xll_xiaolong@163.com;

许丰灵(1990-),男,汉族,广东揭阳人,桂林电子科技大学信息与通信学院硕士研究生,研究方向为嵌入式应用;

王永琦(1989-),男,汉族,河南驻马店人,桂林电子科技大学信息与通信学院硕士研究生,研究方向为天线设计与微波测量。mailto:296033816@qq.com。

Design of a Broadband Synthesizer of UHF-Band Based on PLL

ZHAO Qiuming*,XIAO Long,XU Fengling,WANG Yongqi

(School of Information and Communication Engineering,Guilin Uniυersity of Electronic Technology,Guilin Guangxi 541004,China)

In view of the communication system of UHF-band,a broadband frequency source in UHF-band is designed.According to detailed analysis of the devices selection,parameter setting,loop filter and other key parts,a synthesizer of UHF-band is complemented based on themethod of PLL frequency synthesis.The test results show that its frequency range is 300MHz~350MHz,step frequency is10 kHz,spurious reduction isbetter than-45 dBc,phase noise isbetter than-50 dBc/Hz@100 kHz,outputpower ismore than-15 dBm,the indicatorsmeet the practicalengineering application requirements.

frequency source;pll;uhf-band;wide-band

TN742

A

1005-9490(2016)04-0898-05

2015-08-07修改日期:2015-09-08

EEACC:123010.3969/j.issn.1005-9490.2016.04.028