基于FPGA的可配置IIC总线接口设计

张素萍,高照阳,张建芬(.天津中德职业技术学院电气与能源学院,天津0050;2.上海交通大学上海市复杂薄板结构数字化制造重点实验室,上海200240;.暨南大学珠海校区,广东珠海59070)

基于FPGA的可配置IIC总线接口设计

张素萍1,高照阳2*,张建芬3

(1.天津中德职业技术学院电气与能源学院,天津300350;2.上海交通大学上海市复杂薄板结构数字化制造重点实验室,上海200240;3.暨南大学珠海校区,广东珠海519070)

针对传统IIC总线接口的FPGA设计可重用性不高的问题,提出了一种基于FPGA的可配置IIC总线接口设计方案。该方案采用同步有限状态机设计方法和硬件描述语言Verilog HDL,对IIC总线的数据传输时序进行模块化设计,采用Signal Tap II对设计模块进行仿真验证。实验结果表明,该设计接口作为一种主控制器接口,可实现与具有IIC总线接口的从机器件100 kbyte/s和400 kbyte/s的可靠数据传输。该方案具有可重用度高、可配置性强、控制灵活等优点,并已成功运用于工程实践中。

FPGA;IIC总线接口;Verilog HDL;可配置;仿真验证

IIC总线(Inter Integrated Circuit bus)是Philips公司开发的一种用于芯片间通讯的串行传输总线,它仅需串行时钟线SCL和串行数据线SDA两根信号线,即可实现全双工同步数据传送,能够极方便地构成多机系统和外围器件扩展系统,在现代电子设计系统中得到越来越广泛的应用,并已经成为一种世界性的工业标准[1-2]。

目前,从市场新购的FPGA器件不具有IIC接口,所以,其还不能与具有IIC接口的器件直接连接,要想使FPGA能够与IIC接口从器件进行数据通讯,必须在FPGA内部设计IIC主控制器接口。至此,关于利用FPGA实现IIC总线接口设计方面的工作,多是对IIC总线协议的FPGA设计进行了探索性的研究,实用性有待加强,可重用性不高。如果用户自己构建的SOPC系统中需要IIC总线接口,还需要重新设计,势必会增加系统的研发周期。鉴于此,本文设计了一种基于FPGA的可配置IIC总线主控制器接口,用户使用时只需修改相应的配置参数,即可应用到自己的SOPC系统中,从而加快系统设计进度,缩短产品研发周期,提高产品市场竞争力。

1 IIC总线特征及工作原理

1.1IIC总线特征[3-4]

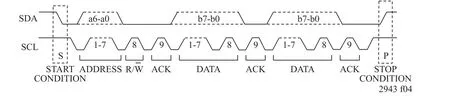

在IIC总线中,只有在总线处于“闲”状态时,才能开始数据传输。在数据传输期间,只要时钟线SCL为高电平,数据线SDA必须保持稳定状态,否则数据线SDA上的任何变化都被当作“启动”或“停止”信号。图1为IIC总线状态的定义。

图1 IIC总线状态示意图

A段:总线处于闲状态,此时,数据线SDA和时钟线SCL均为高电平状态。

B段:启动数据传输状态,当时钟线SCL为高电平状态时,数据线SDA由高电平变为低电平的下降沿被认为是“启动”信号。只有出现“启动”信号后,其它的命令才有效。

C段:停止数据传输状态,当时钟线SCL为高电平状态时,数据线SDA由低电平变为高电平的上升沿被认为是“停止”信号。只要“停止”信号出现,所有的外部操作都结束。

D段:数据有效状态,在出现“启动”信号以后,当时钟线SCL为高电平状态时,数据线SDA是稳定的,这时数据线SDA上的数据即为要传送的数据。数据线SDA上的数据的改变必须在时钟线SCL为低电平期间完成,每位数据占用一个时钟脉冲。每个数据传输都是开始于“启动”信号,终止于“停止”信号。应答信号:每个正在接收数据的从机在接收到一个字节的数据后,通常需要发出一个应答信号。而每个正在发送数据的从机在发出一个字节的数据后,通常需要接收一个应答信号。与此同时,主机控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。

1.2IIC总线工作原理[5-6]

IIC总线数据传输工作原理如图2所示,首先,主机发送一个启动信号,总线上所有从机检测到此启动信号后开始接收第1个字节,第1个字节包括七位从机地址和一位读/写指示位。接着,如果某一从机检测出收到的7位从机地址与自己的地址标识相符,则向主机发送一个回应ACK(低有效)。然后,从机依照读/写指示位向主机发送或从主机接收数据。每1字节传输完后,若是读操作,则主机向从机发送一个回应ACK(低有效),若是写操作,则由从机向主机发送一个回应ACK(低有效)。最后,传送完毕,主机以一个停止信号,来结束整个数据传输过程。

图2 IIC总线数据传输时序图

2 基于FPGA的IIC总线接口设计

2.1IIC总线接口模块结构设计

IIC总线接口结构设计如图3所示,主要包括内部分频器和IIC总线接口控制时序逻辑模块2部分。

内部分频器:通常FPGA的外部输入时钟频率比较高,例如50MHz,所以必须经过内部的分频器输出符合I2C总线要求的数据传输速率(标准模式100 kbit/s,快速模式400 kbit/s),才能满足IIC总线数据传输的时序要求。

IIC总线接口控制时序逻辑模块:此部分是IIC总线接口模块的控制核心,IIC总线数据传输的所有时序控制逻辑都由它产生,例如,启动信号和停止信号的产生,对从器件的寻址,总线上数据的发送和接收。同时,其内部集成数据锁存器和移位寄存器,其中,数据锁存器主要用于暂存发送的数据、地址和控制信息和接收数据,移位寄存器主要用于对发送的数据进行并/串转换,然后发送到数据线SDA上,或者从数据线SDA上接收的数据进行串/并转换,然后由主机进行接收。

图3 IIC总线接口模块结构框图

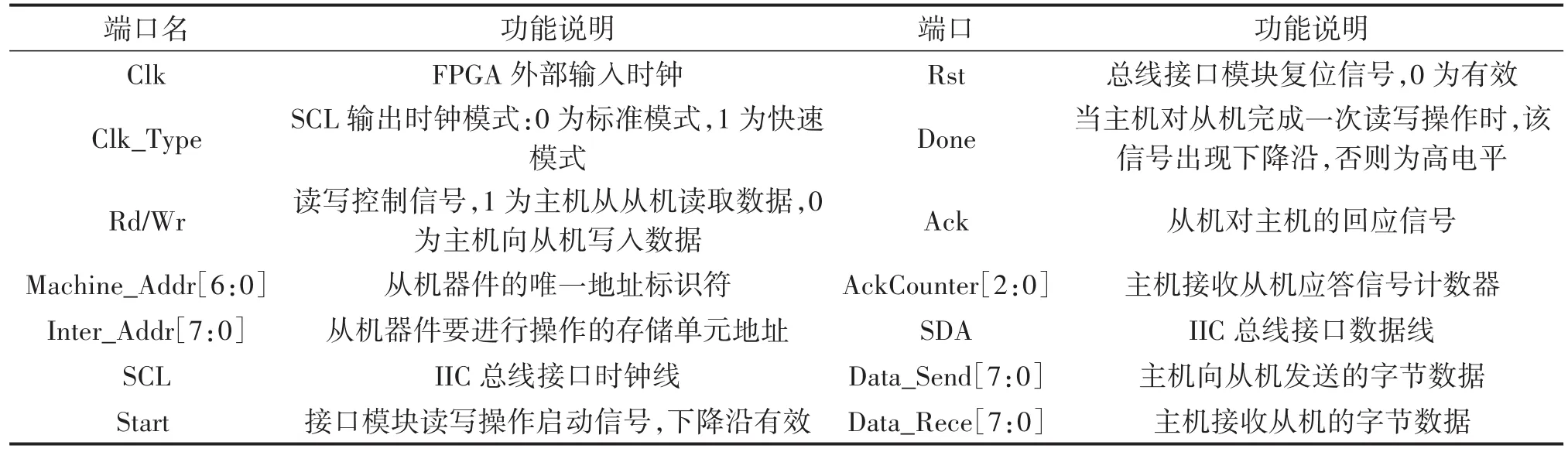

2.2IIC总线端口映射及功能说明

IIC总线端口映射及功能如表1所示。由图3和表1可知,本文设计的IIC总线接口模块能够实现数据传输的两种基本数据操作模式即单字节数据写模式和单字节数据读模式。由于该模块提供读写前、读写过程中和完成后的相应的标志信息(Start、Inter_Addr,Done、Ack、AckCounter),所以,主机能够根据这些信息判断是否进行下一字节数据的读写操作,从而实现从机内部连续存储单元的读写操作,最终实现IIC总线数据传输的4种操作模式,分别为单字节数据写、单字节数据读、多字节数据连续写、多字节数据连续读。例如,多字节数据连续写模式,当主机通过该总线接口对从机成功完成一次写操作后,Done端口会现下降沿脉冲,主机检测到该信号后,这时只要配置好Clk_Type、Rd/W r、Start、Machine_Addr[6:0]、Inter_Addr[7:0]、Data[7:0]这些信号,即可进行相邻地址单元的数据存储,直到写入完指定数据长度的字节数据为止。至于连续读写多少数据,由主机控制程序决定,从而避免了从器件连续读写操作传统模式数据长度的限制。

表1 IIC总线端口映射及功能说明

2.3IIC总线接口模块的Verilog HDL设计

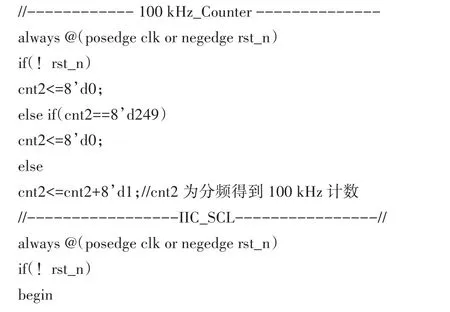

2.3.1IIC总线接口时钟SCL信号产生设计

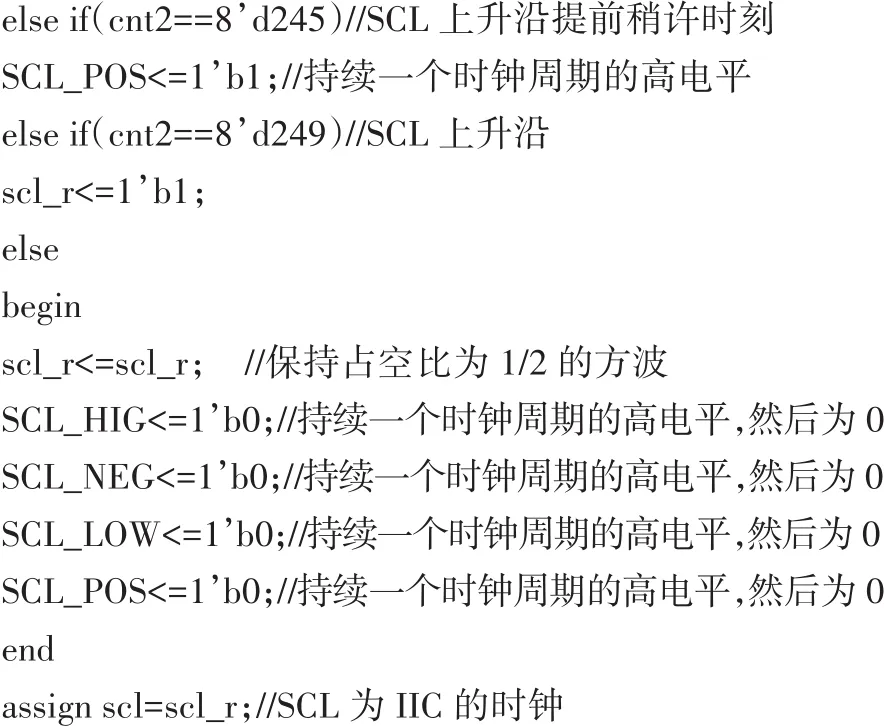

本系统设计的时钟信号SCL有两种输出频率100 kHz和400 kHz,通过主机输入信号Clk_Type进行选择确定,当其为1时,SCL输出频率为100 kHz,当其为0时,SCL输出频率为400 kHz。时钟信号SCL的产生是将FPGA外部输入时钟信号经过分频计数器而得到所需要的信号。系统产生100 kHz的时钟信号所用的分频计数器常数为249,而400 kHz的时钟信号所用的分频计数器常数为62。此外,对IIC总线接口控制时序逻辑模块进行设计时,需要对时钟线SCL一个完整周期内的上升沿SCL_POS、下降沿SCL_NEG、时钟周期高电平部分的中间时刻SCL_HIGH、时钟周期低电平部分的中间时刻SCL_LOW这些信号进行正确检测,才能设计出符合IIC总线协议规范的逻辑控制时序。所以,还要利用本 分 频 计 数 器 产 生 SCL_POS、SCL_HIGH、SCL_NEG、SCL_LOW这4种脉冲信号。本系统在FPGA外部始终为25MHz时,用Verilog HDL对时钟分频计数器进行设计工作。其产生100 kHz的SCL信号的主要VERILOGHDL代码如下:

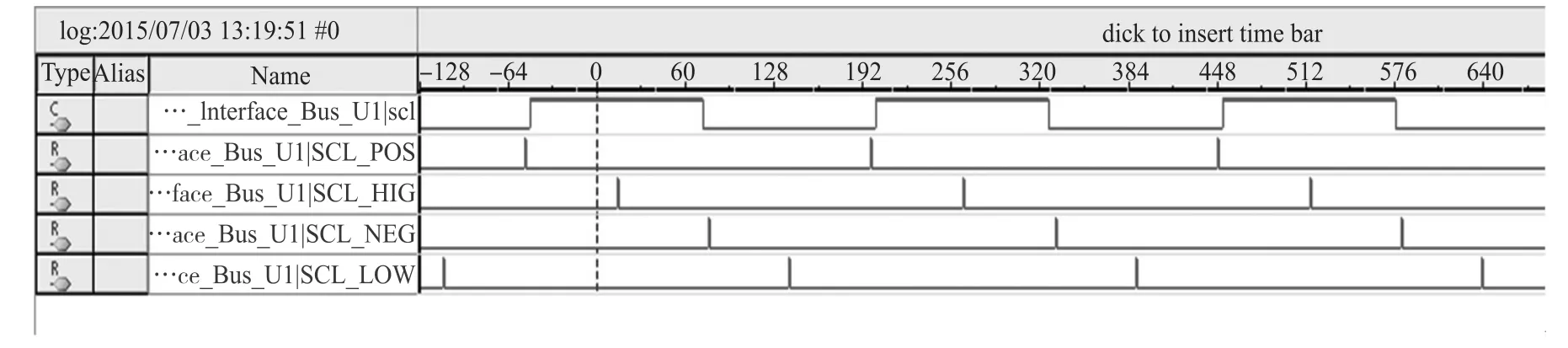

本系统设计的IIC总线接口时钟信号SCL及其相关附加信号实时仿真波形如图4所示。

图4 IIC总线接口时钟信号SCL及相关附加信号实时仿真数据波形图

2.3.2状态机模型

由IIC总线数据传输协议可知,在数据传输过程中存在着空闲、启动、停止、读、写等工作状态,所以我们可以采用同步状态机来进行该模块设计[7-8]。本系统设计的同步状态机共分为14个工作状态,依次为空闲状态IDLE,空闲状态IDLE1,产生起始信号状态START1,写入从器件地址工作状态ADD1,接收从器件应答信号工作状态ACK1,写入从器件内部字节单元地址工作状态ADD2,接收从器应答信号工作状态ACK2,产生读操作开始前的起始信号工作状态START2,读操作重新写入从器件地址工作状态ADD3,接收从器件应答信号工作状态ACK3,单字节数据读写工作状态DATA,接收从器件应答信号工作状态ACK4,主机向从器件发送非应答信号工作状态HIGH,产生停止信号工作状态STOP1。基中,IDLE和IDLE1工作状态主要用于检测主机发送过来的下降沿START信号,如果检测到,才进入工作状态START1,否则,一直循环检测等待。主机向从机写入一个字节数据需要经过以下工作状态IIDLE,IDLE1,START1,ADD1,ACK1,ADD2,ACK2,DATA,ACK4,STOP1。主机从从器件读取一个字节数据需要经过以下工作状态IDLE,IDLE1,START1,ADD1,ACK1,ADD2,ACK2,START2,ADD3,ACK3,DATA,HIGH,STOP1。利用该同步有限状态机和Verilog HDL语言,可以快速设计和实现出IIC总线接口的数据传输控制时序逻辑功能模块。由于本系统设计的IIC总线接口的时钟信号SCL输出频率为100 kHz或400 kHz,所以,该状态机的工作时钟信号频率要高于SCL信号频率,再加上本工作状态机要实时检测SCL_POS、SCL_HIGH、SCL_NEG、SCL_LOW及START信号,所以,该工作状态机的CLK信号频率选为FPGA的外部输入CLK信号(25MHz)。本系统设计的同步有限工作状态机所图5所示。

图5 IIC总线接口的同步有限工作状态机示意图

2.3.3IIC总线接口数据传输中的基本功能模块设计

(1)主机产生启动信号设计

当IIC接口模块检测到主机发送过来的有效START信号后,该模块由空闲状态转入到产生IIC接口模块启动信号状态,然后检测SCL是否处于高电平状态,如是,则置SDA由高电平转为低电平状态,即可产生该模块的启动信号。该模块的主要Verilog HDL主要设计代码如下:

(2)主机产生停止信号设计

当主机不需要向从机发送数据或从从机接收数据时,在应答信号产生后,即可转到终止数据传输状态,然后检测SCL是否处于高电平状态,如是,则置SDA由低电平转为高电平状态,即可产生该模块的停止信号。该模块的主要Verilog HDL代码如下:

(3)主机发送和接收一个字节数据设计

由于IIC是串行数据传输总线,主机要发送一个字节的数据,必须将字节数据经过并/串转换,然后在时钟线SCL的作用下将每一个BIT位发送到数据线SDA上。主机要接收一个字节的数据,必须将数据线SDA上每个数据位经过串/并转换,组合成一个字节的数据,供主机进行接收和处理。该模块的Verilog HDL主要代码如下(以写操作为例):

(4)主机接收从机应答信号和主机向从机产生非应答号设计

当主机向从机写入器件地址、字节地址及数据时,从机会产生相应的应答信号(拉低SDA信号),主机检测到此信号后,才能下一数据传输过程。当主机不需要再向从机接收数据时,主机此时可以向从机发送非应答号(拉高SDA信号),然后产生停止信号,从而结束整个数据传输过程。主机接收从机应答信号的主要Verilog HDL代码如下:

通过上述基本功能模块的组合,就可以实现一次完整的IIC总线数据传输过程中的单字节写、单字节读操作模式,通过设计主机读写从机数据控制电路模块,实例化IIC总线接口读写基本操作模块,从而间接实现多字节连续写、多字节连续读操作模式。

3 仿真验证

本接口设计在Quartus II 12.1开发环境下利用数据逻辑分仪Signal TAP II对IIC总线接口时序进行了实时仿真,其中,FPGA作为主控制器件,从器件选用EEPROM器件(AT24C08),为验证I2C总线接口模块的读写操作功能是否正常,需要设计信号产生模块,将其与设计好的IIC总线接口模块相连接[9-10]。图6是利用Quartus II产生的系统硬件仿真验证连接图。

图6 系统硬件仿真验证连接图

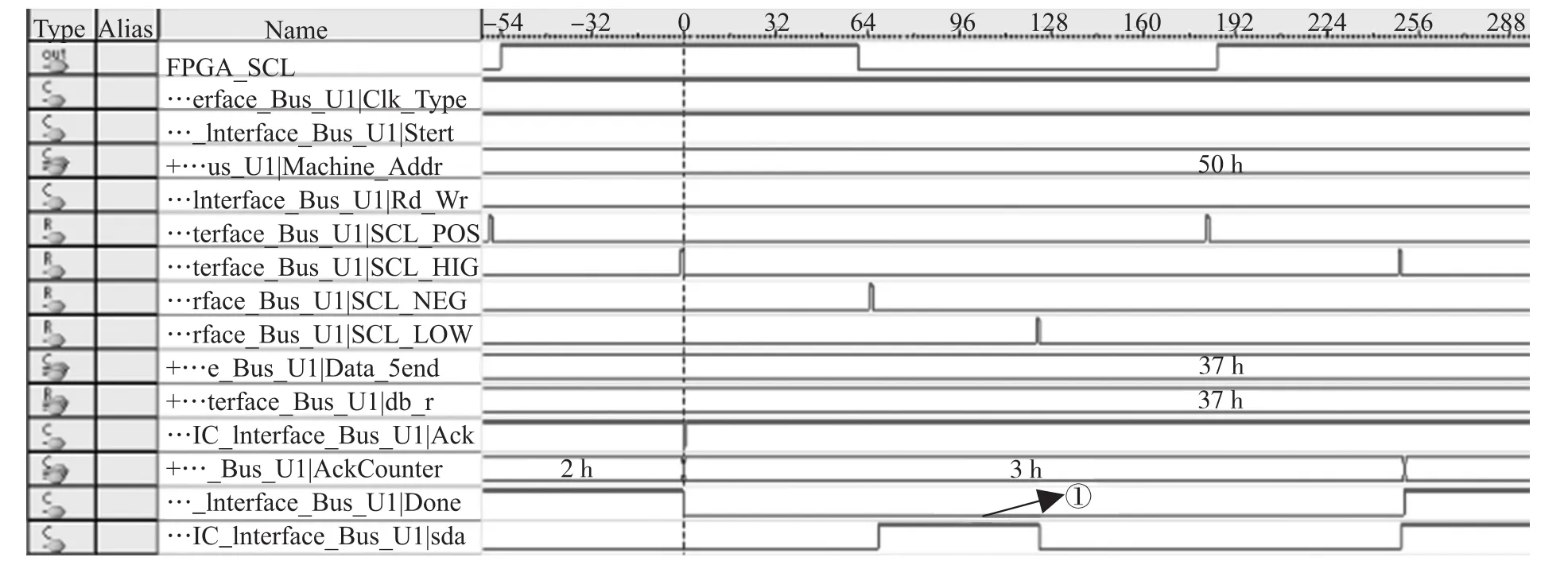

3.1主机向从机器件内某地址单元写入一字节数据仿真验证

该功能模块的仿真验证如图7所示。从图7可知,主机是向从机(地址码为50H)器件内的04地址单元写入0X37H,一次完整的写操作后,从机产生了一个有效的下降沿Done信号,同时从机产生了3次应答信号(SDA为低),产生应答信号的时刻分别为主机向从机写入器件地址后、写入从机器件字节地址后、写入字节数据后。整个数据写操作结束后,由主机产生了一个停止信号(SDA由低电平变为高电平)。标注①处SDA变高是由于从机向主机产生应答信号ACK(拉低SDA)后,释放了数据线SDA,所以,数据线SDA会变高,此后,主机向从机产生停止信号,所以,SDA又从低电平变为高电平状态。上述实时仿真波形图中,时钟线SCL一个周期中的各个状态信号 SCL_POS、SCL_HIGH、SCL_NEG、SCL_LOW均为正常产生,符合预期设计要求。

图7 主机向从机内某地址单元发送一个字节数据仿真波形图

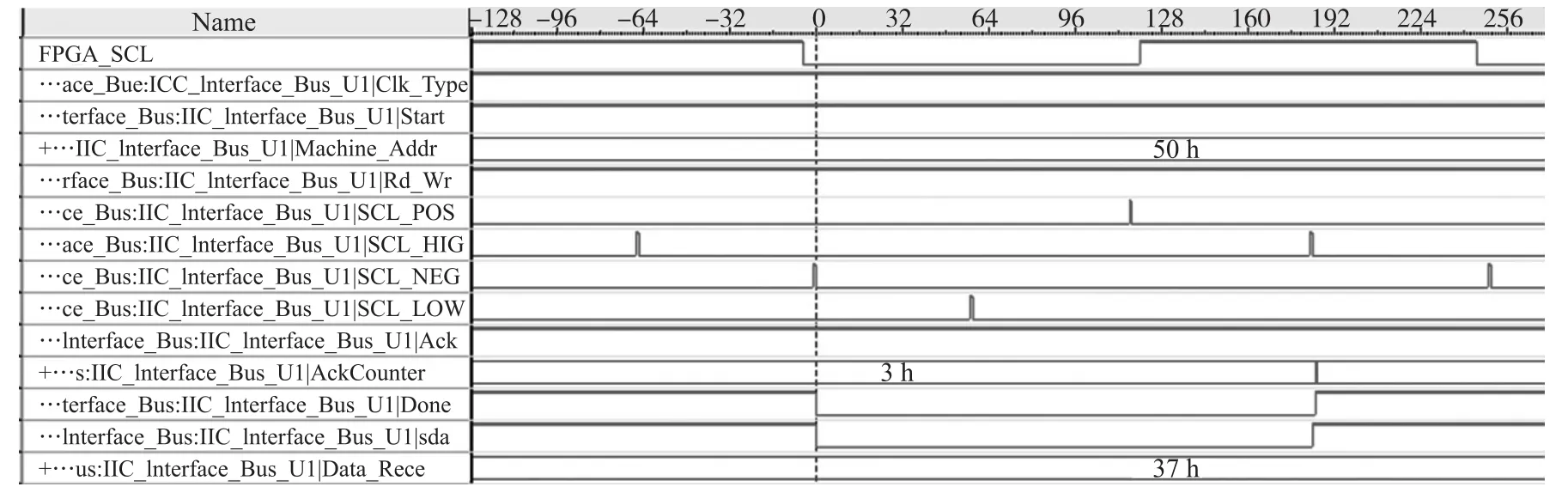

3.2主机从从机器件内某地址单元读取字节数据仿真验证

该功能模块的仿真验证如图8所示。从上图8可知,主机是读取图7中从机(地址码为50H)器件内的04地址单元写入的数据,读取数据为0X37H,主机和从机完成一次完整的读操作后,产生了一个有效的下降沿Done信号,同时从机产生了3次应答信号(SDA为低),产生应答信号的时刻分别为主机向从机写入器件地址后、写入从机器件字节地址后、再入写入从机器件地址后。整个数据读操作结束后,由主机产生了一个停止信号(SDA由低电平变为高电平)。同时,主机读取从机数据后,向从机产生了非应答信号(SDA为高电平),而后,向从机产生停止信号。上述实时仿真波形图中,时钟线SCL一个周期中的各个状 态 信 号SCL_POS、SCL_HIGH、SCL_NEG、SCL_LOW均为正常产生,符合预期设计要求。

图8 主机从从机内某地址单元读取单字节数据仿真波形图

3.3主机向从机连续地址单元写入数据,并对该连续地址单元进行读取仿真验证

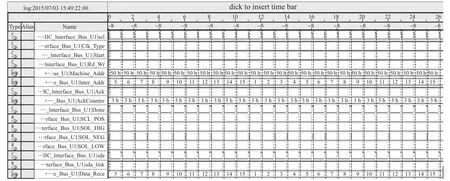

该功能模块的测试验证方法为主机向从机连续地址单元(0X01-0X0F)依次写入十进制字节数据(1,2,3,…,15),然后主机再把写入的数据连续读取出来。数据仿真验波形图如图9所示。

图9 主机读取从机连续地址单元数据仿真波形图

从图9可知,主机从从机器件内连续地址单元Inter_Addr(1,2,3,…,15),读出的十进制数据Data_Rece依次为1,2,3,…,15,每一次读操作都产生了一个有效的下降沿Done信号,同时,从机产生应答信号的次数均为为3次,主机每一次读操作都产生了一个非应答信号(SDA为高电平)。通过以上分析,说明主机能够正确对从机连续地址单元进行读写操作。

4 结论

本文根据IIC总线的工作原理、数据传输时序,利用同步有限状态机设计方法和硬件描述语言Verilog HDL,设计了一种基于FPGA的可配置IIC总线接口,并利用数据逻辑分析仪Signal Tap II对设计模块进行了仿真验证。从实时在线仿真结果可以看出,整个时序完全符合IIC总线协议规范要求,并且所编写的IIC接口模块Verilog HDL代码是可综合的,可下载到具体的FPGA器件中。笔者已成功下载到ALTERA公司的EP4CE30F23C6器件上,并使该器件具备IIC总线主控制器接口功能,经测试验证,主机能够对从器件进行正确读写操作。该IIC总线接口设计已成功应用于工程实践中,运行稳定、可靠、工作时序正常。与传统设计方案相比,该方案具有实用性强、可重用度高,可配置性强,控制灵活等优点,具有较好的实际应用价值。

[1] 何立民.I2C总线应用系统设计[M].北京:北京航空航天大学出版社,2004.

[2] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2005.

[3] 赵辉,董德存.I2C总线技术及其应用实例[J].微型电脑应用,2005,21(4):61-63.

[4] 胡文静,李外云,刘锦高.I2C总线接口的FPGA实现研究[J].计算机工程与应用,2005(12):116-118.

[5] 吕炎军,王泽勇.基于FPGA的I2C总线接口设计[J].自动化技术与应用,2006,25(4):37-39.

[6] 袁江南.一种I2C主控器IP核的设计与FPGA实现[J].厦门理工学院学报,2006,14(2):40-43.

[7] 陈穗光,葛建华.I2C总线接口协议设计及FPGA的实现[J].山西电子技术,2006(6).

[8] 李红刚,杨林楠,张丽莲,等.基于FPGA的高速多通道数据采集系统设计[J].计算机测量与控制,2006,14(10):1407-1409.

[9] 陈科,唐宁,雷求胜,等.一种状态优化的I~2C总线主控制器的FPGA设计[J].电子器件,2010,33(6):738-741.

[10]孟庆浩,边旭东,扈佳林,等.基于FPGA的多路无串扰超声测距系统的设计与实现[J].传感技术学报,2013,26(4):582-588.

张素萍(1979-),女,汉族,河南周口人,天津中德职业技术学院,讲师,硕士,主要研究方向为自动化控制与集成电路设计,zhshup2009@163.com;

高照阳(1975-),男,汉族,河南郑州人,上海交通大学上海市复杂薄板结构数字化制造重点实验室,博士研究生,主要研究方向为精密与微细制造,机械电子,gaozhaoyang2009@sjtu.edu.cn。

Development of Configurable IIC Bus Interface Based on FPGA

ZHANG Suping1,GAO Zhaoyang2*,ZHANG Jianfen3

(1.Tianjin Sino-German Vocational Technical College Electrical Engineering&Energy College,Tianjin 300350,China;2.ShanghaiKey Laboratory of Digital Manufacture forThin-Walled Structures,Shanghai Jiao Tong Uniυersity,Shanghai 200240,C hina;3.Jinan Uniυersity ZhuhaiCampus,ZhuhaiGuangdong 519070,China)

Aimed at lower reusability of FPGA design in traditional bus interface of IIC,one configurable FPGA-based bus interface design of IIC was proposed.Data transmission sequence of IIC bus was designed in modules with finite state synchronous circuit design method and hardware description language of Verilog HDL.The designedmoduleswere simulated,tested and verified by using the data logic analyzer of Signal Tap II.The experimental results show that this interface could reliably achieve the data transmission of 100 kbyte/s and 400 kbyte/swith the slaves using IIC bus interface and ithas the advantages ofhigher reusability,strong configurability,flexible control.Moreover,the designed interfacewas successfully applied to engineering practice.

FPGA;IIC bus interface;Verilog HDL;configurable;simulation verification

TP274

A

1005-9490(2016)04-0866-08

2015-07-31修改日期:2015-09-02

EEACC:6210L10.3969/j.issn.1005-9490.2016.04.023