一种批量FPGA远程并行智能升级的方案

郝天琪,孟立凡*,孙玉环(.中北大学电子测试技术国家重点实验室,太原03005;.中北大学仪器与电子学院,太原03005)

一种批量FPGA远程并行智能升级的方案

郝天琪1,孟立凡1*,孙玉环2

(1.中北大学电子测试技术国家重点实验室,太原030051;2.中北大学仪器与电子学院,太原030051)

针对存储阵列卡中批量FPGA手动逐个升级缓慢的问题,在不修改原有硬件的条件下,提出并成功实现了一种批量FPGA远程并行智能升级的方案。依托存储阵列卡中仅有的PCIE接口,各片FPGA以并发竞争的方式向控制主机提出升级数据读取请求并实时响应,解决了配置Flash手动串行编程效率低的难题。经过存储阵列卡板上远程调试证明,该方案可行,运行稳定可靠,且移植方便,是一种廉价又理想的远程并行智能升级方案。

FPGA;配置Flash;并发竞争;远程智能升级

随着大规模集成电路的高速发展,现场可编程门阵列FPGA(Field Programable Gate Array)在工业领域得到了广泛应用[1]。为了加快电子存储设备的研发进度,提高存储阵列卡的吞吐量,众多电子存储阵列卡使用了大量的FPGA代替传统的ASIC。在整机调试过程中,由于FPGA数量众多,固化配置逻辑极其耗时,给远程存储阵列卡逻辑更新和设备维护造成了困难。国内外对较多FPGA芯片的配置更新研究甚少,在解决此类难题时加入了微控制器、IP核或只能串行逐个更新,通用性差,不够灵活且移植困难[2,3]。因此,在不修改硬件板卡的前提下,利用存储阵列卡现有的PCIE接口和PCIE协议的强突发传输处理能力、高速传输特性对配置Flash[4]并行编程是一种理想方案。本文以SPI接口的NOR Flash为例,详细阐述了远程并行智能升级的原理和FPGA逻辑结构。

1 远程并行智能升级原理

远程并行智能升级系统包括两部分,远程服务站(Romote Server)和存储阵列(Storage Array)。远程服务站通过因特网将新的配置文件传到存储阵列卡中工控机IPC(Industrial Personal Computer)的内存上,接着触发FPGA升级信号,各片FPGA在收到升级触发信号后向IPC确认,接着FPGA对配置Flash进行擦除,再以并发竞争的方式向IPC请求配置数据并编程配置Flash芯片的指定区域,编程完成后回读配置Flash的更新区域,对比确认后再启动加载配置命令,在不掉电的情况下完成配置文件升级[5],如图1所示。由于PCIE传输速率高,NOR Flash的写入速度低,每完成一页的编程Flash都需要等待较长时间,所以各片FPGA彼此之间的影响并不大,多片FPGA可以同时进行升级,这样可以将升级配置时间由N个时间单位缩短为稍大于一个时间单位,大大提高了存储设备远程升级效率。

图1 远程并行智能升级示意图

2 远程并行智能升级FPGA逻辑结构

远程并行智能升级FPGA逻辑包括W rite_Read子模块和 BitLoad子模块,其结构如图 2所示。W rite_Read子模块的功能包括检查FPGA的连接状态、对指定区域的配置Flash进行擦除、编程和读取。BitLoad子模块的功能是当Flash编程完毕回读确认后从配置Flash加载FPGA的配置文件,这样FPGA在编程完毕后无需断电就可以启动新配置,有效保护了存储阵列卡中DDR等其它器件上的数据[6~8]。Top interface为上层控制接口,同PCIE寄存器连接,PCIE模块在此没有列出,它主要用于阵列卡数据高速传输。Bottom interface为底层接口,同Flash芯片连接。

图2 W rite_Read和BitLoad的结构

2.1W rite_Read模块

配置Flash读写子模块包括两条独立且互斥的通道,读通道和写通道。两条通道在上层是独立无联系的,下层通过MUX模块的选择与SpiSerdes模块连接,通道的选择由W rite_ReadENB控制,当W rite_ReadENB置位‘0'时,连接读通道,为‘1'时连接写通道。下面,由下至上分别介绍各个子模块的实现及其关系。

2.1.1STARTUPE2模块

SPI协议是同步通信协议,数据的传输依赖于同步时钟CCLK的边沿,因此需要准确控制CCLK的电平跳变。FPGA的SPI配置方式时钟CCLK为专用管脚,需要硬件原语模块STARTUPE2来管理CCLK。设计中SPI协议选用常见的模式3,即时钟极性CPOL=1,时钟相位CPHA=1。STARTUPE2的USERCLKO直接控制着 CCLK的输出,通过SpiSerdes模块的传输开始标志位启动USERCLKO,传输完成标志位延时拉高USERCLKO[9-10]。

2.1.2SpiSerdes模块

为了数据传输管理方便,我们将一个字节作为此模块的传输单位,用两个有限状态机ShiftCounter和ShiftDate组织字节内数据接收和发送。SpiSerdes包含两个移位寄存器组ShiftCounter和ShiftDate。Shift-Counter有9 bit,用于标识ShiftDate的传输状态,当ShiftDate传输完成后,保留一个时钟周期用于Shift-Date更新数据,其位数高于ShiftDate。ShiftCounter初始值为B“000000001”,ShiftDate每传输完一位,ShiftCounter循环右移一位,当数字‘1'再次回到LSB位时,标记一个字节传输完成,同时为下一个字节的传输做好了准备,如图3(a)所示。ShiftDate寄存器组的LSB和MSB分别连接至配置Flash的MISO和MOSI。当数据传输时,首先将ShiftDate寄存器组用待发送的数据初始化,然后在时钟的上升沿将MSB发往MOSI接口,同时将ShiftDate左移,在时钟的下降沿再将MISO填充到ShiftDate的LSB位,这样随着时钟的周期性循环,当ShiftCounter的位‘1'再次回到LSB,就完成了一个字节的发送和接收,如图3(b)所示。

图3 状态寄存器组循环右移示意图

完成一个字节的数据发送和接收后,将TransferDone置为高电平,再根据TransferStart的情况选择是否继续传输数据。需要注意的是在发送有效数据之前,SpiSerdes模块都要先发出一组空操作,以稳定SPI的同步时钟CCLK。

2.1.3MUX模块

配置Flash的读通道和写通道的切换由MUX模块来完成。当W rite_ReadB为低电平时MUX选择读数据通道与SpiSerdes连接,当W rite_ReadB为高电平时选择写数据通道与SpiSerdes连接,这样独立且互斥的读写通道可以有效降低因误操作导致Flash内容被篡改的可能性。读写通道的切换由时钟同步处理,避免了毛刺的产生。

2.1.4SpiFlashReader模块

配置Flash编程完毕后,检验配置文件已经全部正确写入的可靠方法就是读出本次更新的配置数据,再将读取的数据与写入的数据对比,确认无误后再从配置Flash加载更新后的配置文件。因此,SpiFlashReader模块对编程的完整性检验具有重要意义[11-12]。

SpiFlashReader以寄存器组DateBox移位的形式实现数据和命令传输的。DateBox有5个字节,当发送数据前需要发送读命令时,以[ReadCommand,32 bitsDate]的形式组织,比如Flash读通道选定后需要发送读数据命令和起始地址,就将读命令放在高字节,起始地址放在低4个字节。DateBox初始化后被赋予待发送的值,同时它的状态计数器Counter也被赋予待发送的字节数,当发送使能触发后,DateBox的高字节被送往SpiSerdes模块的数据发送接口,每传输完1个字节,DateBox左移1个字节,同时将SpiSerdes模块接收到的一个字节的数据填充到低字节,这样循环直到Counter减为0,就完成了读命令和起始地址的发送和接收。DateBox移位状态图4所示。

图4 DateBox寄存器组的移位示意图

起始地址发出后,就开始了数据接收的过程。DateBox每次接收完4个字节的数据,就向上层控制模块发出Ready信号,表明该模块接收端口数据有效,当收到应答信号ACK后继续读取下一组数据。在此过程中读取的地址随着Ready信号的跳变不断累加,直至接收完指定的数据长度才停止,最后将读完成状态信号置为高电平标识读过程已经完成。

2.1.5SpiFlashProgrammer模块

①编程模块子状态机设计

编程模块是远程智能升级的关键,SpiFlashProgrammer模块包含SendWords、PollStatus和Program-Pages 3个逐层嵌套的子状态机。PollStatus发送命令时调用SendWords状态机,ProgramPage在查询状态时调用PollStatus状态机,在传输配置数据时调用SendWords状态机,3个子状态机结构如图5所示。

图5 SendW ords、PollStatus和Program Pages状态机状态转移图

SendWords状态机是编程模块最底层的状态机,配置Flash的ID读取、擦除、编程都需要使用该状态机,它的传输单位是双字(DoubleWords)。进入该子状态机后,首先在PreSendWord的状态准备好一组待发送数据,然后进入Sendword状态,向SpiSerdes模块发送四个字节的编程命令或数据,每发送完成4个字节,Sendwords状态机就回到Pre-SendWord状态重新初始化发送器。当一组数据传输完毕后,有限状态机就转移到下一个指定的状态,若传输过程中长时间没有收到配置Flash的正确回应,状态机就会转移至传输超时状态,将错误指示信号拉至高电平,提前结束编程。

NOR Flash以页为最小编程块,每次编程的数据量为一页。由于Flash写入速度较慢,每次写入一页的数据之后需要等待,查询配置Flash是否完成本页的烧写,这就需要一个状态机PollStatus负责检查配置Flash的页编程状态。PollStatus状态机的结构与SendWords状态机相似,进入PrePollStatus之后不停地查询页写入状态,直至写入完成或写入超时。

每片Flash包括许多页,以页为单位编程NOR Flash需要准确组织页的大小和顺序,ProgramPages状态机能够自动累加编程地址,准时更新待编程数据,精确的控制页编程。当一页编程未完成时,ProgramPages持续调用Sendwords状态机,直至本页数据全部写入配置Flash,当本页编程完成时,调用PollStatus子状态机,以确认数据已经准确写入,之后再根据写地址判断是否需要编程下一页,编程全部完成后进入结束状态。

②编程模块更新配置Flash流程

配置Flash在编程前需要先检查其连接状态,通过读取设备的ID可以确认设备是否已经正确连接,Flash ID读取正确后就可以擦除其指定区域了,擦除完毕后才可以进行数据烧写。如果只需要检查配置Flash是否能够识别,只检查其ID就可以了,如图6所示。在检查设备ID、擦除或编程过程中,一旦出现Flash回应超时,状态机就会切换到到对应的错误指示状态,提前结束编程。编程过程中或编程顺利通过后,相应的状态指示信号也会置位,比如 Ready_BusyB,Done,Started,InitializeOK,Check IdOK,EraseOK,ProgramOK等,这些指示信号在调试和升级的过程中指明了编程模块的进度,对定位错误、加快调试进度有很大帮助。

图6 配置Flash编程流程

2.2BitLoad模块

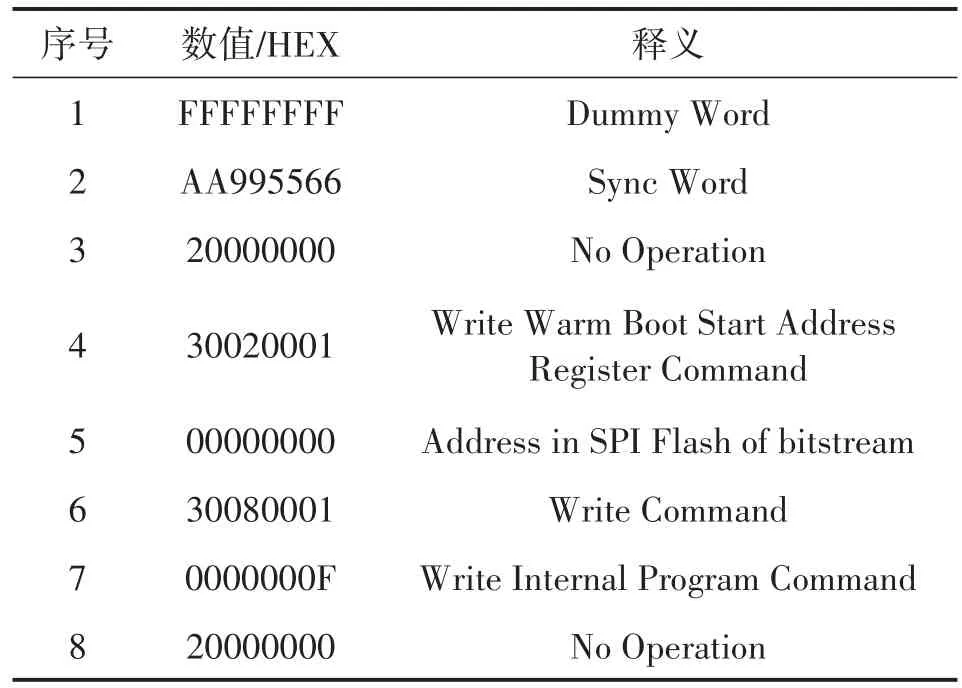

配置Flash编程完毕后,需要将FPGA的配置切换到更新后的版本,但是存储阵列卡又要求必须保护板卡中的DDR等辅助设备中的数据,不得断电,此时就需要BitLoad模块向FPGA内部配置寄存器发送命令,主动加载新的配置文件,这样就达到了FPGA在不掉电的情况下重新加载新配置文件的目标。ICAP命令的发送顺序及其含义如表1所示,更新后配置文件的起始地址根据具体环境有所不同。ICAP命令的字节内位序是LSB在前,使用时需要转换,比如X“30020001”转换后变为X“0C400080”。BitLoad的触发需要延时确认,避免了毛刺、尖峰信号的误触发。

表1 ICAP命令发送顺序

3 逻辑功能仿真

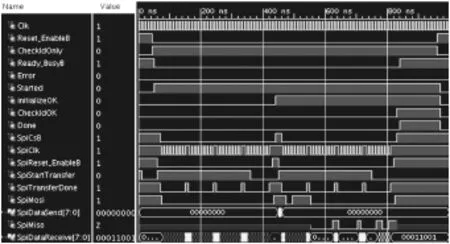

为了便于理解各模块之间的时序关系,下面以读取设备的ID为例对FPGA远程智能升级逻辑进行功能仿真。首先选择写通道,将Reset_EnableB置为低电平使能写通道,同时将Check IdOnly信号拉高,Started变为高电平,Flash片选信号SpiCsB有效,进入写模式状态,SpiFlashProgrammer模块开始初始化配置Flash,initializeOK跳变为高电平之后,开始发送读ID命令X“9F”。SpiMosi和SpiMiso两条信号线显示了SPI串行总线发送和接收数据时数据高低电平的变化。从此时起TranserDone第一个脉冲说明读ID命令已经下发,第2、第3个脉冲和随后的高电平表示FPGA已经完成了3个字节的接收,X“01”、X“02”、X“19”,这就是读出的Flash的ID。配置Flash ID读取完成后,Check IdOK状态信号被拉高,随后Done信号也被拉高,Error维持低电平,说明读ID已经顺利完成,如图7所示。FPGA逻辑仿真正确后,将各模块连接到FPGA的PCIE寄存器接口上上板验证,顺利完成了批量FPGA的远程并行升级。

图7 读取设备ID功能仿真

4 结论

本文介绍了一种批量FPGA远程并行智能升级的方案并对编程模块进行了仿真,该方案逻辑功能由VHDL/Verilog编程实现,不需要额外添加微控制器或其它辅助升级设备,在存储阵列卡只留有PCIE接口的条件下,用少量的LUT和原语模块顺利实现了FPGA的远程并行智能升级,大大缩短了存储设备整机升级时间,提高了存储设备整机调试和升级维护的效率。经过完备的功能仿真和上板远程调试证明,远程智能升级方案可移植性强,可靠性高,维护简单,适用于Xilinx K7、V7、S7等系列主流芯片。

[1] 刘迎辉,朱恒静,张大宇,等.Xilinx低等级FPGA高可靠应用的升级试验方法研究[J].电子产品可靠性与环境试验,2014,32(1):11-17.

[2] 刘永恩,王俊芳.FPGA远程升级技术的分析与实现[J].专题技术与工程应用,2012,42(9):48-50.

[3] 李强,罗超,夏威,等.FPGA远程更新系统[J].仪表技术与传感器,2014(7):72-74.

[4] 唐磊.基于FPGA的USB、Flash控制器设计[D].北京:北京交通大学,2010.

[5] 丁丁,汤晓斌,陈立德,等.基于μClinux的FPGA远程更新系统的实现[J].电子技术应用,2014,40(3):6-8.

[6] Xilinx Corp.Platform Flash In-System Programmable Configuration PROMs[EB/OL].USA:Xilinx,Product Specification,May 2012:19.

[7] 任勇峰,张凯华,程海亮.基于FPGA的高速数据采集存储系统设计[J].电子器件,2015,38(1):135-139.

[8] 李加超,孟令军,周之丽,等.基于FPGA的断电续传存储系统的设计与实现[J].电子器件,2015,38(3):588-591.

[9] 孙云峰,段哲民.基于微处理器系统的FPGA在线配置方法[J].微处理机,2008,10(5):29-31.

[10]连猛,丑修建,李庆,等.基于FPGA和DSP的数据采集与压缩系统[J].电子器件,2015,38(1):130-134.

[11]徐晶晶,陈帅.SSD系统中多级FPGA在线升级电路的设计与实现[J].信息技术教学与研究,2013(72):116-117.

[12]逄锦昊,苏涛,杨涛,等.基于FPGA的多路高速数据传输同步时延测量系统[J].电子器件,2015,38(2):447-451.

郝天琪(1992-),男,汉族,山西河津人,中北大学硕士研究生,主要研究方向嵌入式系统及现代测试技术,384047315@ qq.com;

孟立凡(1956-),女,汉族,中北大学教授,主要研究方向为现代传感理论与技术。1996年12月至1998年1月日本千叶大学高级访问学者。主编有《传感器原理及技术》高等学校教材,撰写论文二十余篇,其中一级论文、核心期刊论文、EI收录论文十余篇。发明专利一项。主持完成十余项省部级课题,menglifan@nuc.edu.cn。

A Scheme of FPGA Remote Parallel Intelligent Upgrade

HAO Tianqi1,MENG Lifan1*,SUN Yuhuan2

(1.National Key Laboratory forElectronic Measurement Technology,North Uniυersity of China,Taiyuan 030051,China;2.College of Instrumentand Electric Technology,North Unitυersity ofChina,Taiyuan 030051,China)

In order to solve the problem that storage array cards upgrade too slow inmanual one by another,a perfectmethod was proposed and successfully implemented on FPGA withoutmodifying the storage array cards.Relying on the storage array card's PCIE interface,each piece of FPGA proposes read request in concurrent competitive way,and respond to the controller in real time.Storage array card onboard debugging shows that the scheme proposed is feasible,reliable,and easy to transplant,and it isan inexpensive and ideal scheme.

FPGA;deploy Flash;concurrentcompetition;remote intelligentupgrade

TP336

A

1005-9490(2016)04-0820-05

2015-08-09修改日期:2015-09-09

EEACC:6120B;721010.3969/j.issn.1005-9490.2016.04.014