基于FPGA的数字频率计设计

北方工业大学 王亚峰 陈 昊 张 军

基于FPGA的数字频率计设计

北方工业大学王亚峰陈昊张军

本设计采用的测频技术是相检宽带测频技术,这种测量方法消除了传统测频、测时仪器存在的±1个数的计数误差,测量精度较传统仪器显著提高,具有很广阔的应用前景。本文详述了该技术的基本原理和具体实现。

相检宽带测频技术;FPGA;MCU

1 总体设计

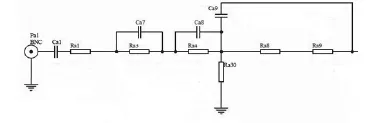

被测信号通过阻抗变换模块进行阻抗匹配,经过高/低滤波器切换,使得高频信号通过高频滤波器,低频信号通过低频滤波器。而后低频信号和高频信号分别在对应的放大电路上进行信号放大,放大后的信号经过高频比较和方波整形得到可测方波,期间高/低滤波器切换由FPGA进行控制。

随着被测信号的频率升高,仪器的相移分辨力会逐渐减小,因此在本设计中,为增加仪器的测量范围,当被测信号频率较高时,信号会通过分频电路进行分频。被测信号分为两种进行处理:当被测信号频率低于标频频率时,信号将首先进行放大整形,之后74LS153双向电子开关生成信号并送入FLEX 10K芯片中;当被测信号频率高于标频频率时,信号将接入mb506进行分频与整形,而后经由双向电子开关74LS153,最后输入到FLEX 10K中,这里采用的分频是64分频。随后标频信号和被测信号进入FLEX 10K芯片,经芯片内部的相位重合点脉冲产生电路,产生两路信号的最小公倍数周期和最大公因子频率,即产生相位重合。

由标频信号和被测信号相互作用产生的最小公倍数周期信号和STM32单片机中预先设置的参考门信号同时由FLEX 10K自带的D触发器的CP端输入,实际测量闸门时间信号将在D触发器的输出端产生,并用此闸门信号来控制计数器的开启和关闭,随后单片机通过存储和计算计数器在一次测量周期里所计的数,得出被测信号频率。计算结果交由LCD液晶显示屏显示。本设计中的实际测量门,严格容纳了标频的整数倍和被测信号的最小公倍数周期,而且此处的最小公倍数周期又严格容纳了品表信号的整数倍和被测出信号周期。因此在得到实际测量门时间时,消除了技术误差,保证了测量了准确性。总体设计框图如图1所示。

2 硬件设计

2.1阻抗切换电路设计

通过电容和继电器调节输入阻抗以实现阻抗匹配。电路如图2所示。

图2 电路图

2.2高频比较电路

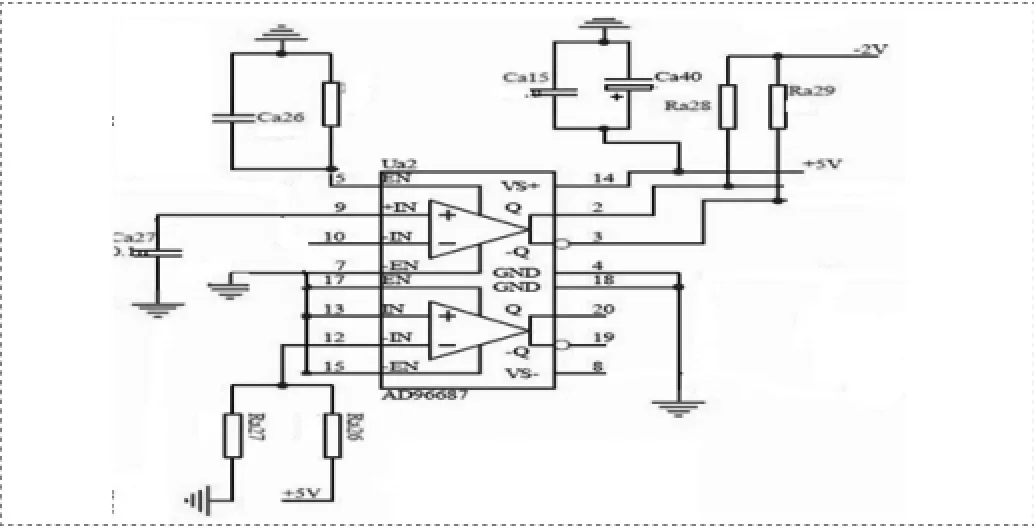

高频比较电路采用AD96687比较器,电路如图3所示。

图3 高频比较电路

3 同步计数

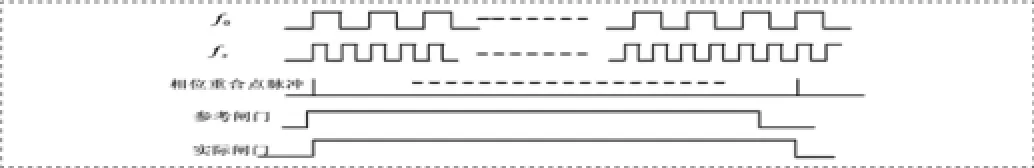

本文所采用的相检宽带测频技术是一种新型的信号检测技术,是基于相位重合点和最大公因子频率等概念逐渐发展而来。其基本原理是利用两个周期性信号的相位重合点和参考门信号产生新的闸门信号,此闸门信号的时间长度与参考闸门时间的长度基本一致。我们注意到此闸门信号终止时刻和闸门信号起始时刻严格对应于两个相位重合点,如果用利用这种闸门时间,进行信号频率的测量,可以避免一半频率测量仪器工作中存在的士1的计数误差,使频率测量精度大大提高。

图4

图4所示为闸门产生波形,在实际闸门时间里分别对标频及被测信号计数,设得到的计数值分别为N0和NX,则被测信号的频率值为:

4 结语

本设计采用了相检宽带测频技术,巧妙地把高测量精度和宽测量范围结合在一起。另外本文采用的频率标准是内置高稳压控晶振,相对传统仪器的外接原子频标,成本大大降低。另外考虑带仪器的老化问题,本文增加了标频校准功能,保证了在使用老化率相对较高的高稳压控晶振情况下,保证仪器的测量精度。本文中的技术部分和重合点计算都是在FPGA芯片内部编程实现,在降低了系统复杂程度和成本的同时,提高了系统可靠性。

[1]朱新华,杨润生,等.基于ARM的数据采集系统设计[N].电子测量与仪器学报,2008.

[2]ALAN V.OPPENHEIM.信号与系统[M].西安:西安交通大学出版社,1997.

[3]元秋奇.数字图像处理学[M].北京:电子工业出版社,2000.

[4]吴运昌.模拟电子线路基础[M].广州:华南理工大学出版社,2004.

[5]阎石.数字电子技术基础[M].北京:高等教育出版社,1997.

[6]张晓丽.数据结构与算法[M].北京:机械工业出版社,2002.