高速伪随机码调制激光测距雷达电子学系统设计

徐恒,刘金涛,贺岩

(1.中国海洋大学 山东 青岛 266100;2.中国科学院上海光学精密机械研究所 上海 201800)

高速伪随机码调制激光测距雷达电子学系统设计

徐恒1,刘金涛1,贺岩2

(1.中国海洋大学 山东 青岛266100;2.中国科学院上海光学精密机械研究所 上海201800)

针对采用光子计数的高速伪随机码激光测距,开发了基于高性能FPGA的电子学系统。该系统将伪随机码调制信号发送、码元数据接收、累加运算、互相关运算、距离信息提取及网络通信等功能集成在单个Altera公司的Stratix IV系列FPGA芯片中。系统中采用10阶M序列伪随机码,伪随机码发送和接收速率为1 GHz,周期为10 kHz。接收的码元经过10次累加和阈值比较后,利用1 024个并行的同或逻辑实现互相关运算。互相关运算和距离信息提取的重复频率为1 kHz。理想条件下的测试结果表明,系统达到了设计要求。

激光测距雷达;伪随机码调制;光子计数;FPGA

伪随机码激光测距对激光峰值功率的要求低,在远距离测量时无需大功率脉冲激光器,可以大大降低整个系统的技术难度,并且系统的体积、功耗、稳定性等也可优化[1]。因此伪随机码激光测距有广泛的应用前景[2-5]。

常规的伪随机码激光测距系统因为激光功率低,所以探测距离有限。与本论文相关的伪随机码激光测距雷达,为了增加探测距离,首先采用光放大器提高激光发射功率;其次,采用单光子探测器和光子计数技术提高信号探测能力。

经过光放大的伪随机码调制激光脉冲由发射望远镜输出。目标的反射信号由接收望远镜接收,通过单光子探测器将光信号转化为电脉冲信号输出,再由光子计数器中脉冲幅度甄别电路对电脉冲进行判决,高于阈值的为码元1,低于阈值的为码元0。甄别后的码元序列与原始伪随机码序列做互相关运算,根据相关峰值位置可提取目标的距离信息[6]。

根据伪随机码测距原理,高调制速率可提高距离分辨率,从而提高测距精度;同时,由于调制速率的提高,伪随机码序列发送时间得到压缩,可有效提高测距的重复频率,进而实现高空间分辨率的激光测距测绘[7]。

针对上述应用,开发了相应的电子学系统,该系统以高性能的FPGA(现场可编程逻辑阵列)为核心,采用1 GHz伪随机码调制速率和10 kHz的测量频率,测量结果进行10次累加,最终以1 kHz频率输出距离结果。本文将从系统的组成和参数设计等方面进行详细论述,并给出系统的有效性测试结果。

1 硬件总体设计

伪随机码测距激光雷达电子学系统采用以高性能FPGA为核心的设计。系统主要完成两个功能:一是输出高速伪随机码LVDS信号,作为激光调制信号;二是甄别单光子探测器的输出信号,并转换成LVDS码元输入到FPGA中进行运算处理。

本文设计中,FPGA选用Altera公司的Stratix IV系列芯片。Stratix IV芯片内部有充足的存储单元和乘加运算单元,可以满足数据缓存和处理的需要。同时Stratix IV芯片的管脚支持1.6 GHz的LVDS逻辑,满足1 GHz伪随机码调制速率的要求。

Stratix IV芯片输出的伪随机码LVDS信号直接驱动激光调制器。 高速比较器选用 Analog Devices公司的ADCMP605芯片,其输入带宽为500 MHz,单端信号输入,LVDS电平输出。测距测量结果通过百兆以太网传输到上位计算机。Stratix IV芯片外接的并行Flash作为程序存储器,外接的静态RAM作为TCP/IP协议的数据缓冲区。

图1 伪随机码测距激光雷达电子学系统硬件框图Fig.1 The electronics system hardware diagram of laser ranging radar based on pseudorandom modulation

2 FPGA逻辑设计

FPGA逻辑设计主要包括伪随机码发送模块、码元数据接收模块、累加运算模块、互相关运算模块、距离信息提取模块、时序控制模块、SRAM控制模块、FLASH控制模块和数据缓冲模块等。本文系统中,伪随机码的输出、码元的输入、数据处理、网络通信等所有功能都在单片Stratix IV芯片中实现。为了达到10 kHz的测量频率,上述模块采用Verilog HDL语言编程。FPGA中还嵌入一个Nios II软核用于实现TCP/IP协议。

图2 FPGA逻辑总体设计框图Fig.2 General block diagram of FPGA logic design

2.1伪随机码发送模块

伪随机码发送模块由两部分组成:伪随机码存储部分和LVDS发送部分。伪随机码存储部分使用FPGA中的存储单元构成8 bit宽度的RAM。本设计中采用10阶M序列伪随机码,码长1 024 bit,使用Matlab软件程序生成。LVDS发送部分采用Altera公司altlvds TX IP核,并设置成8:1的并行转串行模式。

图2中的时序控制模块按照10 kHz的频率以125 MHz的速率从伪随机码存储部分读出发送的码元,同时写入altlvds TX IP核,控制altlvds TX IP核发送出1 GHz的伪随机码。

图3 伪随机码发送模块原理图Fig.3 The schematic diagram of pseudorandom code transmitter module

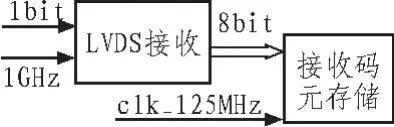

2.2码元接收模块

码元接收模块也由两部分组成:LVDS接收部分和接收码元存储部分。LVDS接收部分采用Altera公司altlvds RX IP核,并设置成1:8的串行转并行模式。接收码元存储部分使用FPGA中的存储单元构成8bit宽度的RAM。

图1中高速比较器输出的是LVDS电平的“0”和“1”码元,LVDS接收部分以1 GHz的速率进行采样,转化为8 bit数据后以125 MHz的速率写入到RAM中。本文系统设计采样长度为5 120 bit,因为RAM深度需设置为2的整数次幂,所以接收码元存储设为8bit×1024。5 120 bit的采样所需时间约为5 μs。

图4 码元数据接收原理图Fig.4 The schematic diagram of code receiver module

2.3累加运算模块

当光信号强度在单光子的量级时,光子到达光电探测器的速率遵循泊松分布。如果将单次接收到的码元同发送的伪随机码直接做互相关,互相关峰值的不确定性会较大。因此,将10次接收的码元做累加后,再进行互相关运算。

为了满足10 kHz重复频率的指标,利用FPGA并行处理的特点,将累加模块设计为8路并行累加子模块。如图5所示,接收码元存储部分中的数据依次分配给8个累加模块,累加的结果写入互相关运算模块数据缓冲中。

为了给互相关运算留出尽可能多的时间,采用2个互相关运算模块数据缓冲。即前一次10组接收码元的累加结果写入互相关运算模块数据缓冲1中,下一次累加结果写入互相关运算模块数据缓冲2中。

累加子模块的频率是40 MHz,一次接收的5 120 bit码元可在约16 μs的时间内累加完成。又因为累加运算模块和互相关运算模块设计为同步进行的,所以在整个工作周期中,基本可以忽略累加运算的时间。

图5 累加运算模块结构图Fig.5 The block diagram of accumulation module

2.4互相关运算模块

本设计中互相关运算必须在1 ms内完成。如果采用乘法运算,则很难实现。如图6所示,累加后的数据先与一个阈值相比较,大于该阈值的为“1”,小于该阈值的为“0”。根据激光雷达方程和实际系统参数,可以估算出接收的光子数,由此给出阈值大小。因为发送和接收的码元都是“0”和“1”,所以可用“同或逻辑”代替乘法运算。

因为发送的伪随机码长度为1 024 bit,本设计中采用了1024路并行的“同或逻辑”运算单元。同或逻辑运算频率为50 MHz,5 120 bit码元的互相关运算可以在约80 μs的时间内完成。

如果接收的码元与发送的伪随机码序列完全匹配,则互相关运算结果为1 024,需要11 bit位宽数据进行存储。因为5 120 bit光子数据共包含有4 096个相关位置,所以互相关运算模块缓冲大小设置为11bit×4096。

图6 互相关运算模块原理图Fig.6 The block diagram of correlation module

2.5距离信息提取模块

距离信息提取模块利用“冒泡”算法,求出互相关运算的最大值,及最大值的位置。本设计中,给出了前4个最大值及其位置,用于上位计算机综合判断目标的距离。

3 系统测试

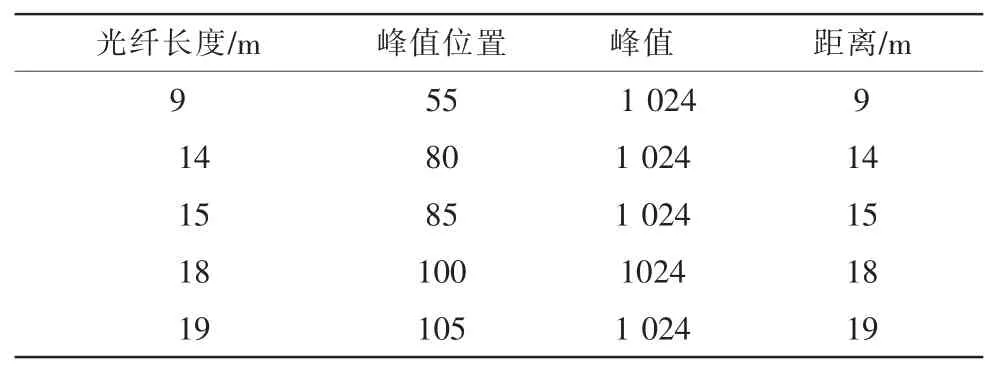

开发完成后,在理想条件下对系统性能进行了测试。测试时使用1.25G的SFP(Small Formfactor Pluggable)模块取代激光调制器、激光器、光放大器和单光子探测器,采用不同长度的光纤做延时。

由表1的结果可以看出,9 m光纤测试结果峰值位置55 与14 m光纤测试结果峰值位置80差值为25,由此得到峰值位置每单位对应光纤长度为0.2 m。以9 m光纤峰值位置为测量基准,当峰值位置为85,距离为:9+(85-55)×0.2=15 m。同理可求得其他两组峰值位置对应距离分别为18 m、19 m。根据峰值位置求得的距离与实际距离(即光纤长度)相同。

由测试结果可看出,互相关运算峰值均为1 024,这是因为伪随机码调制激光脉冲经光纤延时,光损耗比较小,光的传输接近理想状态,接收码元序列与原始伪随机码序列完全匹配。

4 结 论

针对采用光子计数的伪随机码激光测距,开发了基于单片高性能FPGA的电子学系统。该系统设计将伪随机码调制信号发送、码元数据接收、累加运算、互相关运算及距离信息提取等功能集成在一个FPGA芯片中。理想条件下的测试结果表明,系统达到了设计要求。目前,该系统已经成功应用到实际的测量中[8]。

表1 测试结果Tab.1 The test results

本文设计中,主要应用了FPGA中的存储单元和逻辑单元资源。目前存储单元使用了8%,逻辑单元使用了13%。同时,互相关运算的模块工作时钟频率为50 MHz,而Altera公司的Stratix IV系列芯片可以稳定工作在200 MHz以上。因此,本文中系统的测量周期、测量距离等关键性能还有很大的提升空间[9-11]。

[1]杨芳,张鑫,贺岩,等.基于高速伪随机码调制和光子计数激光测距技术 [J].中国激光,2013,40(2):02080001-1-02080001-5.

[2]Machol J L.Comparison of the pseudorandom noise code and pulsed direct-detection lidars for atmospheric probing[J]. Applied Optics,1997,36(24):6021-6023.

[3]Krichel N J,McCarthy A,Buller G S.Resolving range ambiguity in a photon counting depth imager operating at kilometer distances[J].Optics Express,2010,18(9):9192-9206.

[4]Rall J A R,Abshire J B,Manizade S S.Lidar measurements of clouds and aaerosols using AlGaAs lasers modulated with pseudorandom codes[C]//IEEE Lasers and Electro-Optics Society,1992:206-207.

[5]Norman D M,Gardner C S.Satellite laser ranging using pseudonoise code modulated laser diodes[J].Applied Optics,1988,27(17):3650-3655.

[6]杨馥,贺岩,周田华,等.基于伪随机码调制和单光子计数的星载测高计仿真[J].光学学报,2009,29(1):21-26.

[7]温宗平.伪随机码激光探测技术研究[J].红外与激光工程,1996,25(3):34-40.

[8]杨芳,张鑫,贺岩,等.基于不同伪随机码调制的光纤激光测距系统[J].中国激光,2014,41(6):06140031.

[9]沿君莹,田学民,陈洁萌.脉冲激光测距系统及其算法研究[J].电子设计工程,2015(11):99-101.

[10]陈守韦,邹庆秋.机载脉冲式激光测距机接放电路的设计[J].电子科技,2015(2):131-133,138.

[11]张海峰,孟文东,吴志波,等.单向激光测距及其测量试验[J].中国激光,2013(3):202-208.

Electronics system design for laser ranging radar based on high speed pseudorandom modulation technique

XU Heng1,LIU Jin-tao1,HE Yan2

(1.Ocean University of China,Qingdao 266100,China;2.Shanghai Institute of Optics and Fine Mechanics,Shanghai 201800,China)

In the paper an electronics system for laser ranging radar based on high speed pseudorandom modulation and photon counting techniques is presented.All functions,such as pseudorandom code transmission,code reception,accumulation,correlation,distance calculation and network communication,were integrated into one high-performance FPGA chip of Altera Stratix IV.Ten order M sequence pseudorandom code was used in the design.The transmitting and receiving repeat frequency was 10 kHz with 1GHz code rate.The received codes were accumulated by 10 times and changed to 1 bit binary codes by compared with a settled threshold.The correlation was done in 1ms by using 1024 parallel Exclusive-or operations.The test results under ideal conditions showed the affectivity of the developed system.

range laser radar;pseudorandom modulation;photon counting;FPGA

TP302;TP332.2

A

1674-6236(2016)01-0149-03

2015-04-22稿件编号:201504252

中国科学院支撑技术项目(61501010304)

徐 恒(1990—),男,山东临沂人,硕士研究生。研究方向:基于FPGA的高速信号采集和处理。