一种低电压无采样保持运放14bit,100MS/s流水线型模数转换器的65nm CMOS工艺实现

张新龙,薛 盼,姜 培

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

一种低电压无采样保持运放14bit,100MS/s流水线型模数转换器的65nm CMOS工艺实现

张新龙,薛盼,姜培

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

设计了一款低电压实现的14bit,100MS/s流水线型模数转换器(Pipelined ADC),该ADC前端采用无采样保持运放结构来降低功耗和减小噪声,减少了第一级采样网络孔径误差和非线性电荷注入的影响.通过选取合适的输入采样电容容值解决了kT/C噪声和电容不匹配的问题,并设计了符合系统要求的低电压高速高增益运放.该模数转换器同时也包含了带隙基准、分布时钟产生电路、参考电压和共模电压缓冲器等电路模块.芯片采用TSMC 65nm GP 1P9M CMOS工艺实现,面积为3.2mm2(包含PAD).测试结果表明,当采样率为20MS/s, 输入信号频率为1.869MHz时,信噪比(SNR)为66.40dB, 信噪失真比(SNDR)为65.21dB, 无杂散动态范围(SFDR)为73.44dB,有效位数(ENOB)为10.54bit.电源电压为1.2V,整个模数转换器的总功耗为 260mW.

低电压; 流水线型模数转换器; 无采样保持运放结构; 高速; 高精度

高速高精度模数转换器是现代移动无线通信系统[1]和光纤通信系统的重要部件,如无线基站接收机和光时域反射仪(Optical Time Domain Reflectometer, OTDR).随着工艺技术的提高和这些系统的严格要求,高性能、低消耗的模数转换器一直是研究的重点.在众多的模数转换器架构中,流水线型模数转换器在同时要求高速高精度的应用场合中是最主要的选择[2],同时只有相对较低的功耗.

已报道的高性能流水线型模数转换器通常使用较为昂贵的BiCMOS工艺实现[3-6],且BiCMOS工艺一般不利于系统集成,而CMOS工艺由于其低消耗[2]和适合于系统集成等优点,在实现流水线型模数转换器设计方面是更为常用的工艺.另外,随着CMOS晶体管沟道长度的不断减小,CMOS器件可以在更高的频率上获得增益[7].但是,在主流的深亚微米CMOS工艺中,限制流水线型模数转换器性能的许多问题变得越来越严重,其中不断减小的晶体管本征增益和持续降低的电源电压是两个主要因素[8].

为了实现低消耗的流水线型模数转换器,众多技术被用来降低流水线型模数转换器的系统功耗和芯片面积,例如移除前端采样保持运放[1-2,8-11]、运放共享技术[9,12]和开关运放技术[13].作为流水线型模数转换器的第一个模块,采样保持运放通常有大量的功耗,同时还会引入相应的噪声和失真,这些都会降低流水线型模数转换器的系统性能.因此,移除前端采样保持运放不仅消除了其功耗,而且去除了其引入的噪声[1]和失真.但是移除前端采样保持运放会引入孔径误差,这一问题需要仔细对待,因为孔径误差会限制流水线型模数转换器的最大输入信号频率和最大采样率[12],并且在没有前端缓冲器的情况下,移除前端采样保持运放也会引入非线性电荷注入问题[1,11],这一问题会降低流水线型模数转换器的静态和动态性能.运放共享技术和开关运放技术主要运用在低中速、低中精度流水模数转换器中[12],用来降低功耗.但是在高速高精度流水线型模数转换器的实现中,这些技术由于会引入记忆效应和限制采样率等问题而很少被采用.

随着工艺技术的不断提高和CMOS晶体管沟道长度的持续减小,晶体管本征增益gmro变得越来越小,这会严重限制流水线型模数转换器的线性度.在没有数字校准技术的辅助帮助下,高速高精度流水线型模数转换器中使用的高增益运算跨导放大器(Operational Transconductance Amplifier, OTA)变得越来越难实现.在本文中,运用增益自举技术来提高OTA的增益.

另一方面,主流深亚微米工艺中主要针对数字电路设计的电源电压持续不断地降低,而针对一定的动态范围,开关电容电路的功耗反比于电源电压[2],所以得到一个相对较大的输入动态范围,同时保持相对较低的功耗在低电源电压下越来越难实现.另外在低电压情况下,实现具有较大输出摆幅的OTA也是一个较困难的问题.

目前,高速高精度流水线模数转换器是国内各大公司、研究机构争相研究的热点,本文重点探讨低压实现高精度要求和高速情况下移除采样保持运放带来的问题以及相应的解决方法.其中移除采样保持运放用来降低功耗和噪声,重点研究了由此带来的孔径误差和非线性电荷注入的影响.在低电源电压下,运用增益自举技术设计了满足系统要求的高速高增益OTA.

1 流水线型模数转换器系统架构

图1显示了本文设计实现的流水线型模数转换器的系统架构,移除了前端采样保持运放,没有使用数字校准技术和运放共享技术.采用多位的前端在以往的论文中被证明可以提高流水线型模数转换器的线性度[1,14]和节省功耗[1],但是会增加电路设计的复杂度.同时考虑功耗、线性度和降低电路设计复杂度,本文设计的流水线型模数转换器的第一级采用2.5bit,后级仍然使用每级2.5bit结构.

流水线型模数转换器前三级的比例缩小因子为4,后几级保持相同.第一级的采样电容大小为3.2 pF, 这一取值满足电容不匹配的要求和14bit噪声的要求,最后一级是2bit的Flash ADC.本文设计的流水线型模数转换器同时包含了带隙基准源、分布时钟产生、参考电压和共模电压产生电路以及相应的缓冲器、阈值电压产生电路、全局偏置和Scan-Chain电路,其中Scan-Chain电路用来调节每级OTA的参考电流大小,方便测试芯片.OTA的基本架构是两级全差分.对于本文设计的流水线型模数转换器,电源电压为1.2V,输入动态范围为1.2Vp-p.

2 电路实现

2.1输入端采样网络

作为流水线型模数转换器的第一个模块,采样保持运放复制采样得到的输入信号,传递给第一级,所以相同的复制量可以被第一级的乘法数模转换器(Multiplying DAC, MDAC)和子模数转换器(SubADC)同时采样.但是采样保持运放通常有大量的功耗,并且会增加信号路径上的噪声,更严重的是会限制流水线型模数转换器的线性度[1-2,9-10,12].其中一个消除采样保持运放缺点的方法是完全移除前端采样保持运放,继而使得两个不同的采样网络同时采样输入信号.可是由此引入的孔径误差问题会限制流水线型模数转换器的最大输入信号频率[9],孔径误差是由于第一级的MDAC和subADC之间不同的采样网络采样输入信号时的RC延迟不匹配造成的.在本文中,同时在电路级和版图级匹配输入采样网络来减弱孔径误差的影响.在电路级,采样开关共享同一个自举电容Cbootstrap,如图2所示,使得所有的输入级采样开关拥有相同的栅源电压VGS.另外,考虑两个不同网络的采样电容的大小,不断迭代优化两个不同采样网络的采样开关晶体管的W/L,来获得近似相等的RC延迟,孔径误差的问题可以在电路级减弱到最小.在版图级,提参后仿真表明,直到输入信号频率达到500MHz,孔径误差的影响仍然在容许的误差范围内.

在文献[1,11]中讨论的,在没有前端缓冲器的情况下,移除前端采样保持运放会引入非线性电荷注入问题,这一问题会严重恶化流水线型模数转换器的静态和动态性能.类似于文献[1],本文采用增加一个放电相位ΦR来解决非线性电荷注入问题,如图3所示.当ΦR为高时,采样电容的顶极板接输出共模电压Vocm,底极板接输入共模电压Vicm,来清除在前一个放大相位上寄存在采样电容上的电荷.

2.2高速高增益OTA

标准TSMC 65nm工艺的电源电压是1.2V,因此在如此低的电源电压下实现具有大的输出摆幅的高速高增益OTA是一件非常困难的事.图4(见第46页)显示了本文设计的流水线型模数转换器使用的OTA的主体架构,其基本架构是两级全差分,其中第一级为使用增益自举技术的折叠共源共栅结构来尽可能地提高增益,类似于文献[15];第二级是Class-A输出级来获得大的摆幅.OTA的补偿方式为Cascode补偿,这种补偿方式可以获得比密勒补偿方法更大的带宽,但是这种补偿方式对于寄生比较敏感,所以OTA的版图需要细心布局来减小寄生参数对于OTA带宽的影响.后仿真表明,系统第一级OTA具有如下性能指标: 低频增益为97dB,带宽为1.08GHz,相应的相位裕度为69°.

开关电容共模反馈(Switch-Capacitor CMFB, SC CMFB)电路用来设定OTA的输出共模电压,如图5所示.额外增加一股电流路径可以较容易地控制在低电压情况下的输出共模稳定电压,如图4所示.

两级全差分OTA的相应辅助运放P-Booster和N-Booster电路如图6(a)和(b)所示.由于辅助运放也是全差分结构,所以也需要相应的共模反馈电路,辅助运放采用稳定输入共模电压的形式来实现稳定辅助运放的工作点.如图4所示,辅助运放在主运放中工作于单位增益负反馈形式,所以稳定了输入共模电压,也就相应地稳定了辅助运放的输出共模电压.

2.3动态比较器

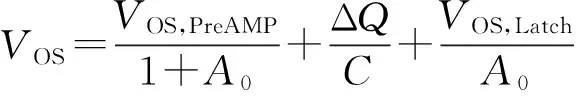

第一级subADC的主体结构如图7所示,其采样开关与第一级MDAC的采样开关共享同一个自举电容.动态比较器包含3个部分: 前置预放大器、锁存器和RS触发器,其电路图如图8所示,前置预放大器的带宽满足建立速度的要求.失调取消技术基于文献[16]的输入失调存储,经过失调取消后的输入参考失调电压为:

(1)

其中VOS,PreAMP和A0分别为预放大器的失调和增益,ΔQ为开关S1和S2电荷注入在电容Coffset上的不匹配差量,VOS,Latch为锁存器的失调.从公式(1)可知,为了减小输入参考失调电压,预放大器的增益应该尽量的大,本文设计的前置预放大器的增益为30dB.

图9显示了系统主要时钟相位安排.基于时钟相位的安排,比较器失调取消的动作原理是: 当ΦSEE为低时,预放大器的失调存储在电容Coffset上;当ΦS为低时,采样完成;当ΦC为高时,比较器将采样得到的输入信号与阈值电压做比较,同时减去失调电压;当ΦL为高时,锁存器锁存比较得到的结果.

2.4参考电压、共模电压和阈值电压产生电路

在低电源电压情况下,参考电压需要一直保持稳定和足够的精度,也就是说,它们的产生路径需要保证足够的精确,并且相应的缓冲器的增益带宽积(Gain Bandwidth Product, GBW)需要足够大来驱动大的、变化着的电容负载.为了减小正负参考电压的电容负载,所有电压均有相应的缓冲器,包括参考电压、共模电压和阈值电压,如图10(见第48页)所示.图11(a)和(b)(见第48页)分别显示了正负参考电压的缓冲器电路图,其他电压缓冲器的结构类似于正负参考电压缓冲器,只是具有不同的性能指标.

在正负参考电压缓冲器内部增加了一些开关,这些开关可以通过Scan-Chain电路实现芯片内外参考电压的切换,方便调试芯片.

3 测试结果和分析

本文设计的流水线型模数转换器采用TSMC 65nm GP 1P9M CMOS工艺实现,芯片总面积为 3.2mm2(包含PADs),包含流水线型模数转换器核和所有的外围电路,图12显示了芯片照片图.

图13显示了采样率为20MS/s,输入信号频率为1.869MHz的测试FFT频谱图,相应的信噪比(SNR)为66.40dB, 信噪失真比(SNDR)为65.21dB, 无杂散动态范围(SFDR)为73.44dB,有效位数(ENOB)为10.54bit;图14显示了采样率为100MS/s,输入信号频率为12.494MHz的测试FFT频谱图,相应的SNR,SNDR,SFDR,ENOB分别为54.11dB,53.87dB,68.21dB,8.66bit. 表1为本文设计的流水线型模数转换器与部分参考文献的性能对比.

从测试结果和性能对比可以看出,测试结果还待于提高.从测试可以得知,导致ENOB较低的原因主要有3个: (1) 第一级采样电容3.2 pF的容值仍然相对较小,电容的匹配度对于14位精度要求来说仍较差;(2) 时钟网络的Jitter较大,尤其是当时钟频率增大时;(3) 电源PAD和电源线有待于重新规划,尤其是需要走大电流的电源PAD和电源线,增加大电流电源的PAD数和增加其线宽,将有助于改善这个问题.

4 总 结

本文描述了一款低电压14bit,100MS/s采样率的流水线型模数转换器的设计与实现,为了降低功耗和提高模数转换器的线性度,采用了前端无采样保持运放架构,并且讨论大量的电路细节.整个模数转换器由六级2.5位组成,后接2位的Flash.采用TSMC 65nm GP 1P9M CMOS工艺实现,整个模数转换器面积为3.2mm2(包含PAD),电源电压为1.2V,消耗总功耗为260mW.

[1]DEVARAJAN S, SINGER L, KELLY D,etal. A 16-bit 125MS/s 385mW 78.7dB SNR CMOS Pipelined ADC [J].IEEEJSolid-StateCircuits, 2009,44(12): 3305-3313.

[2]CHIU Y, GRAY P R, NIKOLIC B. A 14-b 12-MS/s CMOS Pipelined ADC with over 100-dB SFDR [J].IEEEJSolid-StateCircuits, 2004,39(12): 2139-2151.

[3]ALI A M A, DILLON C, SNEED R,etal. A 14-bit 125-MS/s IF/RF sampling Pipelined ADC with 100dB SFDR and 50 fs jitter [J].IEEEJSolid-StateCircuits, 2006,41(8): 1846-1855.

[4]ALI A M A, MORGAN A, DILLON C,etal. A 16-b 250-MS/s IF-sampling Pipelined A/D converter with background calibration[C]∥IEEE International Solid-State Circuits Conference, 2010. San Francisco, USA: IEEE Press, 2010: 292-293.

[5]PAYNE R, CORSI M, SMITH D,etal. A 16-bit 100 to 160MS/s SiGe BiCMOS Pipelined ADC with 100dB FS SFDR [J].IEEEJSolid-StateCircuits, 2010,45(12): 2613-2622.

[6]SETTERBERG B, POULTON K, RAY S,etal. A 14-b 2.5-GS/s 8-way-interleaved Pipelined ADC with background calibration and digital dynamic linearity correction[C]∥IEEE International Solid-State Circuits Conference, 2013. San Francisco, USA: IEEE Press, 2013: 466-467.

[7]WILLY M C. Analog Design Essential [M]. Netherlands: Springer, 2006.

[8]HAFIZ O A, WANG X Y, HURST P J,etal. Immediate calibration of operational amplifier gain error in pipelined ADCs using extended correlated double sampling [J].IEEEJSolid-StateCircuits, 2013,48(3): 749-759.

[9]LEE B G, TSANG R M. A 10-bit 50MS/s Pipelined ADC with capacitor-sharing and variable-gm opamp [J].IEEEJSolid-StateCircuits, 2009,44(3): 883-890.

[10]BRUNSILIUS J, SIRAGUSA E, KOSIC S,etal. A 16-b 80-MS/s 100mW 77.6dB SNR CMOS Pipelined ADC[C]∥IEEE International Solid-State Circuits Conference, 2011. San Francisco, USA: IEEE Press, 2011: 186-188.

[11]ALI A M A, DINC H, BHORASKAR P,etal. A 14-b 1-GS/s RF sampling Pipelined ADC with background calibration[C]∥IEEE International Solid-State Circuits Conference, 2014. San Francisco, USA: IEEE Press, 2014: 482-484.

[12]LEE B G, MIN B M, MANGANARO G,etal. A 14-b 100-MS/s Pipelined ADC with a merged SHA and first MDAC [J].IEEEJSolid-StateCircuits, 2008,43(12): 2613-2619.

[13]FANG B N, WU J T. A 10-bit 300-MS/s Pipelined ADC with digital calibration and digital bias generation [J].IEEEJSolid-StateCircuits, 2013,48(3): 670-683.

[14]YANG W, KELLY D, MEHR I,etal. A 3-V 340-mW 14-b 75-Msample/s CMOS ADC with 85-dB SFDR at Nyquist input [J].IEEEJSolid-StateCircuits, 2001,36(12): 1931-1936.

[15]BULT K, GEELEN G. A fast-settling CMOS opamp for SC circuits with 90-dB DC gain [J].IEEEJSolid-StateCircuits, 1990,25(6): 1379-1384.

[16]RAZAVI B, WOOLEY B. Design techniques for high-speed, high resolution comparators [J].IEEEJSolid-StateCircuits, 1992,27(12): 1916-1926.

Design of a Low-Voltage SHA-less 14bit, 100MS/s Pipelined ADC in 65 nm CMOS

ZHANG Xinlong, XUE Pan, CHIANG Patrick

(State Key Laboratory of ASIC and System,Fudan University, Shanghai 201203, China)

A low-voltage 14bit, 100MS/s Pipelined analog-to-digital converter (ADC) is presented. A SHA-less architecture is adopted to decrease power and noise. The front-end sampling network is carefully considered to minimize the effect of aperture errors and nonlinear charge kickback. And the size of the input sampling capacitor is selected in terms of kT/C noise and capacitor mismatch. High speed and high gain OTAs are elaborately designed in low power supply. The ADC also includes a bandgap, distributed clock generator, reference and common voltage buffers, etc. The ADC is implemented in TSMC 65nm GP 1P9M CMOS process, the area is 3.2mm2(includes PADs). The chip achieves 66.40dB SNR, 65.21dB SNDR, 73.44dB SFDR, and 10.54bit ENOB at a 20MS/s sampling rate with a 1.869MHz input signal. The ADC consumes 260mW with 1.2V power supply.

low-voltage; Pipelined Analog-to-Digital Converter; SHA-less architecture; high speed; high resolution

0427-7104(2016)01-0043-08

2015-04-17

张新龙(1988—),男,硕士研究生;姜培,男,教授,通讯联系人,E-mail: pchiang@eecs.oregonstate.edu.

TN 432

A