NBTI机制下运算放大器的性能退化分析及其可靠性设计*

花修春,李小进,石艳玲

(华东师范大学信息科学技术学院,上海200241)

NBTI机制下运算放大器的性能退化分析及其可靠性设计*

花修春,李小进*,石艳玲

(华东师范大学信息科学技术学院,上海200241)

随着CMOS器件尺寸的不断缩小,集成电路设计阶段的可靠性问题变得愈加重要,NBTI效应作为重要的可靠性问题之一得到了大量的研究,并从电路级对其提出了改进。采用等效电路模型表征NBTI退化对模拟电路的影响,研究了两级运算放大器在NBTI效应影响下电路参数的退化,分析并确定了影响传统两级运算放大器性能的关键器件。在此基础上,对传统运放结构进行改进,引入反馈,使-3 dB带宽的退化量由27%降到了1%左右,从而减小NBTI退化对电路性能的影响。

模拟电路;可靠性;SPICE仿真;NBTI效应;可靠性设计

自摩尔定律诞生以来,半导体技术已经按照该规律发展了半个世纪。2013年国际半导体技术发展指导委员会(ITRS)预测,到2017年,器件特征尺寸将达到7 nm[1]。集成电路可靠性依赖于晶体管的工艺参数和工作条件,随着器件尺寸的缩小,电路集成度不断提高,沿MOSFET沟道与穿越沟道方向的电场强度不断增加,最终导致器件与电路性能参数随时间不断退化。该退化的引入机制之一为热载流子效应(HCI),主要表现为载流子有效迁移率μeff的降低;在P-MOSFET中称为负偏压温度不稳定性(NBTI),主要表现为阈值电压绝对值|ΔVth|的增加[2],以及迁移率、漏电流和跨导的退化[3]。

NBTI效应发生于对P-MOSFET栅极施加负偏压条件下,该效应早在1966年由Yoshio Miura与Yasuo Matukura等人[4]提出。科研人员对数字电路和模拟电路中NBTI效应引起的性能退化进行了大量研究[5-8],对运算放大器性能退化也进行了广泛的研究,并从工艺及电路上提出了减小NBTI效应的方法[9-11]。相比于数字电路,不管输入如何变化,模拟电路中P-MOSFET栅极会受到负的直流偏置电压的连续作用[8],使得模拟电路中的PMOS管受NBTI的影响更加严重。

项目来源:国家自然科学基金项目(61204038);上海市自然科学基金项目(14ZR1412000)

收稿日期:2015-06-24修改日期:2015-07-29

本文从可靠性设计流程及电路结构上对传统两级运放进行改进,以提高其抗NBTI的能力。

1 反应-扩散模型及可靠性仿真设计流程

1.1反应-扩散(RD)模型

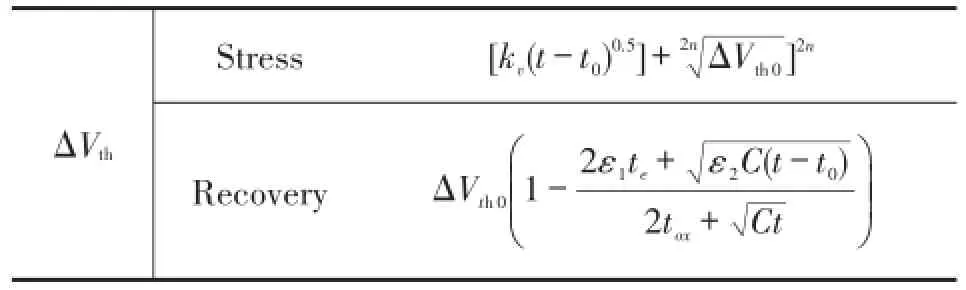

各种NBTI模型中,最受业界接受的是反应-扩散模型(Reaction-Diffusion model)[12-15],简称RD模型。模型描述随着器件尺寸的缩小,栅极氧化层厚度不断减小,在P-MOSFET栅极施加的负偏压使栅极氧化层的电场强度大大增加。这会导致反型层中的空穴与Si/SiO2界面处的Si-H键发生反应,导致Si-H键的断裂,进而在界面处产生硅的悬挂键,形成受主型陷阱电荷。断裂的氢受到电场的作用向栅极漂移,当移除栅极偏压后,部分氢又会返回界面钝化硅悬挂键,最终导致阈值电压随时间发生退化。提出的模型如表1[2]所示。

表1 P-MOSFET阈值电压ΔVth的退化模型 单位:mV

该模型分为两个阶段,第1阶段为栅极施加应力时阈值电压退化的阶段,即表中Stress部分;第2阶段为当栅极负偏压被移除之后,向栅氧中扩散的部分的氢返回界面钝化硅悬挂键的阶段,即表中Recovery部分。其中ΔVth为阈值电压退化量,ΔVth0为初始阈值电压,t0为初始时刻,(t-t0)是退化发生的时间,tox为栅氧厚度,ε1与ε2为反向扩散系数,Kv为与栅极电压有关的系数,n、te与C均为系数。由于NBTI效应也随着工作温度的变化而发生变化,使得该效应更加复杂,严重者会使器件甚至电路失效。工作在不同区域完整的模型参数详见文献[2]。

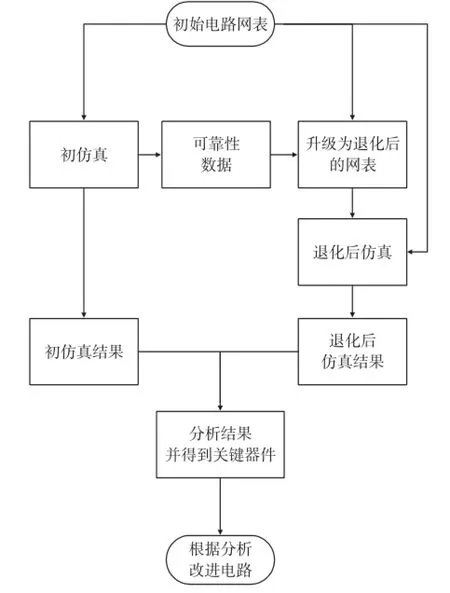

1.2考虑器件可靠性的SPICE模拟电路仿真设计流程

传统的模拟电路设计主要包括电路结构的选择与器件参数的设计,本文采用文献[13]提出的考虑器件可靠性的SPICE仿真设计流程研究两级运放的可靠性设计。设计流程如图1所示。

图1 考虑可靠性的模拟电路设计流程

设计流程分为3大步,首先是初仿真,初仿真即所有的P-MOSFETs均未发生NBTI退化时的仿真。初仿真有两个目的,首先是得到电路未退化的各性能参数,其次是得到电路中各P-MOSFETs栅极所受激励的情况,将栅极的激励情况代入表1的退化模型计算各P-MOSFETs阈值电压随时间的退化曲线。第2步是后仿真,将第1步计算所得晶体管阈值电压的退化量代入电路进行仿真,得到发生退化时的电路参数,并与初仿真比较得出电路参数随时间的退化情况,最终获得电路中的关键器件。最后根据分析结果对关键器件所在的模块进行改进以提高其抗NBTI的能力。

2 NBTI效应对模拟电路的影响

2.1试验方法

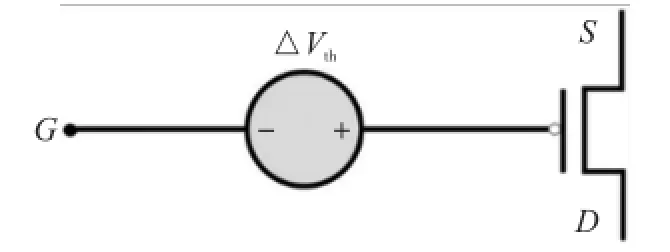

本文采用失效等效电路模型来表征NBTI的退化[16],如图2所示。

图2 NBTI失效等效电路模型

对本文所研究两级运算放大器电路中的P-MOSFETs进行图2所示的等效替换,然后按照图1所示可靠性设计流程分析NBTI效应对两级运放性能参数的影响,并提出可靠性设计。

2.2NBTI效应对运算放大器的影响

运算放大器Op-Amp(Operational Amplifier,简称运放)是模拟集成电路中一个基本组成模块。传统的两级运放由差分放大器输入级、增益级(如共源极)和输出缓冲级组成。

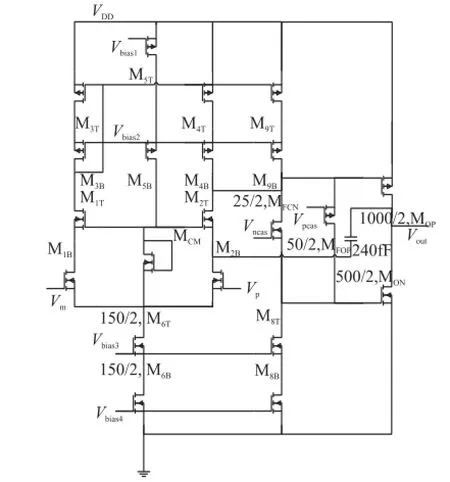

本文所研究电路为带输出缓冲级并经过间接反馈补偿的运算放大器,如图3所示。第一级采用共源共栅结构差分放大器以提高增益,第2级为推挽放大器,其增益取决于所驱动的负载电阻,输出缓冲级仍采用推挽放大器以提高运放的输出摆幅。电源电压VDD=1 V,未标注PMOS的宽长比为100/2,未标注NMOS的宽长比为50/2。设计晶体管 M3T、M4T、M9T、M8T所在支路流过的电流为10 μA,设计晶体管MOP所在支路,即输出级流过电流为100 μA,运放正常工作时消耗功率为140 μW。该两级运放中共有10 个P-MOSFETs,MFCP与 MOP2个PMOS晶体管的源栅电压设计为150 mV,其余8个PMOS晶体管的源栅电压均设计为 350 mV。(Vbias1~Vbias4)均为偏置电路产生的偏置电压,限于篇幅,文中未画出偏置电路。

图3 带输出缓冲级的CMOS两级运算放大器

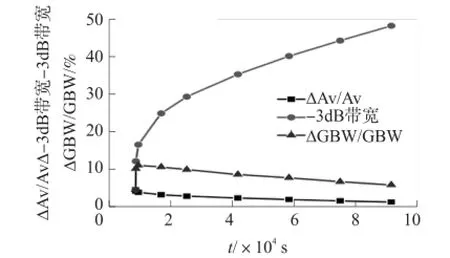

首先经过初仿真得到运放初始参数与各PMOS管栅极激励,然后根据模型分别计算10个PMOS晶体管的退化参数并代入电路,得到运放各参数随时间的退化曲线,如图4~图6所示。

图4 两级运放增益Av、-3 dB带宽、增益带宽积GBW随时间退化的仿真曲线

图5 两级运放共模抑制比CMRR随时间退化的仿真曲线

图6 两级运放相位裕度PM随时间退化的仿真曲线

图4~图6表明运放各参数受NBTI效应的影响发生不同程度的退化。随退化时间的推移,运放的低频增益出现小幅降低,-3 dB带宽大幅增加,增益带宽积在退化初始有大约8%的退化而后又逐渐降低。其中,运放-3 dB带宽退化最为明显,在105s时该退化量接近50%,如图4圆形点线图所示。对于该两级运放,共模抑制比取决于差分输入级,随着NBTI退化时间的增加,共模抑制比的退化量逐渐增加,相位裕度在初始的减小之后逐渐增加,但这两个参数的退化均不显著,在105s时的退化量分别为-4%和0.4%。

由图1所示可靠性设计流程,为得到运放中的关键器件,对运放中P-MOSFETs进行分类:M5T栅极由Vbias1偏置为第1类,M3T、M4T、M9T栅极相连发生同等NBTI退化为第2类,M3B、M5B、M4B、M9B栅极同时受Vbias2偏置发生同等退化为第3类,MFCP栅极由Vpcas偏置为第4类,MOP栅极连接在MFCP源极为第5类。

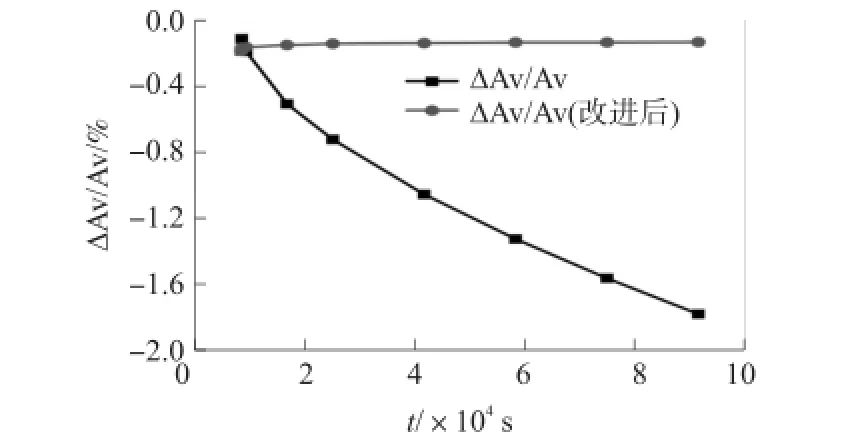

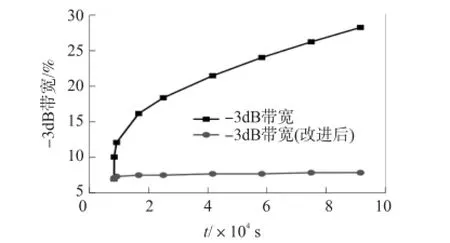

对以上5类管子进行退化仿真,结果表明M5T的退化对该运放的影响最为显著,MFCP发生退化对电路的影响次之,M3T、M4T、M9T发生退化对电路的影响最小,所以确定在该两级运放中M5T为关键器件[13]。图8~图10中黑色方形点线图表示当电路中M5T发生退化时电路参数的退化曲线,曲线表明运放各参数退化幅度较大,其中-3 dB带宽在105s后退化量达到27%之多。为验证M5T为关键器件,分析当M5T没有发生退化而其余MOSFETs发生退化时电路性能的退化。结果表明电路各参数退化量显著减少,其中退化最严重的-3 dB带宽在在105s后退化量为11%左右,明显小于M5T退化对其27%退化量的影响。

3 考虑器件可靠性的模拟电路设计

运用图1所示可靠性设计流程对运放中的关键器件进行改进。由于设计关键器件M5T中流过的电流为10 μA,考虑对M5T作如图7所示的改进,以简单电流镜代替M5T,在M5T′漏极串联60 kΩ电阻R以维持M5T镜像的电流为10 μA。当M5T与M5T'发生退化时,由于它们阈值电压绝对值增大,引起支路电流的减小,导致电阻R上的压降降低,从而使M5T的源栅电压Vsg增加,引起支路电流的增加。即电阻R在电路中起到负反馈的作用。

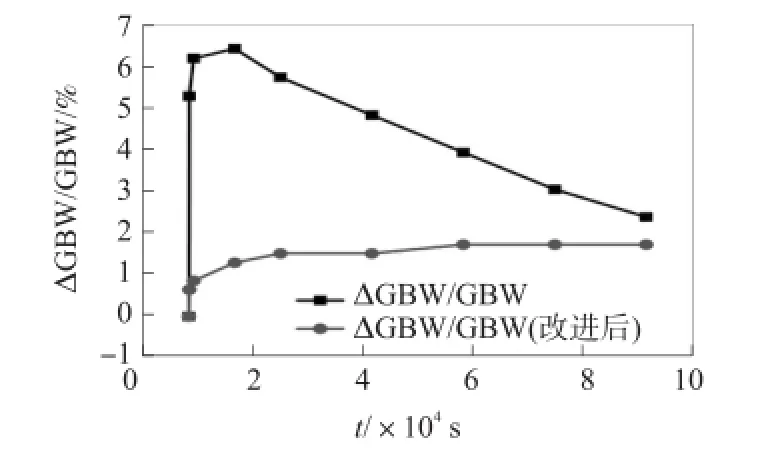

改进后当M5T所在电流镜发生退化时运放的退化曲线如图8~图10中红色圆形点线图所示。与原运放相比,改进后的电路受NBTI效应的影响显著降低,电路稳定性显著提高。如在退化时间到达105s时,退化最严重的-3 dB带宽的退化量由27%降到了1%左右,其它参数如低频增益、增益带宽积、共模抑制比和相位裕度等参数也得到了优化,表明电流镜发生退化对该运放影响很小,运放抗NBTI效应的能力大幅提高。这是由于相对于单管负载,电流镜负载具有更强的抗NBTI退化能力。

但该改进也带来了电路面积与功耗的增加,如增加的 M5T′与 60 kΩ电阻使运放的功耗增加了7.14%。同时,增加的电阻R在实际制备中会有偏差,考虑实际电阻具有±20%的偏差时,再次分析电路的退化。结果表明,除了-3 dB带宽出现±10%左右的退化,其余参数均无明显退化,与原电路相比,改进后电路的抗NBTI能力得到了提高。

这也表明在实际电路设计中需折衷考虑电路可靠性、面积与功耗。

图8 对M5T改进前后低频增益Av随时间的退化曲线

图9 对M5T改进前后两级运放-3 dB带宽随时间的退化曲线

图10 对M5T改进前后两级运放增益带宽积GBW随时间的退化曲线

4 总结

本文采用等效电路模型表征NBTI退化对电路的影响,并采用考虑器件可靠性的SPICE仿真设计流程研究了经过间接补偿的两级运算放大器受NBTI影响时发生的退化,得到电路中的关键器件M5T,引入反馈从电路结构上对M5T所在电路模块进行改进,使该两级运放的抗NBTI能力显著提升。

[1] International Technology Roadmap for Semiconductors 2013 Edition Irc Overview[R].2013.

[2] Wang W,Reddy V,Krishnan A T,et al.Compact Modeling and Simulation of Circuit Reliability for 65-nm CMOS Technology[J].IEEE Transactions on Device and Materials Reliability,2007,7(4):509-517.

[3] SchroderD K.Negative Bias Temperature Instability:What Do We Understand?[J].Microelectronics Reliability,2006,47(6):841-852.

[4] Yoshio M,Yasuo M.Investigation of Silicon-Silicon Dioxide Interface Using MOS Structure[J].J Appl Phys,1966,5(2):180.

[5] SchroderD K,Babcock J A.Negative Bias Temperature Instability:Road to Cross in Deep Submicron Silicon Semiconductor Manufacturing[J].J Appl Phys,2003,94(1):1-17.

[6] Reddy V,Carulli J,Krishnan A,et al.Impact of Negative Bias Temperature Instability on Product Parametric Drift[Z].International Conference on Recent Trends in Information,Telecommunication and Computing.2004:148-155.

[7] Lin Y,Li X,Shi Y,et al.Modeling and Simulation for NBTI-Considered Path Delay Prediction in Logical Circuit[Z].2014 International Workshop on Junction Technology(IWJT),2014:1-4.

[8] JhaN K,ReddyP S,Sharma D K,et al.NBTI Degradation and Its Impact for Analog Circuit Reliability[J].IEEE Transactions on Devices,2005,52(12):2609-2615.

[9] Hellwege H,Taddiken M,Peters D,et al.Analog Behavioral Modeling for Age-Dependent Degradation of Complex Analog Circuits [Z].Mixed Design of Integrated Circuits&Systems(MIXDES),2014 Proceedings of the 21st International Conference,2014:317-322.

[10]Menchaca R,Mahmoodi H.Impact of Transistor Aging Effects on Sense Amplifier Reliability in Nano-Scale CMOS[Z].2013 13th International Symposium on Quality Electronic Design(ISQED). 2012:342-346.

[11]Chang W,Luo J,Qi Y,et al.Reliability and Failure Aanalysis in Designing a Typical Operation Amplifier[Z].2010 17th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits(IPFA),2010:1-4.

[12]Alam M A,Kufluoglu H,Varghese D,et al.A Comprehensive Model of PMOS NBTI Degradation:Recent Progress[J].Micraelectronics Reliability,2005,45(1):71-81.

[13]周晓明,夏炎.NBTI效应及其对集成电路设计的影响[J].电子器件,2007,30(2):407-410.

[14]Jeppson K O,Svensson C M.Negative Bias Stress of MOS Devices at High Electric Fields and Degradation of MNOS Devices[J]. Journal of Applied Physics,1977,48(5):2004-2014.

[15]Ogawa S,Shiono N.Generalized Diffusion-Reaction Model for the Low Field Charge Build Up Instability at the Si-SiO2 Interface [J].Physical Review:B,Condensed Matter,1995,51(7):4218-4230.

[16]Yan B,Qin J,Dai J,et al.Reliability Simulation and Circuit-Failure Analysis in Analog and Mixed-Signal Applications[J].IEEE Transactions on Devices and Materials Reliability,2009,9(3):339-347.

花修春(1991-),男,汉族,江苏徐州人,华东师范大学微电子学与固体电子学硕士研究生,研究方向为半导体器件及电路可靠性设计,15102179019@163.com;

李小进(1978-),男,汉族,陕西人,华东师范大学微电子专业副教授,主要从事集成电路设计和建模,xjli@ee.ecnu.edu.cn;

石艳玲(1969-),汉族,华东师范大学微电子专业教授、博导,主要从事VLSI技术核心器件、模型及应用研究。承担国家及上海市研究课题近10项,在国内外核心刊物上发表论文逾40篇,SCI检索5篇,ylshi@ee.ecnu.edu.cn。

Analysis of Operational Amplifier Performance Degradation under NBTI Mechanisim and Its Reliable Design*

HUA Xiuchun,LI Xiaojin*,SHI Yanling

(School of Information Science and Technology,East China Normal University,Shanghai 200241,China)

With the scaling-down of CMOS device,reliability become increasingly significant in the stage of integratedcircuit design.NBTI effect has received lots of researches as one of the key reliability problems,and some improvement methods has been put forward from the circuit level.Afailure-equivalent model for NBTI degradation on the circuit has been proposed.Degradation affected by NBTI of two-stage operational amplifierhas beenstudied,we analyze and identify the key components of the traditional two-stage operational amplifier.Based on this,the structure of the conventional operational amplifier is improved by the introduction of feedback.The degradation of-3 dB bandwidth is optimized from 27%to about 1%,thereby the NBTI effect on conventional operational amplifier is reduced.

analog circuit;reliability;SPICE simulation;NBTI effects;reliable design

TN721.2

A

1005-9490(2016)03-0591-05

EEACC:1220;0170N10.3969/j.issn.1005-9490.2016.03.018