共源极电感对SiC MOSFET开关损耗影响的研究

董泽政,吴新科,盛 况,张军明

(浙江大学电气工程学院,杭州310027)

共源极电感对SiC MOSFET开关损耗影响的研究

董泽政,吴新科,盛况,张军明

(浙江大学电气工程学院,杭州310027)

共源极电感同时存在于功率MOSFET的功率回路和门极驱动回路中,影响器件的开关特性和开关损耗。共源极电感的影响将随着器件开关速度和开关频率的提高而显得更为严重。碳化硅(SiC)MOSFET相对于硅器件的材料优势使其可以实现更快速的开关过程,共源极电感的影响更加需要考虑。首先分析了现有功率开关损耗测量方法的优劣,然后选用一种通过测量结温升和热阻的方法来测量SiC MOSFET的开关损耗,最后搭建了一台输出功率1 kW、输出电压800 V的全碳化硅Boost样机,从100 kHz到500 kHz进行实验验证。实验结果表明,当不含共源极电感时SiC MOSFET的开通损耗、关断损耗均有所减小。

共源极电感;开关损耗;碳化硅(SiC)MOSFET

引言

近年来,随着宽禁带器件的不断发展,碳化硅基MOSFET在电机驱动、光伏逆变器等场合得到了广泛研究[1-2]。碳化硅器件相比传统的硅基器件,具有较小的结电容和很高的开关速度,导致回路中极高的开关速度di/dt及dv/dt。因此,回路寄生参数对于器件的应力、损耗和EMI干扰的影响需要认真对待。寄生参数中的共源极电感会使器件开关速度减慢,从而对器件的开关损耗产生影响。

回路寄生参数对于器件开关特性的影响主要包括器件的开关速度(di/dt、dv/dt)、器件的开关时间,电压电流应力以及开关损耗。文献[3]中分析了主功率回路电感LDS、门极回路电感LGS以及共源极电感LSS对于CoolMOS开关特性的影响,认为LDS主要影响开关时的振荡和器件总的电压电流应力,而LSS主要影响开关损耗;文献[4]通过改变电路中SiC MOSFET源端封装引脚长度研究了共源极电感对于SiC MOSFET开关损耗值的影响,表明器件的开通和关断损耗值均随着共源极电感的增大而增加;文献[5,6]也得到了类似的结论;文献[7]也分析了寄生电感对于SiC MOSFET的开关特性影响,通过在DBC板上额外串入一段3.15 nH的共源极电感,使用电流互感器测量源极电流,进行双脉冲实验,得出的结论是共源极电感会增加SiC 基MOSFET的开通损耗,而对于关断损耗几乎无影响。

以上文献中均是采用双脉冲电路,直接测量MOSFET的漏源电压和电流,然后将电压和电流乘积积分后得到器件的开关损耗。这种直接测量电压电流计算损耗的方法简单易行,而且非常直观,但是存在一定的不足[8]:(1)测量电路只能测量器件外部的漏极或者源极电流,由于器件寄生电容的存在,实际开通过程中流过芯片沟道内部的电流包含漏极电流和电容CDS的放电电流两部分[9],因此开通过程中实际损耗在器件内部的能量大于测量波形乘积的积分值,关断时实际损耗在器件内部的能量小于测量波形乘积的积分值。(2)测量电流时电路必然需要串入一定的测量元件 (同轴电阻或者电流互感器),必然会改变电路布局,带入额外的寄生电感值。

本文针对该方法存在的不足,选用了一种通过测量芯片结温升和芯片热阻然后计算得到芯片损耗的方法来研究共源极电感对于SiC MOSFET开关损耗的影响。在该实验方法的基础上设计了1台1 kW/800 V输出的全碳化硅Boost电路样机进行实验分析。

1 实验原理及损耗分析

1.1损耗分析

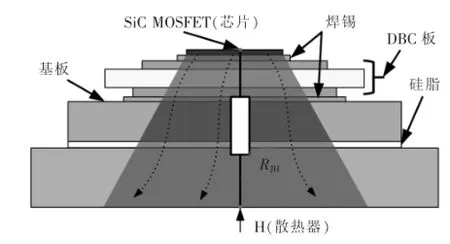

图1中给出了SiC芯片与散热器的空间物理结构。本文关注的是共源极电感对于SiC MOSFET开关损耗的影响,通过测量电路样机的热阻和实际电路开关工作的芯片温升间接得到器件损耗[11]。以Boost电路为例进行分析。

图1 SiC芯片与散热器的空间物理结构Fig.1 Physical structure from SiC chip to heatsick

当Boost电路持续工作至稳定状态,芯片结温也趋于稳定。此时测量芯片中心至散热器的结温差,则芯片内部的总损耗值为

式中:ΔTj为芯片结温与散热器温度差值;RJH为芯片到散热器等效热阻值。

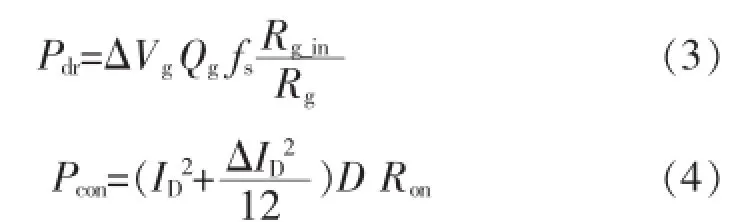

芯片总损耗Pchip分成芯片的驱动损耗、导通损耗和开关损耗,即

式中:Pdr为芯片内部门极电阻上驱动损耗;Pcon为导通损耗;Psw为开关损耗,其中

式中:ΔVg为门极正反电压之差;Qg为门极电荷总量;fs为器件开关频率;Rg为门极回路总电阻值;Rg_in为器件内部门极电阻值;ID为电感电流平均值;ΔID为电感电流峰一峰值;D为器件开关管导通时间的占空比;Ron为开关管的导通电阻。

1.2开通和关断的损耗区分

为了能够区分损耗分析中的开通和关断损耗,本文采用文献[9]中的实验方法进行分析。

第1组实验:使开关管工作在连续导通模式,硬开通和硬关断,开关损耗表示为

第2组为参照实验:使开关管工作在零电压开通,而保持关断时的电压、电流与第1组相同,此时得到的开关损耗全部为关断损耗值,开关损耗表示为

式中:Esw_1、Esw_2分别为第1组实验和第2组实验的器件总开关损耗值;Eon和Eoff分别对应开通损耗和关断损耗;Eoff_2为第2组实验的关断损耗。

两组实验器件关断时的电压和电流完全相同,两组实验的关断损耗值也相等,即

式中,Eoff_1为第1组实验的关断损耗。则硬开关开通损耗为

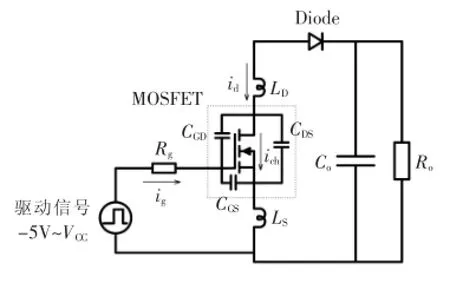

图2 共源寄生回路的电感示意Fig.2 Schematic of common source inductance in the loop

图2为实验中MOSFET寄生共源电感在回路中的示意简图。由于普通的MOSFET器件封装中,驱动和功率共用源端,造成了共源电感。共源极电感对器件的开关过程是不利的,一方面它会加剧开关过程的电压电流振荡,另一方面它会减慢开关过程增加开关损耗。本文主要针对共源极电感对开关损耗的影响进行研究,所以先不考虑其对于开关过程振荡的影响。当开关回路包含共源极电感时,开关过程中电流的变化率会降低,这是由于共源极电感使得门极电压和电流变化率之间存在负反馈关系,表示为

式中:Vgs为门极电压;Ls为共源电感值;id为外部测到的漏源间电流,当id较大的时候,did/dt约等于dich/dt。从式(9)可以看出,随着Vgs的增加,did/ dt减小,即dich/dt减少,开关时间增加。另一方面,漏源电压的变化是通过结电容的充放电实现,其主要过程存在Miller平台,使得充放电电流变化率很小,所以共源极电感对漏源电压的变化率影响很小。

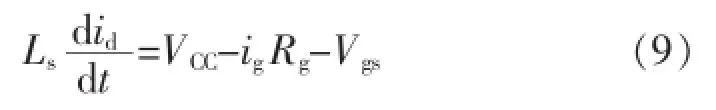

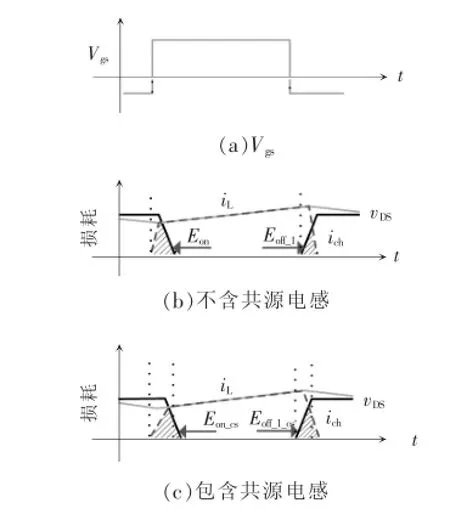

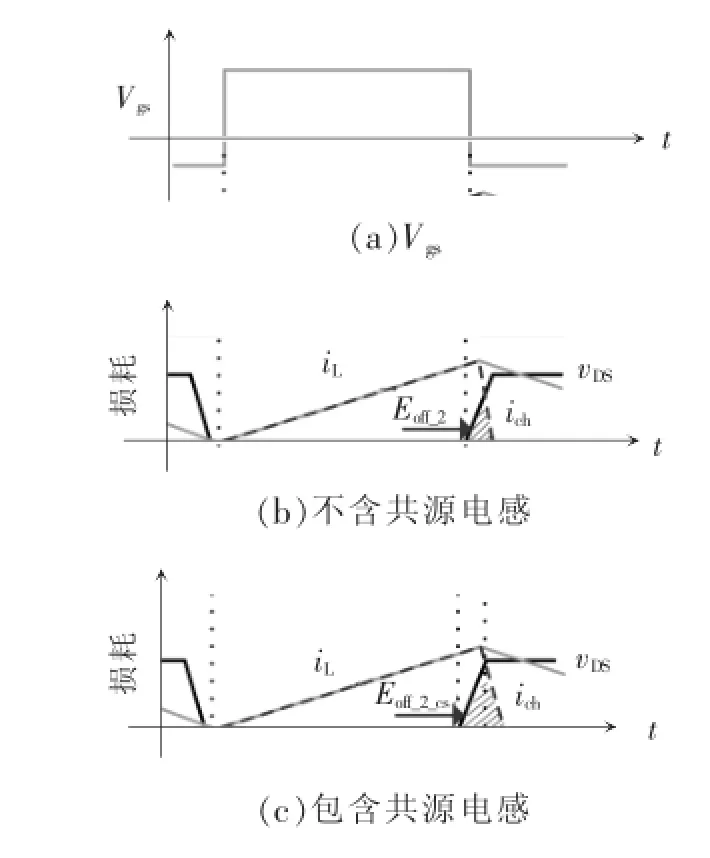

图3、图4分别为实验中MOSFET硬开关和软开关条件下的波形对比。由图可见,图中Eon_cs和E-off_1_cs分别为包含共源电感的硬开关电路的开通和关断损耗。共源极电感的引入增加了开通和关断时间,增加了开通和关断损耗。

图3 包含和不包含共源极电感的硬开关损耗波形Fig.3 Waveforms of loss under hard-switching with and without CSI

图4 ZVS软开关损耗波形Fig.4 Waveforms of loss under ZVS soft-switching

1.3热阻值测量

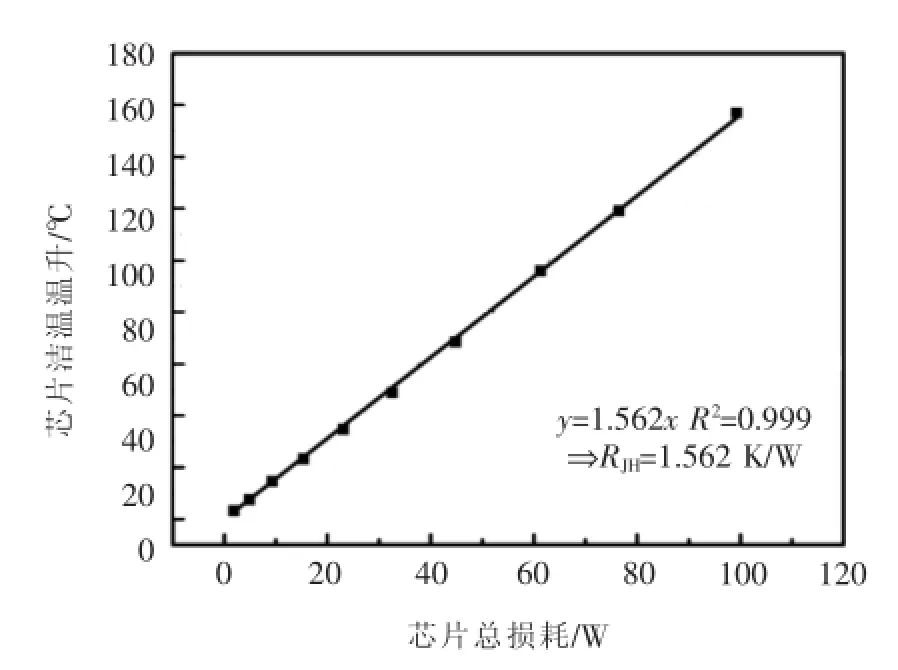

本文采用热成像仪读取芯片的表面温度。校准热成像仪,红外发射率调整为0.90。使芯片工作在持续导通状态下,此时芯片结温的上升全部来自导通损耗自发热产生的热量。通过改变导通电流得到不同导通电流时的芯片结温上升值,测量芯片两端电压和电流得到此时的芯片损耗。热阻值拟合结果如图5中所示。由图可以看出,芯片结到散热器的总热阻值为1.562 K/W。

图5 热阻抗值拟合结果Fig.5 Fitting result of thermal impendance

2 全碳化硅Boost平台的搭建、实验测试及结果分析

2.1平台搭建

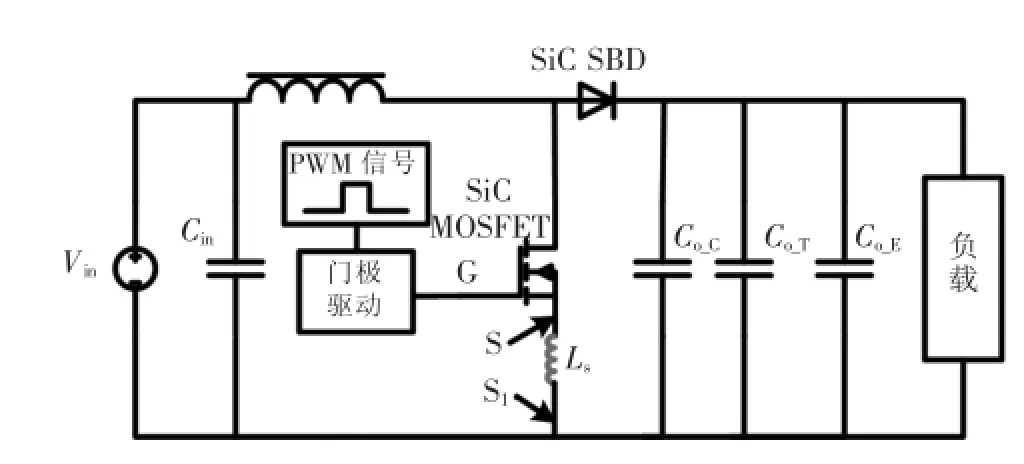

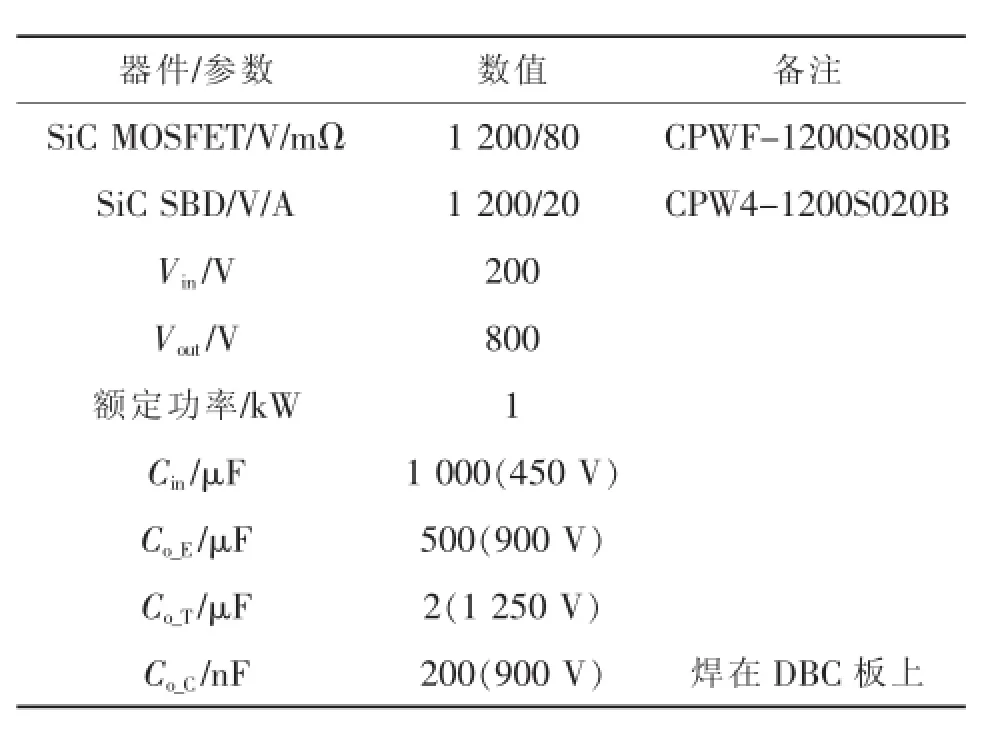

搭建了1台由SiC MOSFET和SiC SBD组成的Boost样机,电路结构如图6所示,参数表1所示。

图6 Boost电路测试平台Fig.6 Boost circuit test platform

表1 全碳化硅模块参数Tab.1 Parameters of All-SiC module

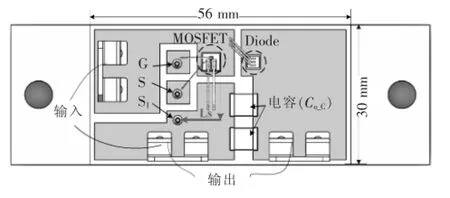

图7为全碳化硅 Boost桥臂模块,SiC MOSFET、SiC SBD和瓷片电容Co_C焊接在模块上。图中从G和S端进行驱动时,不含共源极电感。从G和S1端进行驱动时,包含共源极寄生电感LS,该电感值大小采用Ansys Q3D仿真得到,约为8.5 nH,与目前SiC MOSFET采用的TO-247封装的共源极电感值近似。

图7 全碳化硅boost模块Fig.7 All-SiC boost module

2.2实验测试及结果分析

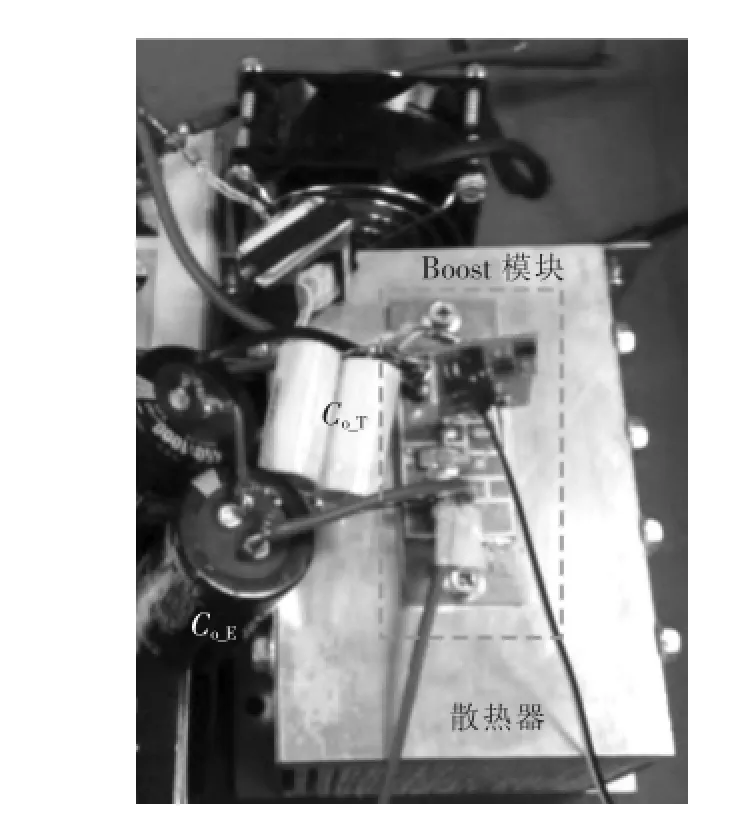

实验平台实物如图8所示,图中驱动电路信号由信号发生器经光耦隔离,输出电压为-5~20 V,外接门极驱动电阻大小为1 Ω。

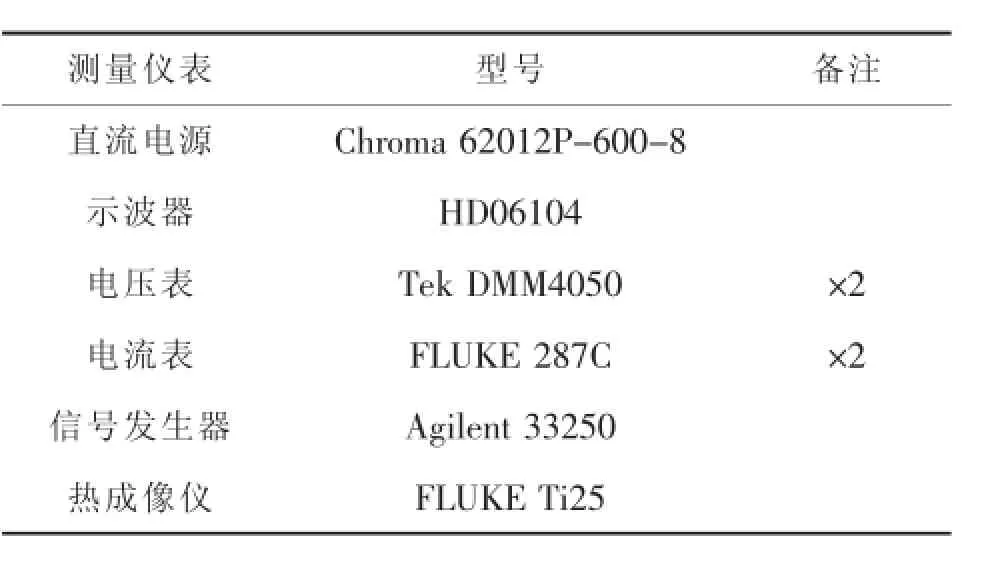

实验所用的直流电源和测试仪表如表2所示。

实验采用开环测试,保持Boost电路输入电压为200 V,输出电压为800 V,阻性负载,输出功率在1 kW左右。

图8 Boost测试平台实物Fig.8 Prototype of boost test platform

表2 实验测量仪表Tab.2 Instruments of experiment

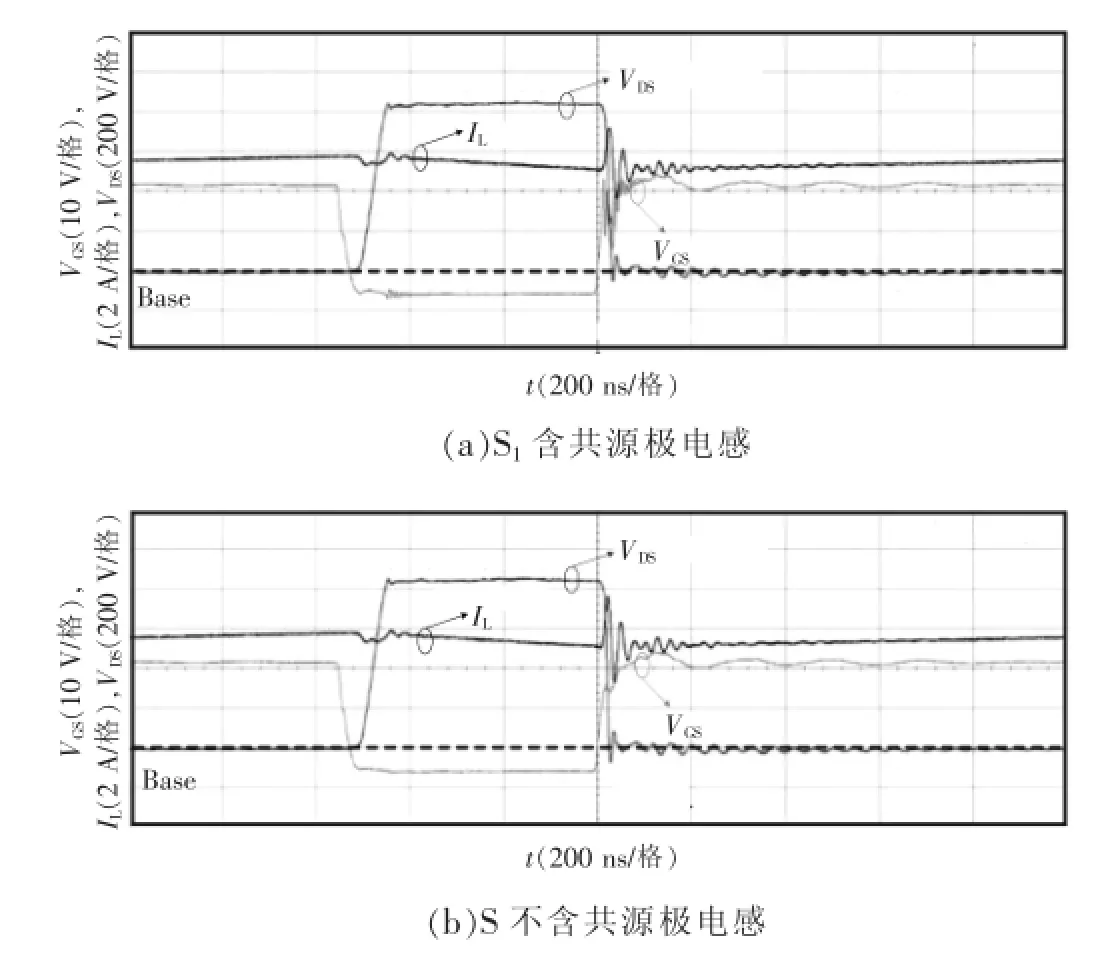

硬开关实验,驱动分别加在G、S两端(不含共源极电感Ls)和G、S1两端(包含共源极电感Ls),电路电感保持在0.68 mH左右,分别测试从100 kHz 到500 kHz(间隔100 kHz)的器件损耗。实验波形与损耗分析分别如图9~图14所示。

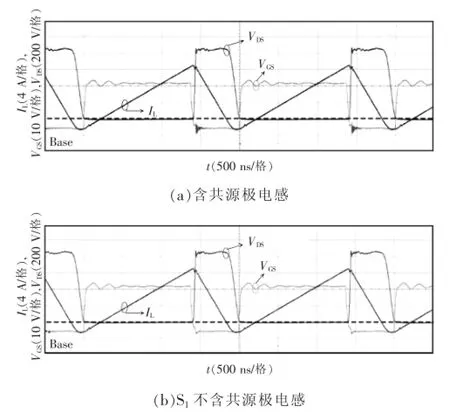

图9为输出功率1 kW时硬开关波形,图9(a)为包含共源极电感的开关波形。由图可以看出,开通和关断时门极电压波形相比图(b)不含共源极电感的波形有更为明显的振荡现象。

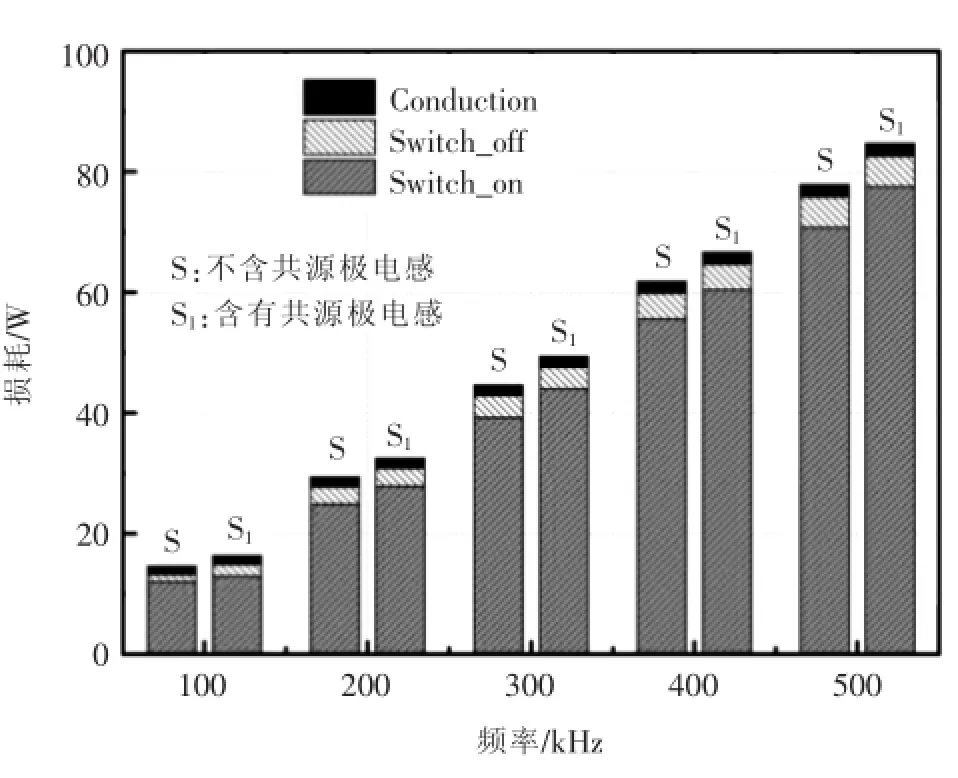

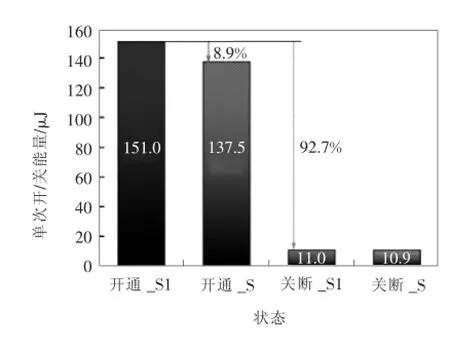

图10为根据上述分析方法得到的损耗,图中S对应表示不含共源极电感,S1代表含共源极电感。由图可以看出在该电路的工作状态下器件的开通损耗值远大于器件的关断损耗值,结果和文献[10、11]一致,是高压MOS器件的一个重要特性;同时,共源极电感增大了器件的开通损耗值,但是由于关断损耗值非常小,在500 kHz时仍小于总输出功率的0.5%,节温温升小于10°C,此时考虑到热成像仪精度(±2°C)及环境温度波动,所以实验结果表现出的共源极电感对于关断损耗影响并不明显。

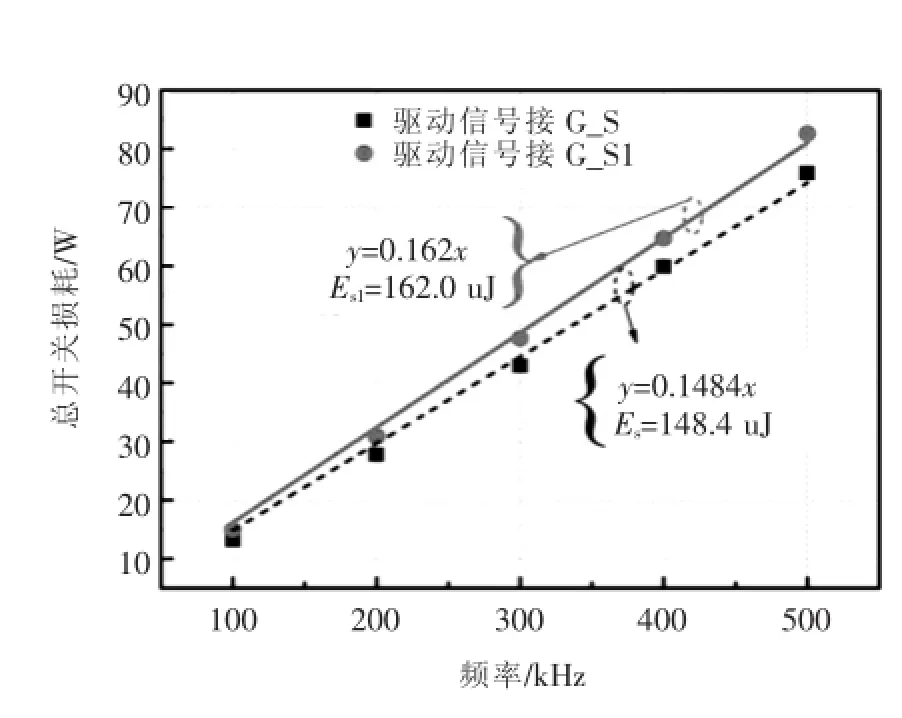

图11为器件总开关损耗和频率的关系,拟合得到的直线斜率即为器件单次开关损耗的能量。参照图11同样可以得出器件单次开通和单次关断的能量值大小。

图9 输出功率1 kW时硬开关实验波形Fig.9 Experimental waveforms of hard-switching at output power 1 kW

图10 硬开关损耗Fig.10 Loss of hard-switching

图11 总开关损耗和频率关系Fig.11 Relationship of total switching loss and frequency

图12 输出功率1 kW时硬开关单次开通、关断能量Fig.12 Switching energy in one cycle of turn-on and turn-off in hard switching experiment at output power 1kW

图12为SiC基MOSFET硬开关单次开通和关断能量对比。由图可以看出,当不含8.5 nH的共源极电感时,在本文实验条件下SiC MOSFET的硬开关时开通时单次开关能量由151.0 μJ下降到137.5 μJ,下降了8.9%;关断时的差别并不明显,原因如前文分析。

为了进一步观察共源极电感对于SiC MOSFET关断损耗的影响,增大ZVS软开关实验的关断电流进行试验。图13为输出功率1 kW时软开关波形,图(a)为含有共源极电感的开关波形,因为是零电压开通,所以开通波形和图(b)不含共源极电感的波形一致。但关断时门极电压波形相比于图(b)有更为明显的振荡现象。

图13 1 kW软开关波形(500 kHz)Fig.13 Soft-switching waveforms at output power 1 kW (500 kHz)

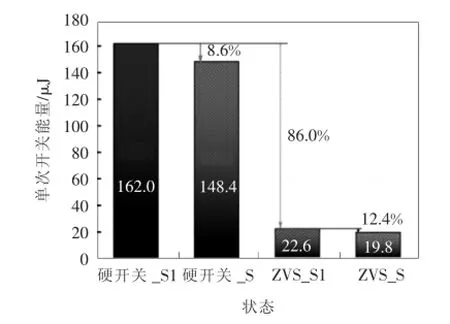

图14是同为1 kW输出功率时SiC MOSFET硬开关和软开关的单次开关能量。当不含8.5 nH的共源极电感,SiC基MOSFET在实验条件下的硬开关单次开关能量由162.0 μJ下降到148.4 μJ,下降了8.6%,软开关单次开关能量由22.6 μJ下降到19.8 μJ,下降了12.4%。

图14 1 kW时单次总开关能量Fig14 1 kW switching energy in one cycle for hard switching and soft switching experiment

3 结语

本文就共源极电感对于SiC MOSFET的开关损耗影响进行了分析。通过测量芯片结温温升和芯片热阻的方法间接得到芯片的损耗。并且通过采用零电压开通的实验方法分别对比和分析了共源极电感对于开通和关断损耗的影响。实验结果表明共源极电感的存在增大了SiC MOSFET的开通损耗以及关断损耗。所以在具体的应用特别是高频中应该注意优化电路参数,避免共源极电感导致额外的开关损耗。

[1]徐德鸿,陈文杰,何国锋,等.新能源对电力电子提出的新课题[J].电源学报,2014,12(6):4-9. Xu Dehong,Chen Wenjie,He Guofeng,et al.New power electronics topics brought by the development of renewable energy[J].Journal of Power Supply,2014,12(6):4-9(in Chinese).

[2]胡光铖,陈敏,陈烨楠,等.基于SiC MOSFET户用光伏逆变器的效率分析[J].电源学报,2014,12(6):53-58. Hu Guangcheng,Chen Min,Chen Yenan,et al.Efficiency analysis of household PV inverter based on SiC MOSFET [J].Journal of Power Supply,2014,12(6):53-58(in Chinese).

[3]Chen Zheng,Boroyevich D,Burgos R.Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C].Power Electronics Conference(IPEC),2010 International,IEEE,2010:164-169.

[4]Li Helong,Munk-Nielsen S.Detail study of SiC MOSFET switching characteristics[C].Power Electronics for Distributed Generation Systems(PEDG),2014 IEEE 5th International Symposium on,IEEE,2014:1-5.

[5]Nayak P,Krishna M V,Vasudevakrishna K,et al.Study of the effects of parasitic inductances and device capacitances on 1200 V,35 A SiC MOSFET based voltage source inverter design[C].Power Electronics,Drives and Energy Systems (PEDES),2014 IEEE International Conference on,IEEE,2014:1-6.

[6]Anthon A,Hernandez J C,Zhang Zhe,et al.Switching investigations on a SiC MOSFET in a TO-247 package[C]. Industrial Electronics Society,IECON 2014,40th Annual Conference of the IEEE.IEEE,2014:1854-1860.

[7]Wang Zhaohui,Zhang Junming,Wu Xinke,et al.Analysis of stray inductance’s influence on SiC MOSFET switching performance[C].Energy Conversion Congress and Exposition(ECCE),2014 IEEE.IEEE,2014:2838-2843.

[8]Cougo B,Schneider H,Meynard T.High current ripple for power density and efficiency improvement in wide bandgap transistor-based buck converters[J].Power Electronics,IEEE Transactions on,2015,30(8):4489-4504.

[9]Xiong Yali,Sun Shan,Jia Hongwei,et al.New physical insights on power MOSFET switching losses[J].Power Electronics,IEEE Transactions on,2009,24(2):525-531.

[10]Wang Jianjing,Chung H S,Li R T.Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance[J].Power Electronics,IEEE Transactions on,2013,28(1):573-590.

[11]Zhong Xueqian,Wu Xinke,Zhou Weicheng,et al.Design and experimental analysis of a 1 kW,800 kHz all-SiC boost DC-DC converter[C].Applied Power Electronics Conference and Exposition(APEC),2014 Twenty-Ninth Annual IEEE. IEEE,2014:492-492.

Impact of Common Source Inductance on Switching Loss of SiC MOSFET

DONG Zezheng,WU Xinke,SHENG Kuang,ZHANG Junming

(College of Electrical Engineering,Zhejiang University,Hangzhou 310027,China)

Common source inductance(CSI)exists both on the power loop and the gate driver loop of a power electronic circuit,impacting the switching characteristics and losses of devices.The higher the switching speed and frequency is,the severer the impact is.SiC MOSFETs can switch much faster compared to its Si-based counterpart due to its material superiority,so it’s more important to study the impact of common source inductance on switching loss of SiC MOSFET.First,the benefits and drawbacks of common means to measure device switching loss is in this paper analyzed,then a method of measuring temperature rise and thermal resistance is adopted.Finally,a 1 kW,800 V output all-SiC boost DC-DC converter is built to accomplish this study,and the converter works from 100 kHz to 500 kHz at intervals of 100 kHz.The experiment results show that the turn on loss and turn off loss will be reduced when eliminating the common source inductance.

common source inductance;switching loss;SiC MOSFETs

董泽政

10.13234/j.issn.2095-2805.2016.4.112

TM 461.5

A

2016-04-09

董泽政(1991-),男,博士研究生,研究方向:碳化硅器件的应用与封装,E-mail:dongzz1218@zju.edu.cn。

吴新科(1978-),男,通信作者,博士,教授,博士生导师,研究方向:高频高密度软开关变流技术,E-mail:wuxinke@zju.edu.cn。

盛况(1974-),男,博士,教授,博士生导师,研究方向:新型电力电子器件及应用,E-mail:shengk@zju.edu.cn。

张军明(1975-),男,博士,教授,博士生导师,研究方向:电力电子新能源变换和储存技术,E-mail:zhangjm@zju.edu.cn。