第三代半导体GaN功率开关器件的发展现状及面临的挑战

何 亮,刘 扬

(1.中山大学电子与信息工程学院,广州510275;2.中山大学电力电子及控制技术研究所,广州510275)

宽禁带功率电子器件及其应用专辑

第三代半导体GaN功率开关器件的发展现状及面临的挑战

何亮1,2,刘扬1,2

(1.中山大学电子与信息工程学院,广州510275;2.中山大学电力电子及控制技术研究所,广州510275)

氮化镓(GaN)材料具有优异的物理特性,非常适合于制作高温、高速和大功率电子器件,具有十分广阔的市场前景。Si衬底上GaN基功率开关器件是目前的主流技术路线,其中结型栅结构(p型栅)和共源共栅级联结构(Cascode)的常关型器件已经逐步实现产业化,并在通用电源及光伏逆变等领域得到应用。但是鉴于以上两种器件结构存在的缺点,业界更加期待能更充分发挥GaN性能的“真”常关MOSFET器件。而GaN MOSFET器件的全面实用化,仍然面临着在材料外延方面和器件稳定性方面的挑战。

氮化镓;Si衬底上GaN功率电子器件;GaN MOSFET器件;产业化

引言

功率电子器件是电力电子技术的基础,也是电力电子技术发展的重要推动力。功率电子器件的主要功能是通过器件的高速开关完成各种电能形式的相互变换,主要包括交直流转换、高低压变换、交流频率变换等等一系列能量形式的变换,从而可以将发电站输出的电能——“粗电”变换成日常生活可以使用的各种“细电”。可见器件性能优劣将直接影响到电能的利用效率[1]。

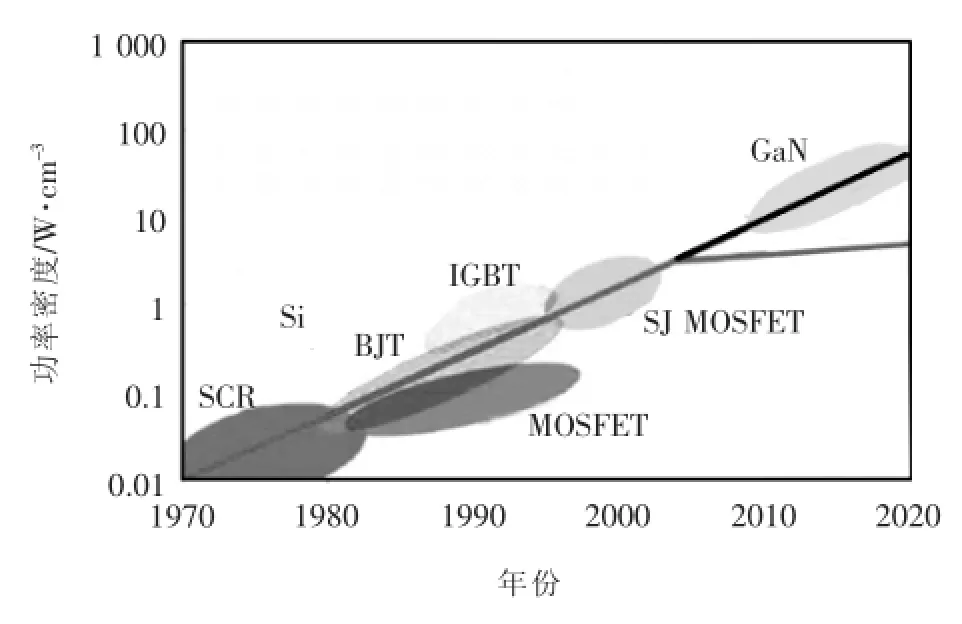

目前,市场上主流的功率电子器件主要是基于半导体Si材料制备的。从20个世纪70、80年代开始,Si基微电子技术经过几十年的发展,器件形式不断演化,性能不断推陈出新。从最早的可控硅(SCR)到全控型的双极型晶体管(BJT)、单极型高速MOSFET器件,再到功率转换能力更大的绝缘栅双极型场效应晶体管(IGBT),以及到近年快速发展的超结器件(SJMOSFET)等等,器件性能逐年提升。这种性能的改变不仅表现在能量变换效率的提升,而且表现在系统装置能量处理能力上——功率密度的提升,这一指标平均每4年就提升1倍,被业界称为“功率电子领域的摩尔定律”。但是,随着半导体工艺技术的不断改进,Si器件性能已经趋向其材料本身的理论极限,使得功率密度的增长出现了饱和趋势,其发展速度已无法满足市场的高性能要求。2015年,在政府发布的“《中国制造2025》重点领域技术路线图”中,提到大力推动电力装备这一重点领域的突破发展,包括对大功率电力电子器件这一关键元器件的开发,形成产业化能力。

1 GaN功率开关器件的优势和发展前景

归功于GaN外延材料生长上取得的突破,GaN在发光二极管LED和射频RF放大器两个领域取得了长足发展。自从1991年日本科学家中村修二等成功制备了高亮度的GaN基蓝光LED开始,GaN材料在光电器件领域得到快速发展,而日本科学家中村修二、赤崎勇和天野浩3人也因发明高效率蓝光LED获得2014年诺贝尔物理学奖。1993年,美国南卡莱罗纳大学的M.A.Khan教授研制出了世界上第1只AlGaN/GaN异质结场效应晶体管(HFET)[2],开启了GaN射频器件时代。在此之后,美国加州大学圣塔芭芭拉分校和耶鲁大学于2001年成功制备了耐压达到1.2 kV的AlGaN/GaN HFET[3],证明了GaN材料在功率开关器件领域的可行性,这一意义重大的研究成果掀起了GaN基功率器件的研发热潮,并在过去的十多年间取得了显著的成绩。以GaN和SiC为代表的第三代宽禁带半导体可以继续保持这一增长趋势[4],如图1所示。因此,重点突破SiC、GaN等第三代功率半导体功率器件的研发和产业化显得尤为重要。

图1 功率电子系统的功率密度发展趋势(功率电子“摩尔定律”[2])Fig.1 The development trend of power density for power electronic systems

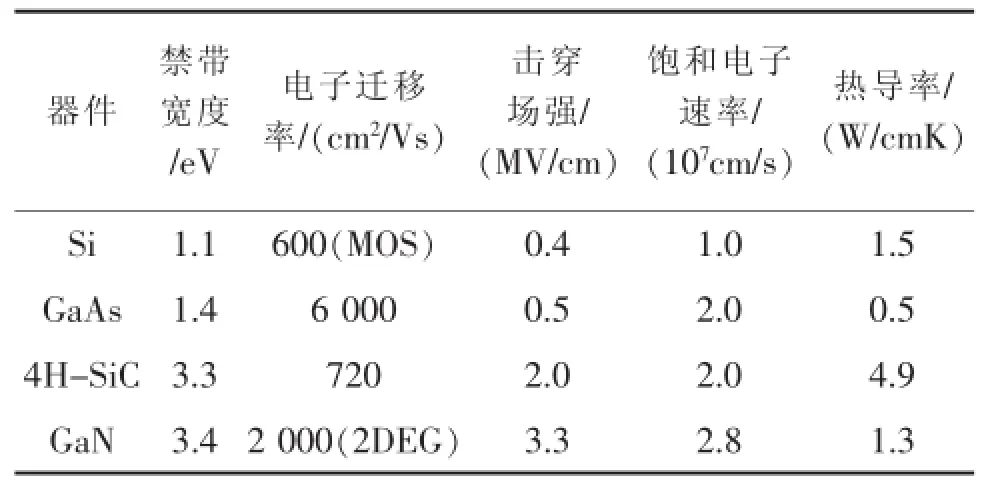

作为第三代半导体材料的代表,GaN具有宽禁带、高临界击穿电场、高饱和电子漂移速度、高电子迁移率等优点,在电力电子领域有着广泛的应用前景,表1给出了制备功率电子器件的几种半导体材料物性参数[1,5,6]。

表1 常见制备功率电子器件的半导体材料物性参数Tab.1 Characteristics parameters of different semiconductor materials

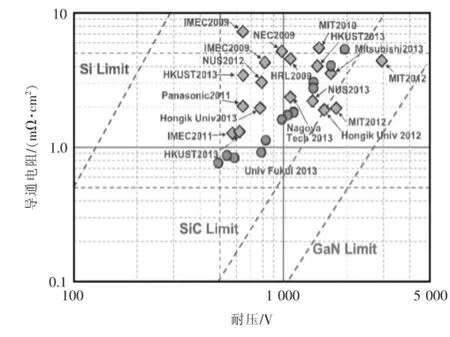

图2为Si材料和宽禁带半导体SiC和GaN的导通电阻和耐压关系理论值比较[7]以及GaN功率开关器件目前的发展状态。与Si基功率电子器件相比,GaN基功率电子器件具有如下3个优点:①高效节能:由于GaN材料特有的极化特性,在AlGaN/ GaN异质结间存在极强的极化效应,形成迁移率高达2 000 cm2/V·s和面密度高达1013cm-2量级的高浓度二维电子气(2DEG)[8]。GaN基功率开关器件HFET利用AlGaN/GaN异质结2DEG工作,器件具有导通电阻小、开关速度快的优点,使器件的通态损耗和开关损耗大大降低。②可以使电力电子装置小型化、轻量化,低成本化:GaN材料比Si具有更大的禁带宽度,使GaN器件可以工作在更高温度环境,因此可简化甚至省去散热装置。此外由于GaN器件具有高的开关频率,使得系统的无源器件电容电感的体积大大缩小。这些都使得GaN基电力电子装置能更小型化轻量化,大大降低系统制作成本。③输出功率密度大,驱动力强劲:由于宽禁带等特性,GaN材料的临界击穿电场高达 3.4 MV/ cm,是Si材料的10倍,因此GaN器件具有更高耐压能力。同时GaN基器件利用2DEG工作,获得低导通电阻,高电流密度,因此使GaN器件可以获得更大的功率密度。

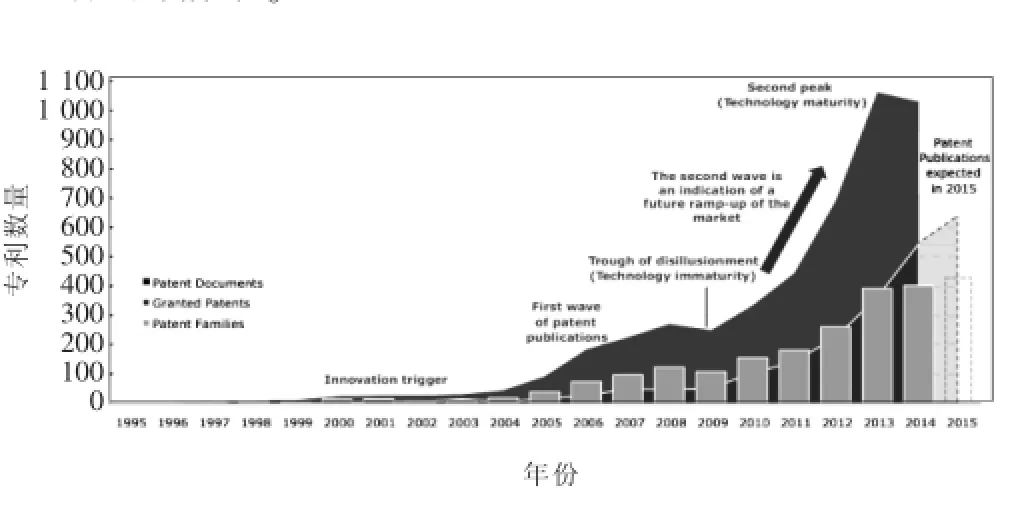

目前全球功率器件每年约有150亿美元的市场规模,根据GaN行业先行者GaN Systems公司的评估,GaN器件可以直接替代的市场份额至少可达20%,这还不包括尚待发展的领域,比如电动汽车等新兴潜力市场。2015年国际著名半导体资讯调查机构Yole Development报道分析了GaN功率电子器件的知识产权动态[9],从2010左右发展出第一只GaN商业化器件至今,世界范围内GaN的专利申请量急剧攀升,出现了新一轮的发展高潮,如图3所示。可见,GaN功率电子器件可以满足现代电子技术对高温、高功率、高压、高频以及抗辐射等恶劣条件的新要求,以其优异的能源利用效率,而且可以实现系统小型化、轻量化,从而大大降低制作成本,在整个世界范围内推行节能减排的今天,具有十分重大的现实意义。它将在消费类电子、云服务、光伏发电、新能源电动汽车等领域有着巨大的应用前景。

图2 不同半导体材料导通电阻和耐压关系理论数值以及GaN功率开关器件目前的发展状态Fig.2 On-resistance versus breakdown voltage for semiconductor materials and the present status of GaN power switching devices

图3 过去10年GaN功率电子器件的知识产权发展动态Fig.3 Power GaN intellectual property(IP)development dynamics in the past decade

2 GaN功率电子器件的技术路线

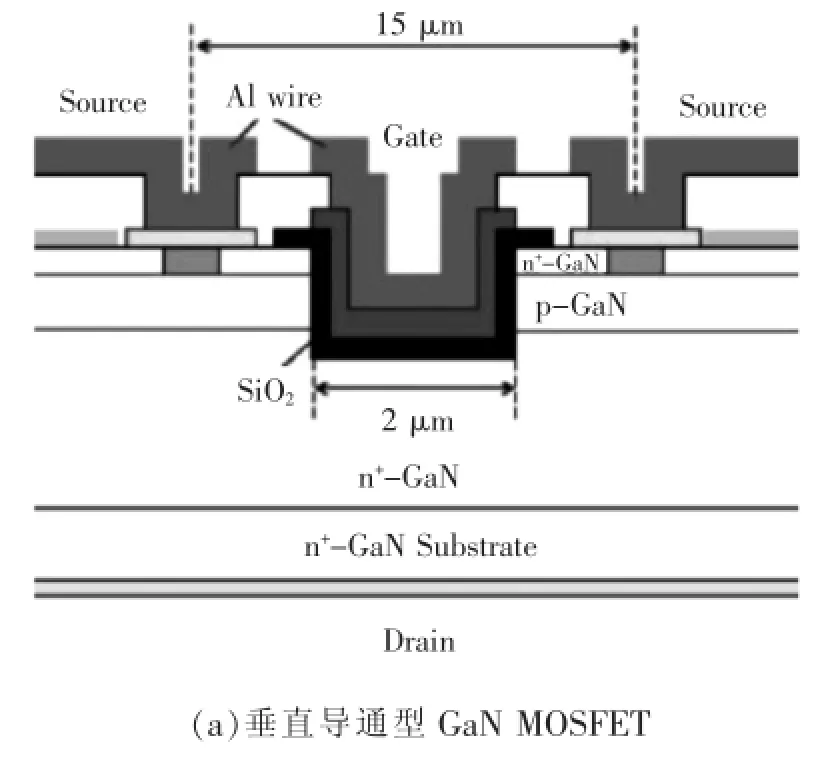

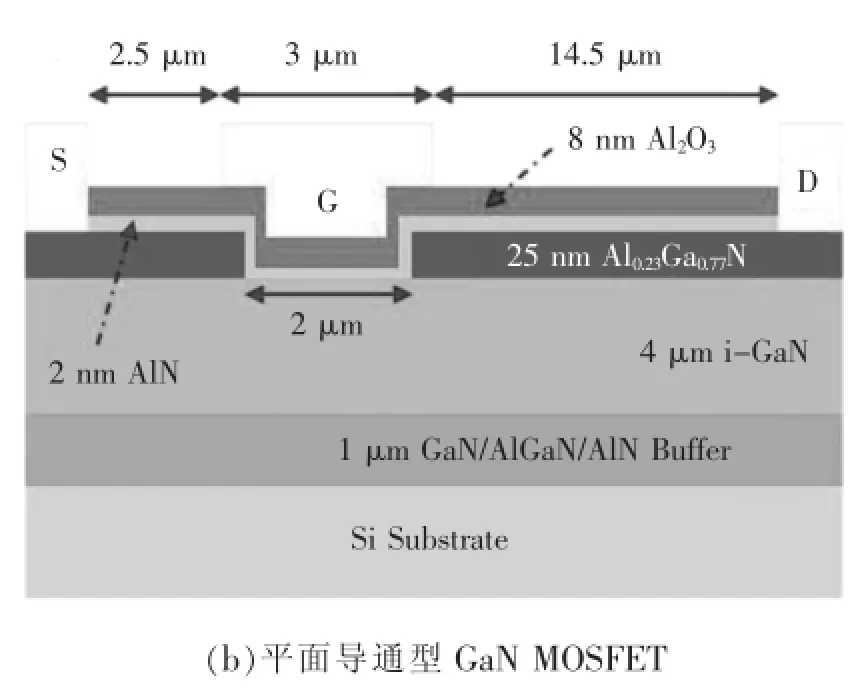

目前世界范围内围绕着GaN功率电子器件的研发工作主要分为两大技术路线,一是在自支撑GaN衬底上制作垂直导通型器件的技术路线[10,11],另一是在Si衬底上制作平面导通型器件的技术路线[12,13]。GaN基垂直和平面导通型器件的结构简图如图4所示。

图4 基于GaN自支撑衬底的垂直导通型MOSFET[11]以及基于Si衬底的平面导通型GaN MOSFET[13]的器件结构简图Fig.4 Schematic of vertical GaN MOSFET on free-standing GaN substrate and lateral GaN MOSFET on Si substrate

2.1垂直导通型GaN功率电子器件技术路线

对于GaN基功率电子器件,最理想的是在GaN自支撑衬底上同质外延GaN有源层,进而进行器件的制备。基于高导的GaN自支撑衬底制备的GaN垂直导通型器件,相对平面导通型器件而言,有以下3点优势:①更易于获得高的击穿电压:垂直型器件由于漏极制作在栅极和源极的背面,在漏极加高电压时,电场会比较均匀地沿着垂直方向分布,而不存在平面器件的栅极边缘尖峰电场现象,因此垂直型器件比平面型器件更利于获得高的击穿电压。②可以减缓表面缺陷态引起的电流崩塌效应:垂直型器件的高场区域在材料内部,远离表面,从而可以弱化表面态的影响而减缓电流崩塌效应。③更利于提高晶圆利用率和功率密度:垂直型器件本身不存在尖峰电场而不需要使用场板结构,也无需通过增加栅漏间距实现高击穿电压,因此,垂直型器件比平面型器件在某种程度上工艺更简单,也更容易提高晶圆利用率以及提高功率密度。

尽管垂直导通型GaN器件优势十分明显,但是与平面型器件相比发展相对缓慢,相关研究于近十年左右才刚刚起步,而且在产业化进程上面临着一些待解决的技术难点。第1点是如何实现导电大尺寸自支撑GaN衬底低成本化。GaN基垂直导通型功率电子器件实现商业化的主要瓶颈是导电自支撑GaN衬底非常难以制备,导致其价格非常昂贵。由于 GaN材料具有极高的饱和蒸汽压,很难像Si和GaAs那样采用拉单晶的方式制备GaN衬底。因此,解决导电自支撑GaN衬底制备问题[14],使其实现低成本化,毫无疑问将是实现GaN基垂直导通型功率电子器件产业化目标最迫切需要解决的问题。第2点是自支撑GaN衬底上同质外延厚膜GaN层的背景掺杂问题。同质外延GaN材料中O、Si等背景掺杂以及位错、寄生沟道等会降低载流子迁移率,严重影响器件性能。因此,抑制背景掺杂、制备低缺陷密度的厚膜GaN层,是提升器件高耐压能力的关键问题[15]。此外,p型掺杂沟道电流限制层的制备也是一直存在的技术难点。高性能p型掺杂有利于提高器件栅控制能力和耐压性能[16],对于宽禁带半导体GaN而言,提高p型受主杂质的电离效率是科学界亟待解决的一个难点。

有关GaN垂直导通结构器件的研究,尤以日本丰田公司和美国Avogy公司为代表,还有加州大学圣塔芭芭拉分校(UCSB)和日本罗姆半导体公司(ROHM)等著名公司和研究机构。其中,日本丰田公司于2013年在GaN自支撑衬底上研制了耐压达1.6 kV的垂直导通的常关型GaN MOSFET器件[11]。美国Avogy公司采用2-inch GaN自支撑衬底,分别于2014年和2015年制备了耐压达到1.5 kV的常开型GaN FET[17]和4 kV的GaN pn结二极管[15]。与平面导通结构器件相比,GaN垂直型器件采用价格昂贵的GaN自支撑衬底,所以未来将主要定位于高耐压器件的高端市场,与宽禁带SiC器件展开竞争。目前,GaN垂直型器件在产业方面的成果还鲜有报道。

2.2基于Si衬底的平面导通型GaN功率电子器件技术路线

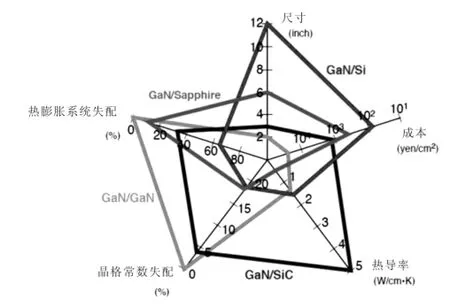

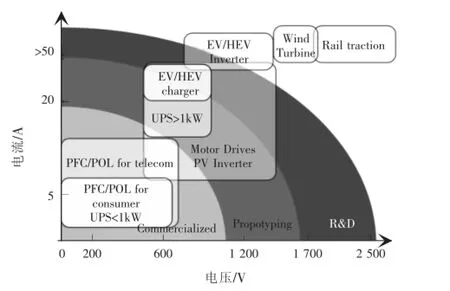

由于GaN同质外延的成本居高不下,因此在GaN功率电子器件的商业化进程中,选择合适的衬底材料以发展基于异质外延的平面型器件是目前的主流解决方案。在异质外延生长过程中,衬底材料不仅需要具有与GaN外延层材料相当的热膨胀系数以及较小的晶格失配。同时,它还需要具有高温(1 000℃左右)化学物理稳定特性。理论上应尽量选择与GaN材料晶格失配和热失配小的衬底,但是在实际应用中需要对其他参数进行综合考虑。目前,可供选择的衬底材料主要包括蓝宝石、SiC和Si衬底等[18],如图5所示。

图5 适合GaN外延生长的不同衬底特性对比Fig.5 Comparison between different substrates on GaN epitaxial grown

目前蓝宝石衬底是GaN异质外延生长中应用最广泛的衬底材料,并且已经在光电器件产业方面有了成熟的应用。但在功率器件领域,蓝宝石衬底却存在非常明显的缺点。首先,蓝宝石的热导率非常低,制备的功率器件散热能力不强,使得GaN材料本身的优势很难得到充分发挥,因而限制了蓝宝石衬底在功率器件产业应用的前景;另一方面,蓝宝石衬底中的氧元素在GaN中形成重掺杂n型背景载流子,这严重限制了高耐压GaN外延材料制备。此外,SiC衬底与GaN材料晶格失配小,且具有高的热导率,使其非常适合制作高温高功率工作下的电子器件。但是受制于SiC材料本身很难制备,且价格非常昂贵,这限制了SiC衬底在商业GaN电子器件领域的推广。

Si衬底与GaN材料的晶格失配和热失配都非常大,但是Si材料相比蓝宝石材料热导率高,晶元尺寸大,成本低,制作工艺成熟并且能和现有CMOS工艺兼容,这些优点使得Si衬底成为实现商用化GaN功率器件产业化的最佳衬底。Si衬底上GaN基平面导通型器件是目前的主流技术,从几十到几百伏的中低压应用领域已逐渐走向产业化。

3 Si衬底上GaN基功率开关器件的发展状况

在电力电子控制系统中,为了保证系统失效安全,器件必须具备常关型的工作特性。通常对于Si衬底上GaN基功率开关器件,主流技术是利用Al-GaN/GaN异质结构界面处高浓度、高迁移率的2DEG工作,使器件具有导通电阻小、开关速度快的优点。然而,这种AlGaN/GaN HFET即使在外加栅压为0的情况下,其器件也处于开启状态。如何实现高性能的常关型操作是GaN功率开关器件面临的一个重要挑战。

3.1GaN常关型功率开关器件的主流技术

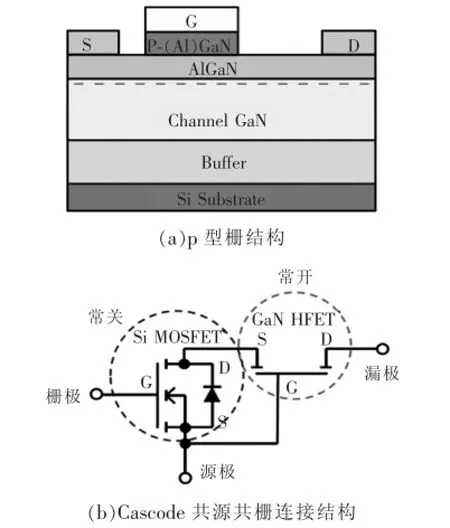

实现常关型工作特性的一般思路是保留接入区高导通的2DEG,同时耗尽或截断栅极下方的2DEG,以实现器件零偏压下关断。目前业界最普遍采用的常关型GaN器件的结构有3种:(1)结型栅结构(p型栅)[19],(2)共源共栅级联结构(Cascode)[20],(3)绝缘栅结构(MOSFET)[21-24],如图6所示。

图6 GaN常关型器件结构示意Fig.6 Schematic of GaN normally-off devices

目前,前两种方案已经实现了产业化。p型栅结构方案是利用栅极下方的p型 (Al)GaN层抬高沟道处的势垒,从而耗尽沟道中的2DEG来实现常关。该结构的制备工艺难度较大,需要对接入区p型层的刻蚀,存在阈值电压小、栅压摆幅冗余度小以及抵抗电磁干扰能力差等缺点,此外其栅极漏电流大,且无法通过采用MOS栅结构来进行改善。而Cascode级联结构的常关型器件方案是将一只高压常开型GaN HFET和一只低压常关型Si MOSFET通过Cascode方法组合成一个全新的混合管来实现常关。然而,Cascode结构会带来芯片所引入的附加寄生参数增大等问题,限制器件的高频开关性能,使得GaN的高速开关性能很难得到充分的发挥,而多芯片的封装也会降低器件的可靠性能。

绝缘栅结构器件通过引入一层绝缘栅介质层,可以解决上述p型栅阈值电压低等问题。而Cascode结构只是目前的一个暂时的解决方案,业界更加期待“真”常关型器件——绝缘栅结构器件,目前绝缘栅法使用最普遍的就是凹槽栅结构,如图6(c)所示。凹槽绝缘栅结构器件的工作原理是,通过凹槽切断栅极下方的2DEG,使得器件在零栅压下为关断状态。当正栅压增至大于阈值电压时,将在栅界面处形成电子积累层以作为器件的导电沟道,器件呈导通状态。凹槽绝缘栅技术在制备常关型功率器件方案中具有很大的优势,可以解决p型栅结构和Cascode结构所带来的诸多问题,这种凹栅的形成方式包括干法刻蚀(Dry etch,如ICP)[21]、湿法刻蚀(Wet etch)[22,23]以及选择区域外延(SAG)[24-27]等。目前国内外使用凹槽绝缘栅技术制备GaN常关型MOSFET器件已有大量研究工作报道,但是器件工作的稳定性和可靠性问题仍需要进一步克服。

3.2GaN功率开关器件的产业化发展状况

2000年后,鉴于对GaN功率电子器件优异性能的预期,GaN功率器件的研发得到了美日等发达国家政府的高度重视,GaN器件的产业化发展将是电力电子技术的一次革命。国际上GaN功率器件的产业化最早开始于2010年,美国的国际整流半导体(IR)公司和EPC公司率先实现了耐压200 V以下的GaN功率电子器件的产业化制造;2012年美国 Transphorm公司推出了 600 V耐压级别的GaN功率开关器件产品,并且与日本Fujitsu公司合作推出了量产化产品,其器件结构为cascode级联结构;2014年日本Panasonic公司和加拿大新风险投资企业GaN Systems公司也分别推出了600 V 和650 V耐压等级的GaN功率开关器件,器件结构为p型栅结构。从器件的散热、集成密度、寄生效应等层面考虑,各公司采用的封装形式亦不尽相同,各产品及应用形式如图7所示。Transphorm公司采用传统的TO220直插封装和PQFN表面贴装形式,EPC公司采用LGA栅格阵列封装形式大大地降低功率损耗,GaN Systems公司采用GaNPX贴片封装和驱动器协助技术获得了极低的电感和高热效率,如图7(a)、(b)、(c)所示。从目前的发展方向来看,为了充分发挥GaN功率开关器件高速开关特性的优势,各公司采用的器件封装形式主要是倾向于贴片封装。

在系统应用方面,2014年Transphorm公司与日本安川电机(Yaskawa Electric)合作,采用其GaN功率开关器件研制出了高性能的功率达4.5 kW的光伏微逆变器,由于GaN器件的高速开关性能使得微逆变器的体积较采用Si器件的逆变器相比缩小了40%,同时损耗降低了45%,如图7(d)所示。2015年EPC公司在香港ISPSD会议上宣布该公司的GaN功率开关器件已经成功地应用于笔记本电脑的65 W电源适配器上,体积缩减到了常规适配器的1/3,如图7(e)所示,可兼容全球不同电力标准,适用于目前市场主流品牌的笔记本电脑。2015年日本Fujitsu公司宣告采用GaN器件实现了世界上体积最小、效率最高的12 W AC电源适配器。在2015年Google及美国电气电子工程师学会(IEEE)联合举办的Little Box Challenges挑战赛上,荣获第一名的CE+T Power采用GaN Systems公司的GaN 650 V功率器件设计了2 kVA逆变器,其体积缩小至13.77 inches3,效率高达95.4%,功率密度145 W/ inches3,如图7(f)所示。

图7 各公司的GaN器件产品及应用形式Fig.7 GaN devices products and application of different companies

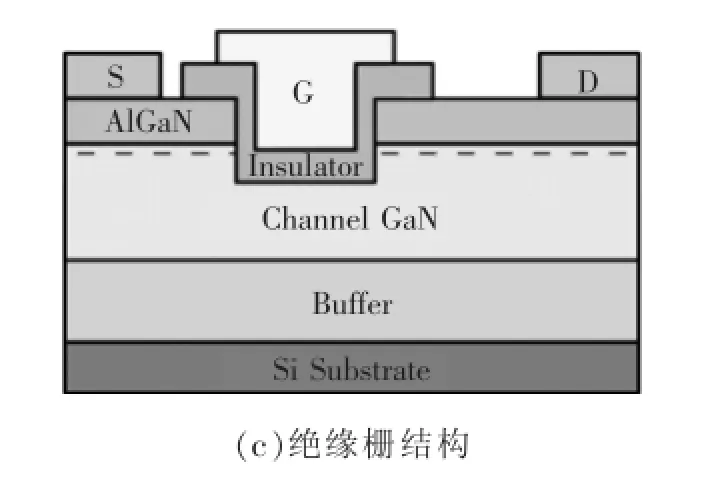

GaN功率电子器件之所以在短期内得以迅速产业化的原因,一方面得益于半导体照明使得GaN材料产业的不断成熟,另一更重要的原因是由于工业界采用了Si衬底上制备GaN材料的这一技术路线,因为从量产实用化角度考虑,Si衬底易于获得大尺寸、导热性较好,可以有效兼容传统Si集成电路CMOS工艺,可利用传统功率电子器件制造产业平台,大大减少设备投入。2014年Yole Development 对GaN市场的应用领域分析[28]如图8所示。目前,GaN功率器件的商业化主要还是集中在额定电压200 V的低压DC-DC转换器,最近随着600 V的GaN器件的产业化,预示着它将在电源以及功率因数校正等领域快速发展。在中高耐压领域,如电动汽车的电机驱动上,GaN器件也将凭借它的巨大优势在未来占据较大的市场份额。

图8 GaN功率电子器件的市场应用领域及相应电压、电流范围Fig.8 GaN state-of-the-art device vs.application requests

4 Si衬底上GaN功率开关器件的关键技术和挑战

尽管近年来Si衬底上GaN基功率电子器件取得了非常多的进展,但仍然面临着一些关键技术问题,如大尺寸Si衬底上GaN材料的异质外延和应力调控技术、器件关态漏电抑制和耐压提升技术、器件动态电阻稳定性问题、GaN MOSFET阈值电压的稳定性问题等,对此提出了相对应的解决方案。

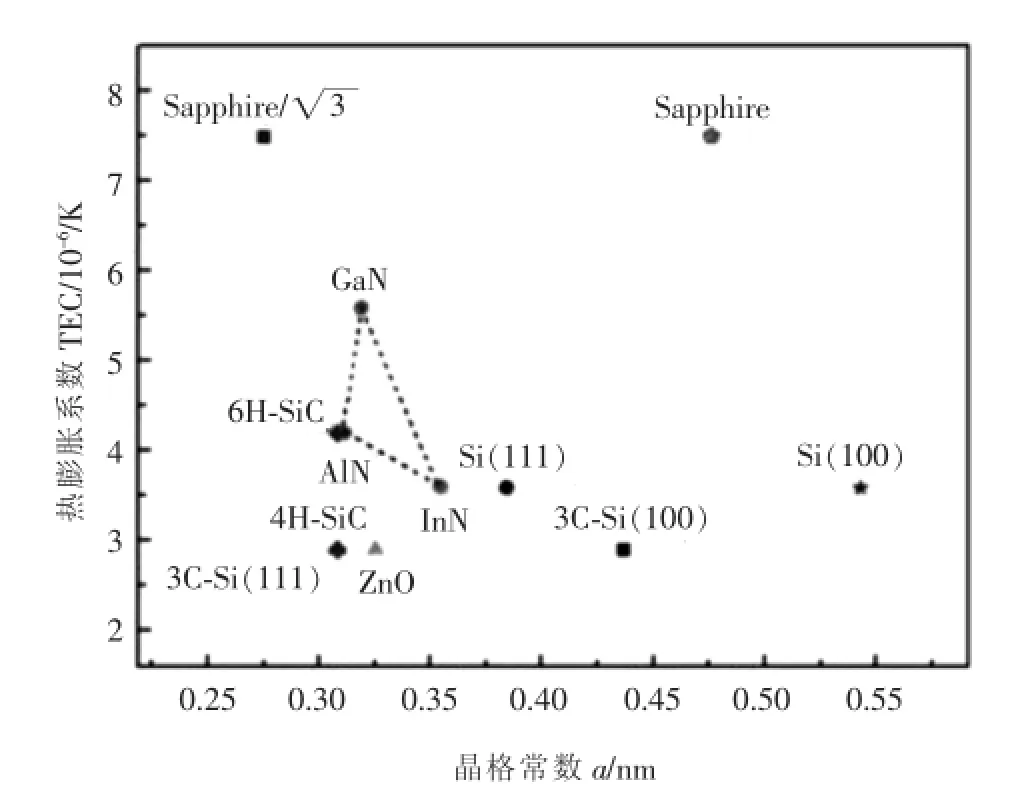

4.1大尺寸Si衬底上GaN材料的异质外延和应力调控技术

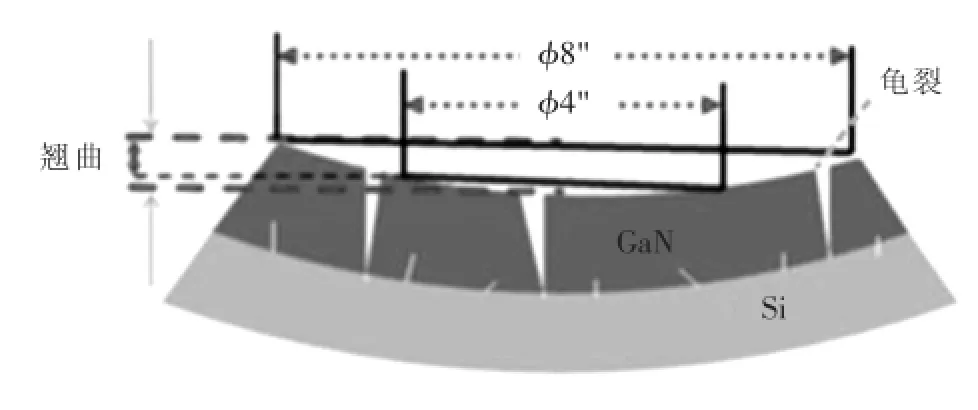

在生长GaN晶体材料的几种可能衬底材料中,虽然Si衬底拥有明显的低价格、大尺寸、易于与产业CMOS平台兼容等优势,但是实现Si衬底上异质外延高质量的GaN材料,难度仍是很大。原因主要来自于异质衬底Si和GaN外延层之间的晶格常数失配和热膨胀系数(TEC)失配[29,30],如图9所示,失配分别达16.9%和56%。Si衬底与GaN外延层之间晶格常数不同导致的晶格失配会在Si和GaN外延层界面处产生非常高密度的位错缺陷(106~109/cm2),在外延生长过程中这些位错很大一部分会贯穿整个外延层,严重裂化外延层晶体质量。而两者热膨胀系数的不同导致的热失配会使得整个外延层在高温生长后降温过程中形成非常大的应力积累,发生翘曲,严重时外延层产生龟裂,而且这种翘曲和龟裂随着衬底尺寸的增大而变得愈发严重,如图10所示。

图9 3族氮化物(GaN、AlN、InN)与常规衬底(Si、SiC、蓝宝石)之间材料热膨胀系数和面内晶格常数的关系Fig.9 Thermal expansion coefficient of III-nitride and common substrates as a function of lattice constant(in plane)

图10 Si衬底上GaN外延材料的翘曲、龟裂示意Fig.10 Schematic of bow and crake for GaN on Si substrate

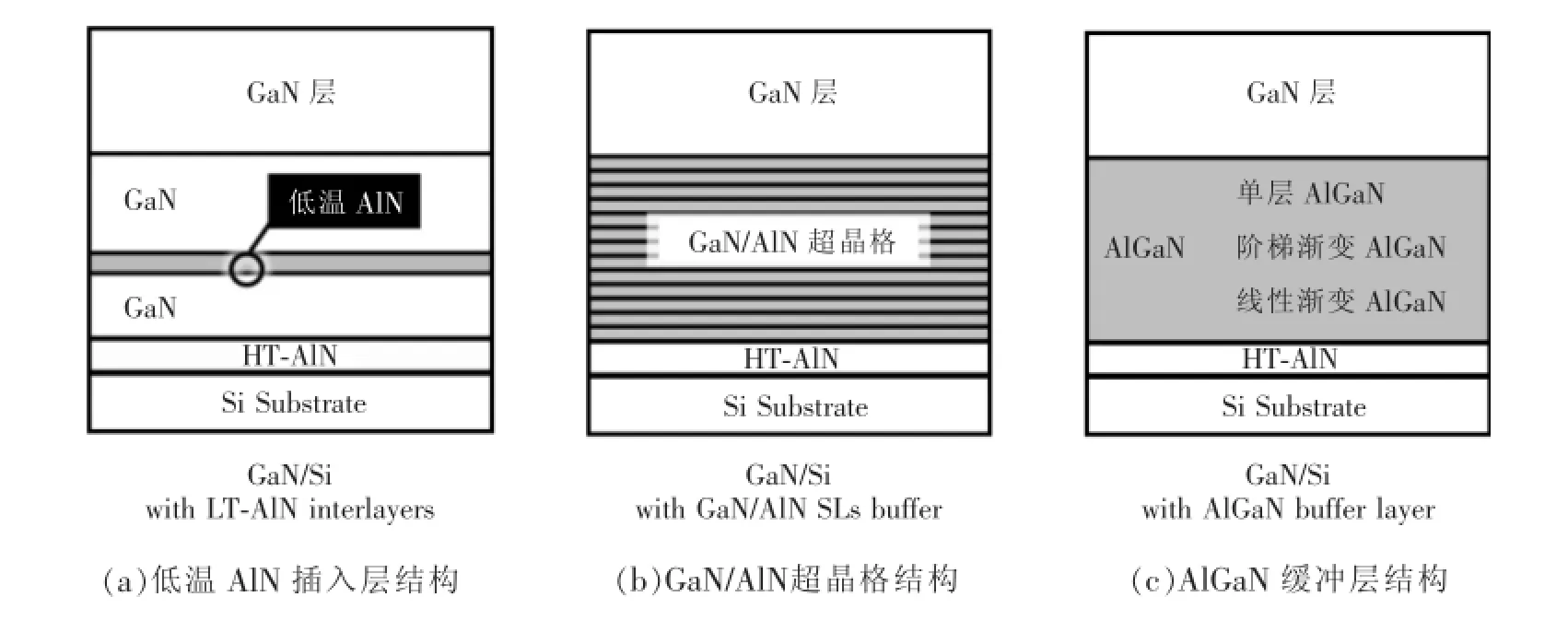

国际上关于Si衬底上异质外延GaN技术最早开始于20世纪90年代末期,GaN外延层晶体质量不断提高,晶片直径从早年的2 inch、4 inch 到6 inch,甚至发展到近期的8 inch。为了解决Si衬底上GaN异质外延时存在的应力问题,研究人员开发出了图形衬底选区生长法、插入层技术以及缓冲层技术等一系列方法。目前广泛采用的是插入层和缓冲层这两种方法,其基本外延层结构如图11所示。其中插入层技术是指通过引入一层或几层薄插入层来调节外延层内部的应力状态,平衡降温时由于热失配和晶格失配导致的外延层中的张应力,主要的插入层有低温AlN插入层[31]。而缓冲层技术也是通过提供压应力,从而调节外延薄膜内部的应力状态使其趋于平衡。目前广泛采用的缓冲层有AlGaN渐变缓冲层[32]和AlN/(Al)GaN超晶格缓冲层[33-35]。以上方法均可以达到提供压应力以平衡Si衬底GaN中的张应力使得系统趋于应力平衡的目的,最近几年6 inch和8 inch Si 上GaN外延技术的发展也逐步趋于成熟并量产化。当然,这些方法也不能完全解决应力问题,针对缓冲层对应力调控的机制仍然模糊,尚有大量的工作需要研究和优化。

图11 目前主流的3种应力缓冲层方案Fig.11 There different stress buffer layer schemes

图12 GaN功率器件的电流崩塌现象Fig.12 Current collapse phenomenon in GaN power devices

4.2器件关态漏电抑制和耐压提升技术

对于GaN基功率器件而言,高场下泄漏电流的主要来源有两个:一个是栅极漏电,即栅极的肖特基结在强电场下会出现的泄漏电流,可以通过引入栅极绝缘介质层得到有效抑制;另一个是外延缓冲层漏电,引起缓冲层漏电的原因有很多,如背景施主型掺杂、高密度位错缺陷产生的漏电通道以及AlN成核层与Si界面处的寄生导电通道等,这严重影响到器件工作的可靠性。根据相关文献报道,通过优化器件结构、提高外延层质量以及改进器件的制备技术等,目前GaN基功率开关器件的功率转换能力已远远超过了Si基器件的理论值,并部分超越了SiC器件的理论水平,逐渐接近GaN的理论极限,如图2所示[7]。现有报道的GaN器件耐压水平离理论值仍有所差距,这主要是由于上述的器件和材料中存在的问题造成的。

实现器件的低漏电和高耐压,往往需要从器件终端设计和材料缓冲层结构两个层面去解决问题。器件终端结构设计(如引入场板结构,采用MIS结构等)可以解决材料中电场分布不均匀导致尖峰电场以及栅极漏电较大等问题,但是在较大电场下,只有通过抑制缓冲层材料漏电才能在降低器件关态漏电流的同时提高器件的击穿电压。所以从材料层面提高缓冲层绝缘性能是实现低漏电/高耐压GaN基电子器件的关键,目前行之有效的方法是对缓冲层材料进行杂质补偿,受主杂质可以有效补偿材料中的过剩载流子,从而抑制漏电流,提高击穿电压。目前常用的受主掺杂杂质有C,Mg或Fe,其中C掺杂技术具有无记忆效应等优点,而且能够采用生长源进行C自掺杂[36],因此成为近年来缓冲层杂质补偿的首选方案。然而,C杂质往往在GaN外延层中扮演着深受主的角色,是引起器件电流崩塌的重要原因。

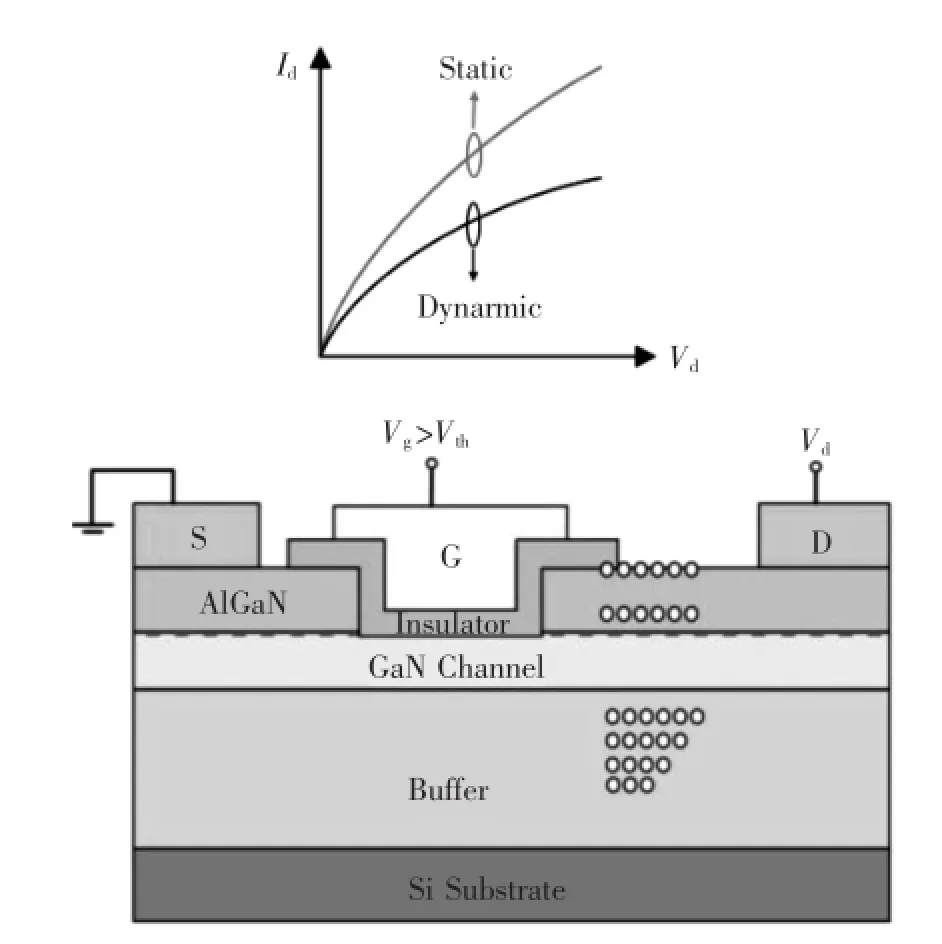

4.3器件动态电阻的稳定性问题

对于理想的GaN基功率开关器件,在关态下器件的反向漏电流为0,在开启时器件的压降为0(即导通电阻为0),可使器件的能量转换效率达到100%。然而在实际应用中,器件存在关态漏电流和开态导通电阻,器件的能量转换效率降低。除此以外,GaN功率器件在不断地由关断(高电压)切换到开启(大电流)的高速开关状态时,导通电阻会显著增大,这就是电流崩塌现象,如图12所示。

电流崩塌现象的直接体现是器件导通电阻的增大,主要原因是由于AlGaN/GaN异质界面处2DEG沟道的电子浓度下降。目前普遍认为电流崩塌现象来源于2个方面:AlGaN势垒层表面受主陷阱态[37]和AlGaN势垒层或GaN缓冲层内部受主陷阱态[38]。电流崩塌是制约GaN基功率器件应用的一个关键问题,器件导通电阻的增大会增加器件在开态下的功率损耗,降低器件的效率,而且这也是器件工作稳定性的一大挑战。目前抑制电流崩塌的主要方案有:表面处理/钝化、外延缓冲层结构设计(如背势垒层)以及器件结构设计(如场板)等。

4.4GaN MOSFET器件阈值电压稳定性的问题

根据前文所述,绝缘凹栅结构GaN基常关型MOSFET器件可以解决p型栅结构和Cascode结构所带来的诸多问题。但是这种器件存在阈值电压的回滞和漂移现象,即阈值电压的不稳定性[39]。在GaN基MOS界面系统中,沟道附近处GaN材料表面缺陷态、栅介质层/GaN界面处的界面态以及介质层内部的缺陷态,都可能产生大量的陷阱。这些陷阱态处于或者靠近栅极沟道,会引入额外的关态漏电通道,造成器件在栅极零偏压下不能理想地夹断。当电子占据这些陷阱态时,栅极沟道电子也可能会受到这些带电陷阱态的库伦散射,导致迁移率降低,器件导通特性劣化。更为严重是,这些界面陷阱态在不同的栅极开关偏压下,电子俘获和释放效应会造成阈值电压的变化,严重劣化器件工作的稳定性。此不稳定性现象,会随着外加偏压的增加及加载时间的增长而愈显著。阈值电压稳定性问题是GaN MOSFET器件面向产业化必须解决的问题,MOS栅界面控制技术是解决这一问题的关键。

对于传统的Si基MOSFET器件,通过高温热氧化的方法制备Si的本体氧化物SiO2,可以极大地降低SiO2/Si界面系统中的缺陷态。而在GaN MOSFET器件中,由于GaN的本体氧化物Ga2O3极难通过热氧化方法形成,而且Ga2O3与GaN的带阶差较小,不适合用于做栅介质层,因此必须通过物理或化学气相沉积法制备其他介质材料作为栅介质层。在该制备过程中,极易由于表面沾污以及介质层/GaN界面不饱和化学键等引入缺陷态。针对于该GaN/栅介质的界面缺陷态研究,目前科技界和产业界的研究者对绝缘栅介质沉积前后工艺条件,包括沉积前化学溶液表面处理、等离子处理,沉积时设备生长条件参数改进,沉积后不同气体环境退火处理等方法进行了深入研究,以降低界面缺陷密度,提高GaN MOSFET器件工作的稳定性。

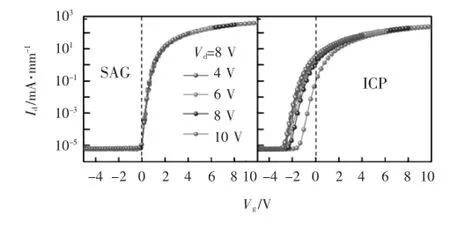

另外,早期的槽栅制备多采用等离子体干法刻蚀(ICP),而该方法会对GaN材料表面造成晶格损伤,从而引入缺陷,造成严重的器件阈值电压不稳定性问题。通过降低干法刻蚀刻蚀功率和速率的方法以及高温退火的办法,可以一定程度上降低晶格损伤。中科院微电子所黄森等采用高温干法刻蚀槽栅技术减少界面杂质沾污,实现了低界面陷阱的常关型MOSFET器件[21]。另外,通过湿法刻蚀槽栅的方法来减少损伤,但由于氮化物具有极高的抗腐蚀性,多采用先氧化后酸腐蚀的方法,如北京大学王茂俊等采用数字式氧化湿法刻蚀技术[23];浙江大学盛况等报道了经济性好、耗时短的一次氧化加湿法刻蚀制备槽栅方法[22],刻蚀出较低界面损伤的槽栅。此外,作为槽栅结构制备方法的另一种选择,中山大学提出采用选择区域外延(SAG)方法生长Al-GaN/GaN异质结构的源漏接入区[25],从而自然形成凹槽栅区,并于2015年成功地制备了高稳定性的常关型GaN槽栅MOSFET器件[41],其转移特性中的阈值电压回滞大小仅为几十mV,该方法能有效避免干法刻蚀槽栅所引入的损伤,减少栅界面的缺陷。与ICP方法制备的器件相比,SAG槽栅结构GaN MOSFET器件表现出优异的阈值电压稳定性能[14],如图13所示,这一成果证明了选择区域外延技术制备GaN槽栅MOSFET的优越性以及该技术路线的可行性。

图13 采用SAG和ICP制备的GaN凹槽栅MOSFET阈值电压稳定性对比Fig.13 The threshold voltage stability of GaN MOSFET by SAG and ICP technique

5 国内发展状况

国内关于Si衬底GaN功率开关器件的研发工作起步较晚,总体水平与国际先进技术还有一定的差距。关于Si衬底GaN外延及器件等研究主要集中在高校和研究所[21-24,33,34,42],在产业发展方面,近几年风险投资公司相继涉足Si衬底GaN基电力电子材料与器件领域,如苏州能讯、江苏能华、南通清华同方、厦门三安等。同时Si衬底GaN功率开关器件也得到了一些传统Si基电力电子器件企业的重视,如杭州士兰微电子、上海新傲科技、重庆中航半导体、深圳方正微电等,但尚未有正式的产品推出。

尽管国内GaN功率电子器件起步晚于国际发达国家,但是国内功率半导体器件企业在这一领域的发展存在相当大的机遇。首先,GaN功率器件的技术路线尚未确定,目前商业器件所采用的技术路线多是临时性的解决方案,专利及技术发展空间巨大,在这方面我国与国际先进国家的差距并不大。如果国内龙头企业在国家“政、产、学、研、用、资”协同创新机制的引导下,利用第三代半导体材料大力推动我国的电力电子器件产业发展、实现功率电子器件产业的弯道超车的机会是非常大的。其次,Si衬底GaN功率开关器件的产业化环境在中国已经成熟,这一方面得益于半导体照明产业的发展,使得GaN材料产业不断成熟,另一方面得益于国家在 “十一五”和“十二五”期间大力扶持的Si基功率半导体及集成电路产业平台的成熟。最后,第三代半导体功率器件已经得到了中国政府的高度重视,被科技部列为国家重点研究计划 (2016年下半年开始实施)及国家重大科技专项——工程材料专项 (18专项)中的重要研究内容,将带动数百亿元的产业基金,助力中国GaN功率电子器件产业的腾飞。

6 结语

GaN基功率电子器件凭借其优异的性能,将成为未来功率电子应用的首选技术方案,在逐步实现商业化的进程中,将取得非常可观的市场份额。随着GaN高压(600 V以上)器件的产品化,与现有Si 基IGBT和MOSFET相比,其巨大优势将愈发显现出来。目前基于CMOS工艺的Si衬底上GaN功率开关器件的产业化方案主要是Cascode级联结构和p型栅结构的器件,这两种技术方案仅仅是现阶段的临时性过渡方案,以此打开GaN器件产业化的大门。而凹槽绝缘栅结构的常关型GaN MOSFET器件的产品化是业界公认的发展方向,以期实现更高性能的电力电子系统。鉴于采用传统的驱动和封装形式会导致GaN器件在高速开关工作状态下发生严重的寄生效应,因此需要在驱动和封装层面加以重新设计,如采用纯GaN驱动的单片集成方案,这将大幅度提升器件的工作特性。此外,GaN功率开关器件在工作状态下的长期可靠性和稳定性近来也成为产业界关注的重点之一。从现阶段的发展趋势来看,随着制造成本的下降和一些技术瓶颈的逐一突破,GaN功率器件将在高速开关等Si基功率器件无法满足的领域迅速得到发展与应用。未来几年将是GaN功率电子器件全面产业化的关键时期,我国需要紧紧抓住这一发展机遇,迎接挑战,努力追赶美、日、欧先进技术,实现电力电子领域的产业升级。

[1]Baliga B J.Trends in power semiconductor devices[J]. IEEE Trans.Electron Devices.,1996,43(10):1717-1731.

[2]Khan M A,Bhattarai A,Kuznia J N,et al.High electron mobility transistor based on a GaN/AlxGa1-xN heterojunction[J].Applied Physics Letters,1993,63(9):1214-1215.

[3]Zhang Naiqian,Moran B,DenBaars S P,et al.Kilovolt AlGaN/GaN HEMTs as switching devices[J].Physica Status Solidi(a),2001,188(1):213-217.

[4]Power sources manufacturers association[OL].(2013).http://www.psma.com/.

[5]Kuzuhara M.Nitride power devices:future perspectives[C]. Int.RCIQE/CREST joint workshop,Hokkaido University,March,2010:1-2.

[6]Okumura H.Present status and future prospect of wide gap semiconductor high power devices[J].Japanese Journal of Applied Physics,2006,45(10A):7565-7586.

[7]Masaaki K,Hirokuni T.Low-loss and high-voltage III-Nitride transistors for power switching applications[J].IEEE Trans.Electron Devices.,2015,62(2):405-413.

[8]Keller S,Parish G,Fini P T,et al.Metal organic chemical vapor deposition of high mobility AlGaN/GaN heterostructures[J].Journal of Applied Physics,1999,86(10):5850-5857.

[9]Baron N,Lin Hong.GaN devices for power electronics:patent investigation[DB/OL].France:Yole Développement,2015.http://www.i-micronews.com.

[10]Chowdhury S,Swenson B L,Wong M H,et al.Current status and scope of gallium nitride-based vertical transistors for high-power electronics application[J].Semiconductor Science and Technology,2013,28(7):074014-074021.

[11]Oka T,Ueno Y,Ina T,et al.Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a freestanding GaN substrate with blocking voltage of 1.6 kV[J]. Applied Physics Express,2014,7(2):0210021-0210023.

[12]Meneghesso G,Meneghini M,Zanoni E.Breakdown mechanisms in AlGaN/GaN HEMTs:An overview[J].Japanese Journal of Applied Physics,2014,53(10):1002111-1002118.

[13]Hsieh T E,Chang E Y,Song Yizuo,et al.Gate recessed quasi-normally off Al2O3/AlGaN/GaN MIS-HEMT with low threshold voltage hysteresis using PEALD AlN interfacial passivation layer[J].IEEE Electron Device Lett.,2014,35 (7):732-734.

[14]Sochacki T,Bryan Z,Amilusik M,et al.HVPE-GaN grown on MOCVD-GaN/sapphire template and ammonothermal GaN seeds:Comparison of structural,optical,and electrical properties[J].Journal of Crystal Growth,2014,394(15):55-60.

[15]Kizilyalli I C,Prunty T,Aktas O.4-kV and 2.8-mΩ·cm2vertical GaN p-n diodes with low leakage currents[J]. IEEE Electron Device Lett.,2015,36(10):1073-1075.

[16]Yaegassi S,Okada M,Saitou Y,et al.Vertical heterojunction field-effect transistors utilizing re-grown AlGaN/GaN two-dimensional electron gas channels on GaN substrates [J].Physica Status Solidi(c),2011,8(2):450-452.

[17]Nie Hui,Diduck Q,Alvarez B,et al.1.5-kV and 2.2-mΩ·cm2vertical GaN transistors on bulk-GaN substrates [J].IEEE Electron Device Lett.,2014,35(9):939-941.

[18]Egawa T.Development of next generation devices amidst global competition due to their huge market potential[C]. Ultimate in Vacuum ULVAC,2012,63:18-21.

[19]Marcon D,Saripalli Y N,Decoutere S.200 mm GaN-on-Si epitaxy and e-mode device technology[C].Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM),2015:16.12.11-16.12.14.

[20]Huang Xiucheng,Liu Zhengyang,Lee F C,et al.Characterization and enhancement of high-voltage cascode GaN devices[J].IEEE Trans.Electron Devices.,2015,62(2):270-277.

[21]Huang S,Jiang Q,Wei Ke,et al.High-temperature lowdamage gate recess technique and ozone-assisted ALD-grown Al2O3gate dielectric for high-performance normallyoff GaN MIS-HEMTs[C].Proceedings of the 2014 IEEE International Electron Devices Meeting(IEDM),2014:17.4.1. -17.4.4.

[22]Tang Cen,Xie Gang,Sheng Kuang.Enhancement-mode GaN-on-Silicon MOS-HEMT using pure wet etch technique [C].Proceedings of the Power Semiconductor Devices& IC’s(ISPSD),2015:333-336.

[23]Wang Maojun,Wang Ye,Zhang Chuan,et al.900 V/1.6 mΩ·cm2normally off Al2O3/GaN MOSFET on silicon substrate[J].IEEE Trans.Electron Devices.,2014,61(6):2035-2040.

[24]Yao Yao,He Zhiyuan,Yang Fan,et al.Normally-off GaN recessed-gate MOSFET fabricated by selective area growth technique[J].Applied Physics Express,2014,7(1):0165021-0165024.

[25]Wen Yuhua,He Zhiyuan,Li Jialin,et al.Enhancement-mode AlGaN/GaN heterostructure field effect transistors fabricated by selective area growth technique[J].Applied Physics Letters,2011,98(7):0721081-0721083.

[26]He Zhiyuan,Li Jialin,Wen Yuhua,et al.Comparison of two types of recessed-gate normally-off AlGaN/GaN heterostructure field effect transistors[J].Japanese Journal of Applied Physics,2012,51(5R):0541031-0541035.

[27]Yang Fan,Yao Yao,He Zhiyuan,et al.The suppression of background doping in selective area growth technique for high performance normally-off AlGaN/GaN MOSFET [J].Journal of Materials Science:Materials in Electronics,2015,26(12):9753-9758.

[28]Roussel P.GaN for power electronics[DB/OL].France:Yole Développement,2014.http://www.i-micronews.com.

[29]Lahrèche H,Vennéguès P,Tottereau O,et al.Optimisation of AlN and GaN growth by metalorganic vapour-phase epitaxy(MOVPE)on Si(111)[J].Journal of Crystal Growth,2000,217(1-2):13-25.

[30]Zhang Baijun,Liu Yang.A review of GaN-based optoelectronic devices on silicon substrate[J].Chinese Science Bulletin,2014,59(12):1251-1275.

[31]He Zhiyuan,Ni Yiqiang,Yang Fan,et al.Investigations of leakage current properties in semi-insulating GaN grown on Si(111)substrate with low-temperature AlN interlayers [J].Journal of Physics D:Applied Physics,2014,47(4):04 51031-0451038.

[32]Yang Yibing,Xiang Peng,Liu Minggang,et al.Effect of compositionally graded AlGaN buffer layer grown by different functions of trimethylaluminum flow rates on the properties of GaN on Si(111)substrates[J].Journal of Crystal Growth,2013,376:23-27.

[33]Ni Yiqiang,He Zhiyuan,Yang Fan,et al.Effect of AlN/ GaN superlattice buffer on the strain state in GaN-on-Si (111)system[J].Japanese Journal of Applied Physics,2015. 54(1):0155051-0155055.

[34]Ni Yiqiang,He Zhiyuan,Zhou Deqiu,et al.The influences of AlN/GaN superlattices buffer on the characteristics of AlGaN/GaN-on-Si(111)template[J].Superlattices and Microstructures,2015,83:811-818.

[35]Freedsman J J,Watanabe A,Yamaoka Y,et al.Influence of AlN nucleation layer on vertical breakdown characteristics for GaN-on-Si[J].Physica Status Solidi(a),2016,213 (2):424-428.

[36]Ni Yiqiang,Zhou Deqiu,Chen Zijun,et al.Influence of the carbon-doping location on the material and electrical properties of a AlGaN/GaN heterostructure on Si substrate [J].Semiconductor Science and Technology,2015,30(10):1050371-1050379.

[37]Meneghini M,Vanmeerbeek P,Silvestri R,et al.Temperature-dependent dynamic RON in GaN-based MIS-HEMTs:Role of surface traps and buffer leakage[J].IEEE Trans. Electron Devices.,2015,62(3):782-787.

[38]Uren M J,Möreke J,Kuball M.Buffer design to minimize current collapse in GaN/AlGaN HFETs[J].IEEE Trans. Electron Devices.,2012,59(12):3327-3333.

[39]Lagger P,Ostermaier C,Pobegen G,et al.Towards understanding the origin of threshold voltage instability of Al-GaN/GaN MIS-HEMTs[C].Proceedings of the 2012 IEEE International Electron Devices Meeting(IEDM),2012:13.1. 1-13.1.4.

[40]Wu Tianli,Marcon D,Bakeroot B,et al.Correlation of interface states/border traps and threshold voltage shift on Al-GaN/GaN metal-insulator-semiconductor high-electron-mobility transistors[J].Appl.Phys.Lett.,2015,107(9):0935071-0935074.

[41]Zheng Yue,Yao Yao,Yang Fan,et al.The improvement of threshold voltage stability on normally-off AlGaN/GaN MOSFET by selective area growth[C].The 11th International Conference on Nitride Semiconductors(ICNS-11),2015.

[42]马焕,王康平,杨旭,等.GaN器件的LLC谐振变换器的优化设计[J].电源学报,2015,13(1):21-27. Ma Huan,Wang Kangping,Yang Xu,et al.Optimal design of GaN-based LLC resonant converter[J].Journal of Power Supply,2015,13(1):21-27(in Chinese).

Recent Progress and Challenges of GaN Based Power Electronic Devices

HE Liang1,2,LIU Yang1,2

(1.School of Electronics and Information Technology,Sun Yat-Sen University,Guangzhou 510275,China;2.Institute of Power Electronics and Control Technology,Sun Yat-Sen University,Guangzhou 510275,China)

GaN-based materials have bright market prospects in the field of high-temperature,high-speed and high-power applications owing to their superior physical properties.GaN-based power devices on Si substrate are current mainstream techniques,in which p-gate and cascade structure have been applied in industrial productions such as universal power supply and PV inverter.In view of the disadvantages of the above two kinds of device structure,highperformance true normally-off MOSFET is still recognized as the direction and goal in the industry.GaN MOSFET devices still face many technical bottlenecks and challenges in terms of materials epitaxy and devices stability.

GaN;GaN power electronic devices on Si substrate;GaN MOSFET;industrialization

何亮

10.13234/j.issn.2095-2805.2016.4.1

O472.4

A

2016-05-11 基金项目:国家自然科学基金资助项目(51177175);国家高技术研究发展计划(863计划)资助项目(2014AA032606);广东省自然科学基金资助项目(2015A030312011) Project Supported by the National Natural Science Foundation of China(51177175);the National High-tech R&D Program of China(863 Program)(2014AA032606);Guangdong Natural Science Foundation(2015A030312011)

何亮(1988-),男,博士研究生,研究方向:GaN材料外延生长及电力电子器件制备,E-mail:he_liang_mail@163.com。

刘扬(1969-),男,并列第一作者,通信作者,博士,教授,研究方向:宽禁带半导体材料与器件,E-mail:liuy69@mail.sysu.edu. cn。