基于SoPC的微小卫星姿态控制器的设计与实现*

范 凯 康国华 许 蕾 周琼峰 潘俊帆

南京航空航天大学微小卫星研究中心, 南京 210016

基于SoPC的微小卫星姿态控制器的设计与实现*

范 凯 康国华 许 蕾 周琼峰 潘俊帆

南京航空航天大学微小卫星研究中心, 南京 210016

为提高微小卫星姿控系统的集成度、实时性、灵活性和可扩展性,本文运用SoPC技术设计了一种基于Nios Ⅱ 双核架构的微小卫星姿态控制器。在一片FPGA内嵌入2个Nios Ⅱ 软核,分别处理外设通信和姿控算法,双核通过共享存储器实现信息交互。该系统还封装了自行设计的外设接口IP核和各类数学运算IP核,分别实现多路并行外设通信和姿控算法的硬件加速。该系统也可以在上述基础上针对不同的应用需求,封装不同的IP核以实现系统的扩展和性能的提升。本文从构架设计、硬件选型、软件编排和任务调度等角度对系统进行了描述,最后以三轴气浮台模拟卫星本体作为控制对象,进行了全物理仿真实验,实验结果的统计表明,该姿态控制器功能齐全,性能稳定,可应用于实际的微小卫星姿控系统。关键词 微小卫星;姿控系统;SoPC;全物理仿真

现代微小卫星要求体积小、重量轻、功耗低[1],因此如何在有限的成本、体积、重量及功耗的约束下,设计出集成度高、实时性好和灵活性强的姿控系统是微小卫星领域关注的重点[2]。

微小卫星姿态控制系统包括姿态敏感器、姿态控制器和执行机构[3],其中姿态控制器作为姿控系统的核心部分,其体系架构和运作方式直接影响了姿控系统的性能。

随着微电子技术的快速发展,SoPC(可编程片上系统)已成为电子系统设计新的发展方向[4]。SoPC技术是将大规模的数字逻辑和嵌入式处理器整合在一块FPGA芯片内,形成软硬件结合的具有控制和处理能力的片上系统[5],从而使系统在成本、体积、功耗以及性能等方面实现最优化[6]。

本文从提高微小卫星姿控系统的集成度、实时性、灵活性和可扩展性的角度考虑,将SoPC技术运用到微小卫星姿控系统中进行软硬件协同设计,提出了一种基于Nios Ⅱ 双核架构的微小卫星姿态控制器。

目前,也有很多文献设计了各种不同架构的微小卫星姿态控制器,文献[7]将386ex芯片运用到微小卫星星载姿态控制器中,但386ex CPU运算速度偏低,且体积和功耗均不理想,而SoPC技术在单片FPGA上实现系统主要逻辑功能[8],在集成度、速度、体积和功耗等方面均有较大优势。文献[9-11]分别运用了PowerPC,SPARC,ARM架构的芯片,这些架构的处理器体系完善、功耗低、性能好、速度快,但硬件结构较为固定,无法根据需求扩展外设接口,而SoPC技术可以重新配置FPGA芯片的内部结构,形成新的电子系统,具有更好的灵活性和可扩展性。文献[12]采用了DSP+FPGA架构,这种架构发挥了DSP强大的数据处理能力和FPGA可灵活逻辑扩展的特点,但由于DSP和FPGA具有各自的全局时钟,当两者之间进行通信时,就会遇到跨时钟域的数据传输问题,可能会使系统进入亚稳定状态[13],只能通过一些方法将亚稳态的概率降到最低。而SoPC系统只有一个全局时钟,不存在跨时钟域数据传输问题,所以从根本上避免了亚稳态问题。

因此,基于SoPC的微小卫星姿态控制器的设计具有一定的研究意义,下文将从构架设计、硬件选型、软件编排和任务调度等角度对系统进行详细的描述。

1 姿态控制器总体架构设计

本文提出了一种新的微小卫星姿态控制器的体系架构,如图1所示。

图1 姿态控制器架构示意图

在1片FPGA内嵌入2个NiosⅡ软核处理器,协处理器通过调用外设接口IP核实现各种串行时序,并行地接收所有姿态敏感器的数据,同时进行解包解码,得到有效的传感器数据,存放在共享存储器中,并发出中断;主处理器接收到中断后一次性地从共享存储器中拿到批量式的传感器数据,然后调用数学运算IP核运行姿态确定和姿态控制算法,得到的控制指令和下行数据也是批量式地写到共享存储器中,由协处理器代理完成与执行机构的数据通信。

2 姿态控制器硬件设计

2.1 FPGA选型

目前全球大部分的FPGA产品都是由Altera和Xilinx两大厂商提供的[14],相比较而言:Xilinx的硬件功能稍强;Altera逻辑资源速度稍快,且软件智能程度更高,并拥有更高的性价比,所以本文选用Altera的Cyclone IV系列的EP4CE115F23C8N,它是Altera公司Cyclone系列产品中功耗最低的芯片,只需两路电源供电,就能正常运行和工作,拥有114480个逻辑单元,3888K的嵌入式存储器,266个18×18乘法器,280个用户IO口,支持Nios II 32位嵌入式处理器,其丰富的片内资源和超低的功耗有利于提高姿态控制器的集成度[15]。

2.2 存储器配置

为实现双核的运行,控制器配置如表1所示的各类存储器,其功能及参数如下。

2.3 双核系统搭建

本文在QuartusⅡ13.1开发环境下搭建姿态控制器硬件系统,利用Qsys组件进行内核开发。如图2所示,控制器搭载了2个NiosⅡ软核处理器,2个软核通过各自的Avalon-MM总线分别挂载了各种IP核以实现特定功能。

图2 双核系统架构示意图

双核都挂载了SDRAM/Flash的控制器IP核,以驱动各个外围存储器,同时均挂载了定时器为操作系统提供时钟节拍。

双核还共同挂载了一些从设备,2个处理器共用1个System ID号作为整个硬件系统的标识符。另外共同挂载了2片双端口RAM作为片内共享存储器。为访问SRAM作为片外共享存储器,还共同挂载了三态控制器和三态桥以及互斥硬核。

双核也各自挂载了一些不同的IP核以实现特定功能。主处理器的主要任务是运行姿态控制算法,为进行算法的硬件加速,在主处理器的总线上挂载了一些Altera公司提供的数学运算IP核,包括整数及浮点数的加法器、乘法器、除法器、比较器、转换器、平方根计算器及正弦/余弦计算器等。

协处理器的主要任务是与外设通信,因此挂载了多个自行设计的外设接口IP核,IIC接口IP核驱动FeRAM和其他IIC接口的外设;UART接口IP核通过串口电平转换电路可扩展出RS232,RS422,RS485等各类异步串行接口;ADC IP核用以采集外部的模拟量信号;DAC IP核用以输出模拟电压信号驱动动量轮;PWM波IP核用以驱动喷气电磁阀。

2.4 硬件实现

根据总体方案进行硬件详细设计,最后姿态控制器实物如图3所示。姿态控制器电路板采用核心板和扩展板层叠的结构,方便升级和扩展,如图3左边是扩展板,右边是核心板,插在扩展板背面。

图3 姿态控制器实物图(左:功能扩展板;右:核心板)

3 姿态控制器通信机制设计

3.1 内部双核间通信机制设计

双核处理系统的数据共享机制是一个难点[16],特别是在高速、并发情况下,如何有效保证数据安全是本文设计的重点,根据实际情况设计了2种方案,分别应用在不同场景中。

3.1.1 基于共享SRAM和互斥硬核的通信机制

双核共同挂载了1片SRAM作为片外共享存储器,基于硬件互斥核Altera Avalon Mutex的操作机制实现对共享资源分时访问,每个软核在使用共享资源前,都要测试互斥核是否可用:若可用,则试图对Mutex加锁,确认加锁成功、取得使用权后才能对共享资源操作,直到使用完再对Mutex解锁;若不可用,则根据操作指令选择继续等待或者立即返回。

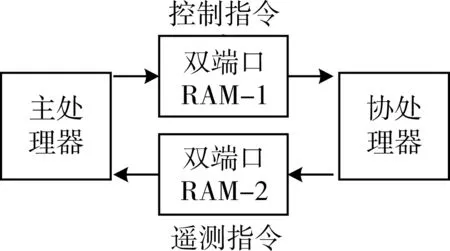

3.1.2 基于双端口RAM和IO中断的通信机制

利用FPGA的片上逻辑资源构建了2片双端口RAM同时挂在双核的总线上。该双端口RAM自带防竞争机制,当处理器A读某一地址,而处理器B正在对同一地址写数据时,处理器A读到的是前一时刻的数据,不会出现错误。所以只要避免2个处理器同时对同一地址执行写操作即可。因此配置了2片双端口RAM,连接关系如图4所示。

图4 双端口RAM数据通信

主处理器将控制指令写到RAM-1中,并发出IO中断,然后协处理器从RAM-1中读取控制指令,写到执行机构中。对于RAM-1,主处理器只写不读,协处理器只读不写;协处理器接收遥测指令,写到RAM-2中,并发出IO中断,然后主处理器从RAM-2中读取遥测指令,运行控制程序。对于RAM-2,协处理器只写不读,主处理器只读不写。

对比这2种通信机制,SRAM能实现双向的数据交换,但操作比较繁琐;每片双端口RAM设置成了单向模式,但操作比较灵活。因此对于一些需要双向流动的共享数据,选择基于SRAM的通信方案;而对于单向流动的共享数据,选择基于双端口RAM 的通信方案。

3.2 姿态控制器与外设通信机制设计

姿态控制器需要与众多姿态敏感器进行通信,这些敏感器大多是UART,SPI,IIC等慢速串行接口,如果仅用1个CPU顺序采样,难以保证采样任务不被其他高优先级的任务打断,影响了通信的实时性。因此,本文提出了一种新的批量式数据通信机制,这种机制下各模块的逻辑关系如图5所示。

图5 双核与外设通信机制设计

在1片FPGA上开发了多个外设接口IP核,其中,时序发生器负责产生指定时序与外设通信,通信数据存放在FIFO中。通信控制器负责配置时序发生器的通信速率等参数,以及读写FIFO的数据和状态,并转换成Avalon总线信号传送给协处理器。协处理器以基址加上偏移量的方式访问IP核各个寄存器的内容。协处理器读写好的外设数据通过片内双端口RAM和片外SRAM与主处理器共享。

从外设接收数据时,时序发生器产生指定的串行时序,并行地从传感器读取数据写入FIFO中,满一定数据量后触发中断,协处理器寻址获取接收的数据,并进行解包解码,得到有效的传感器数据,所有传感器数据读取完成后,统一写入共享存储器,并向主处理器发出中断,主处理器一次性地从共享存储器中获取所有传感器数据。

向外设发送数据时,主处理器将需发送的数据一次性全部写到共享内存中并发出中断,协处理器接收到中断后,从共享内存中获取数据,分别写入指定IP核的FIFO中,一旦时序发生器检测到FIFO不为空,就根据设定的通信速率产生相应的时序,将FIFO中的数据依次发送出去。

通过以上设计,主处理器得以从繁琐的外设通信中解放出来,转而由协处理器代理。协处理器通过调用各外设接口IP核实现与外设的多路并行通信,提高了通信的实时性。

4 姿态控制器软件设计

姿态控制软件程序基于Nios II 13.1 SBT for Eclipse开发,为2个软核处理器分别建立了NiosⅡ Application工程,并都嵌入了μC/OS-Ⅱ操作系统。

4.1 协处理器软件程序设计

协处理器的任务主要是与姿态敏感器和执行机构通信。协处理器共有5个任务,各任务间交互关系如图6所示。

图6 协处理器各任务间的交互关系

3个串口接收IP核实时接收光纤陀螺、磁强计和加速度计的数据,达到一定数据量触发中断,发出信号量激活陀螺、磁强计和加速度计的数据采集任务,以状态机的方法进行解包解码,得到的传感器数据分别通过消息邮箱发出。姿态敏感器数据处理任务由定时器每10ms激活,无等待的获取以上消息邮箱的消息;读取所有姿态敏感器的数据后,按照Mutex机制将数据写入SRAM,并发出一次I/O口中断;然后读取双端口RAM-1中主处理器传来的控制指令数据,通过消息队列发送给控制指令处理任务。控制指令处理任务等待消息队列中的消息,通过消息首字符分离出各执行机构的指令,然后调用D/A转换接口IP核控制动量轮转速,调用PWM输出IP核控制喷气电磁阀开关。

4.2 主处理器软件程序设计

主处理器的任务是建立工作时序,首先读取协处理器传来的姿态敏感器数据,然后运行姿态确定和姿态控制算法,最后得到执行机构控制指令返回给协处理器。这里的姿态控制采用了角度和角速度的双回路增量式PID控制算法。主处理器共有4个任务,各任务间的交互关系如图7所示。

图7 主处理器任务交互关系

当协处理器把所有姿态敏感器的数据写到SRAM后,会发出1次I/O中断,主处理器检测到这个中断后发出2个信号量:1)激活SRAM数据处理任务,按照Mutex机制从SRAM中批量式的读取所有传感器数据,然后将传感器数据通过消息邮箱发出;2)激活双端口RAM-2数据读取任务,读取协处理器接收到的遥测指令并通过消息邮箱发出。

姿态控制任务通过消息邮箱读取当前传感器数据和遥测指令;运用AHRS算法融合陀螺、加速度计和磁强计的数据,解算出当前的姿态信息;然后根据遥测指令更新控制参数和目标姿态,运行姿态控制算法,计算得到的控制指令通过邮箱发出。双端口RAM-1存储任务接收消息将控制指令存储到双端口RAM-1中,由协处理器代理驱动执行机构。

5 全物理仿真与验证

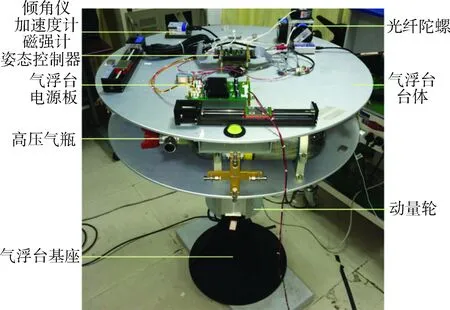

为了验证姿态控制器的功能和性能,用三轴气浮台模拟卫星本体作为控制对象,进行全物理仿真实验。

5.1 全物理仿真平台的搭建

将本文设计的姿态控制器固定于气浮台台体上,并与各姿态敏感器和执行机构相连,组成全物理仿真平台如图8所示。

图8 姿控仿真系统实物图

气浮台采用球面气浮轴承,提供三自由度微干扰力矩悬浮。台体配平以后的惯量矩阵如下所示。

各传感器的主要参数如表2所示。

表2 气浮台传感器性能参数

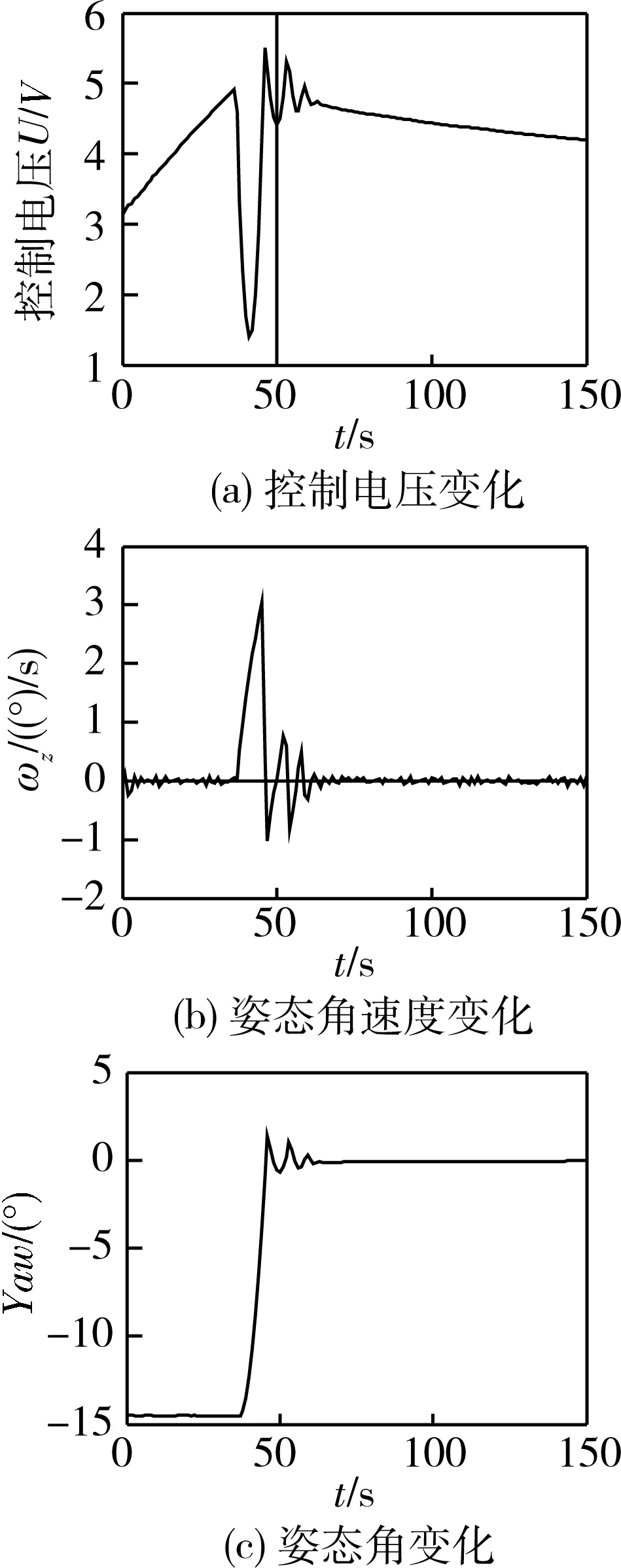

5.2 试验结果分析

姿控要求:气浮台XY面保持水平,即横滚和俯仰角保持0°,实现偏航角从14.5°到0°的姿态机动,最后稳定在0°。指标要求姿态指向精度优于0.2°,指向稳定度优于0.01 (°) /s。

实验过程典型姿态数据如图9所示。

图9 系统全物理仿真姿态控制效果

从图9(c)可以看出,由0s开始,台体偏航角保持指向14.5°,在40s时,接收到指令,偏航角向0°机动,最后稳定在0°附近。偏航角机动是一个典型的控制系统调节过程,其动态特性是:上升时间6s,峰值时间7s,动态偏差1.39°,震荡周期8s,调节过程时间21s。静态特性是:在65s时,系统达到了新的平衡,静态偏差为0.061°。图9(a)和(b)分别反映了台体在姿态机动过程中控制指令和姿态角速度的变化过程。

按上述要求进行多次重复试验,经过统计分析控制指标得出偏航角指向精度为0.065°,指向稳定度为0.0029 (°) /s,达到设计指标。

6 结论

运用SoPC技术设计了一种基于NiosⅡ双核架构的微小卫星姿态控制器,在一片FPGA上实现了整个姿态控制器的逻辑功能,提高了集成度;用VHDL语言编写了所有外设接口,将硬件软件化,提高了灵活性和可扩展性;设计了一种基于双核的批量式外设通信机制,从底层保证了系统的实时性。基于三轴气浮台的全物理仿真实验验证了本姿态控制器具有较好的姿控性能与效果。后期将对姿态控制器的可靠性展开深入研究。

[1] 廖文和. 立方体卫星技术发展及其应用[J]. 南京航空航天大学学报,2015,47(6):792-797.(Liao Wenhe. A Survey of Cubesat Technology Development and Applications [J]. Journal of Nanjing University of Aeronautics and Astronautics, 2015, 47(6): 792-797.)

[2] 谢祥华. 微小卫星姿态控制系统研究[D]. 南京:南京航空航天大学,2007.(Xie Xianghua. Study on Micro-satellite Attitude Control System [D]. Nanjing : Nanjing University of Aeronautics and Astronautics, 2007.)

[3] 樊雯,程月华,姜斌,等. 卫星姿态控制系统的可重构性分析[J]. 宇航学报,2014, 35(2): 185-191. (Fan Wen, Cheng Yuehua, Jiang Bin,et al. Reconfigurability Analysis for Satellite Attitude Control Systems [J]. Journal of Astronautics, 2014, 35(2): 185-191.)

[4] Hsu Yuan-Pao, Shih Bo-Tang. An SoPC-based Object Tracking Quadrotor [J]. Journal of the Chinese Institute of Engineers, 2016, 39(3): 254-264.

[5] Chen Han-Chiang, Huang Y-M, Su Chia-Hung, Chiu Te-Wei. Implementation of SOPC Based Telecom & Datacom for Monitoring Wireless Sensor Networks [J]. Telecommunication Systems, 2013, 52(4): 2325-2333.

[6] 刘仁伟. 基于SOPC的嵌入式系统的设计[D]. 电子科技大学,2007.(Liu Renwei. Design of Embedded System Based on SOPC [D]. University of Electronic Science and Technology, 2007.)

[7] 华更新,王国良,郭树玲. 星载计算机抗辐射加固技术[J]. 航天控制,2003,21(1):10-15,21.(Hua Gengxin, Wang Guoliang, Guo Shuling. Radiation Hardening Techniques for On-board Computers [J]. Aerospace Control, 2003,21(1): 10-15,21.)

[8] 梁海波,司文杰,刘志华,等. 基于SOPC的MEMS组合导航仪设计与实现[J]. 航天控制,2014, 32(2): 3-8. (Liang Haibo, Si Wenjie, Liu Zhihua,et al. De sign and Realization of MEMS Integrated Navigator

Based on SOPC [J]. Aerospace Control, 2014, 32(2): 3-8.)

[9] 胡志丹. 星载计算机中商用处理器容错关键技术研究[D].国防科学技术大学研究生院,2009.(Hu Zhidang. Research on Fault-Tolerant On-board Computer System Based on Commercial Processors [D]. Graduate School of National University of Defense Technology, 2009.)

[10] 谢浩. 基于国产CPU(SPARCV8)的星载计算机技术研究[D]. 中国科学院研究生院,2007.(Xie Hao. Study of On-board Computer Technology Based on Domestic CPU(SPARC V8) [D]. Graduate School of Chinese Academy of Sciences, 2007.)

[11] 王新升,孙汉旭,徐国栋. 基于ARM处理器的星载计算机系统研究[J]. 北京邮电大学学报,2005,28(4):23-26.(Wang Xinsheng, Sun Hanxu, Xu Guodong. Study on the On-Board Computer System Based on ARM Processor [J]. Journal of Beijing University of Posts and Telecommunications, 2005, 28(4): 23-26.)

[12] 易进. 小卫星姿控系统设备模拟器研制[D].哈尔滨工业大学,2014.(Yi Jin. Development of Attitude Control System Device Simulators for Micro-satellite [D]. Harbin Institute of Technology, 2014.)

[13] 胡波,李鹏. 异步FIFO在FPGA与DSP通信中的运用[J]. 电子科技,2011,24(3):53-55,61.(Hu Bo, Li Peng. Application of Asynchronous FIFO in Communication between FPGA and DSP [J]. Electronic Science and Technology, 2011, 24(3): 53-55,61.)

[14] LIN Haifeng, MAO Ruili. Research on Design of a Management System for a Power Source Equalizing Charge Based on FPGA Control [J]. International Journal of Online Engineering, 2016, 12(2): 20-24.

[15] Chakrapani K, Neelamegam P. NIOS II Based Secure Test Wrapper Design for Testing Cryptographic Algorithms [J]. International Journal of Applied Engineering Research, 2015, 10(11):27613-27621.

[16] Li Hefei, Xu Cuiping, Tian Chunyu. The Asymmetric Coupler Based on the Dual-core PCF [J]. In Optik-International Journal for Light and Electron Optics January, 2016, 127(2): 694-696.

Design and Implementation of Micro-Satellite Attitude Controller Based on SoPC

Fan Kai, Kang Guohua, Xu Lei, Zhou Qiongfeng, Pan Junfan

Research Center of Microsatellites, Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China

Aimingatimprovingtheintegration,instantaneity,flexibilityandscalabilityofmicro-satelliteattitudecontrolsystem, SoPCtechnologyareemployedtodesignanewmicro-satelliteattitudecontrollerthatisbasedonNios IIdual-corearchitecture.ThetwoNios IIsoft-coresembeddedinoneFPGAaretreateddividedlyperipheralcommunicationsandattitudecontrolalgorithms.Theyexchangeinformationviasharedmemory.Thesystemalsoencapsulatestheself-designedperipheralinterfaceIPcoreandvarioustypesofmathIPcore,respectively,toachievemulti-channelparallelperipheralcommunicationsandhardwareaccelerationforattitudecontrolalgorithm.ThesystemcanalsopackagedifferentIPcoresfordifferentrequirementstoachieveexpansionandenhancetheperformanceofthesystem.Inthepaper,thesystemisdescribedbyarchitecturedesign,hardwareselection,softwareschedulingandtaskscheduling.Finally,three-axisair-bearingtableisusedtoimitatesatellitebodyasacontrolobjectandconductafull-physicalsimulationexperiment.Theresultoftheexperimentshowsthatthisattitudecontrollerhasfullfeaturesandstableperformanceanditcanbeappliedtoactualmicro-satelliteattitudecontrolsystem.

Micro-satellite;Attitudecontrolsystem; SoPC;Full-physicalsimulation

*江苏省自然基金青年基金项目(SBK201343261);中央高校基本科研业务费专项资金资助(NS2014092)

2016-07-01

范 凯(1992-),男,江苏扬州人,硕士研究生,主要研究方向为微小卫星姿态控制技术;康国华(1978-),男,福建南平人,博士,研究员,主要研究方向为微小卫星总体设计;许 蕾(1977-),男,安徽无为人,博士,助理研究员,主要研究方向为无人机飞行控制;周琼峰(1993-),女,浙江金华人,硕士研究生,主要研究方向为微小卫星导航技术;潘俊帆(1992-),男,北京人,硕士研究生,主要研究方向为微小卫星结构设计。

V249

A

1006-3242(2016)05-0039-07