基于FPGA的冗余CAN总线通信节点设计

孙大元,闫 冬

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

基于FPGA的冗余CAN总线通信节点设计

孙大元,闫冬

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

摘要针对航天领域对通信系统可靠性要求高的特点,提出了基于FPGA、SJA1000和PCA82C250的冗余CAN总线通信节点设计。介绍了CAN总线冗余方式的选择原则,详细给出了采用控制器级冗余方式的通信节点硬件设计和FPGA控制程序设计,重点对SJA1000初始化流程、收发报文处理过程、SJA1000错误处理过程和链路热备份条件下的数据选择策略进行了说明。通过FPGA程序仿真,验证了收发报文时SJA1000的控制时序,进行了高低温条件下的节点传输性能测试和冗余数据处理功能测试。测试结果证明,节点工作稳定性高、实时性强,适用于航天和航空等高可靠性要求的领域。

关键词CAN总线;FPGA;冗余;CAN控制器;SJA1000

0引言

Control Area Network(CAN)总线是一种采用异步串行方式工作的现场总线,最早由德国BOSCH公司提出用于实现汽车内部控制[1],由于其传输速率高,抗电磁干扰性能强,同时配置灵活,使用方便,所以被越来越多地应用于航天领域,近年来我国发射成功的多颗小卫星都采用了CAN总线通信系统[2]。星上设备长时间在高低温、真空和辐射等恶劣条件下工作,且故障后不可维护,因此对总线可靠性提出了更高的要求。

在传统的CAN总线通信系统中,通常采用单片机作为总线节点的处理器,但是单片机处理速度慢、抗干扰能力差的缺点使其在航天领域应用中受到很大限制。本文针对航天应用的特点,提出了一种基于FPGA作为处理器的总线节点设计方案,同时为了进一步提高系统可靠性,对节点进行了控制器级的冗余设计,使总线通信链路由1条变为互为热备份的2条,在保证系统实时性不受影响的同时,极大地提高了系统的可靠性。

1总体设计

1.1冗余方式选择

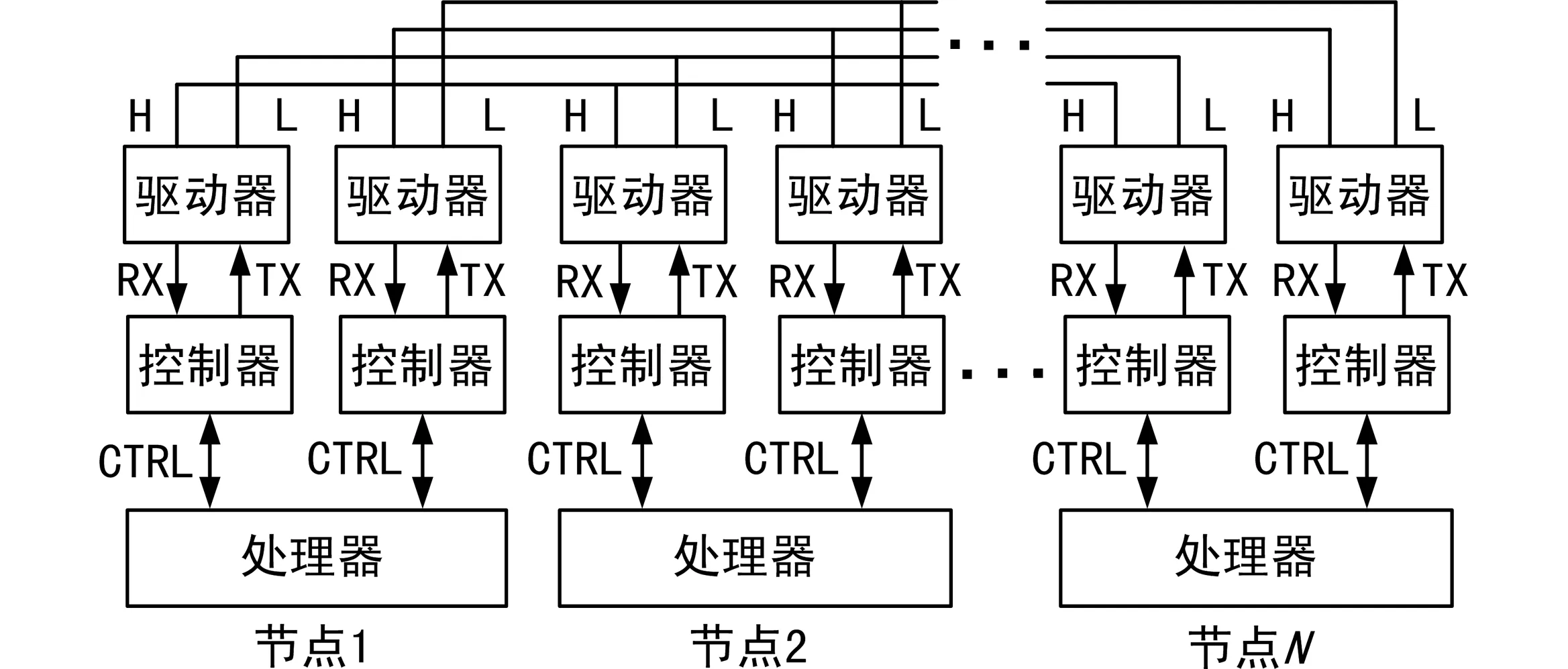

CAN总线的冗余设计分为驱动器冗余、控制器冗余和处理器冗余3种方案[3]。驱动器冗余方案中通信节点包括:1个处理器、1个CAN控制器、2个CAN驱动器和1个切换电路,工作时由处理器控制切换电路进行2个CAN驱动器间的选择,该方案实现较为简单,但如果控制器出现故障会导致系统无法工作,对节点可靠性的提升相对较小。控制器冗余方案中通信节点由1个处理器、2个CAN控制器和2个CAN驱动器来实现,此时2条CAN链路独立,对节点可靠性有很大提高。处理器冗余方案中通信节点包括2个处理器、2个CAN控制器和2个CAN驱动器,该方案实现了硬件上的完全独立,冗余度最高,但处理器的增加会使节点软硬件复杂度极大提高。航天应用中对节点的体积、功耗等指标要求较为严格,并且处理器芯片等级一般为军品级或宇航级,成本较高,因此不适宜采用处理器冗余方案,而驱动器冗余方案对系统可靠性的提升有限,同样不适用于高可靠性要求的场合。本文设计选择使用控制器冗余方案,2条链路热备份,即处理器同时通过2条链路收发数据,与冷备份相比,热备份方案虽然使系统功耗有所增加,但其可靠性更高、实时性更好。采用控制器冗余方案的CAN总线系统结构框图如图1所示[4]。

图1 控制器冗余CAN总线系统结构

1.2节点硬件设计

CAN总线节点硬件包括总线驱动器、协议控制器和处理器[5]。总线驱动器提供协议控制器与物理总线之间的接口,完成信号电平控制,协议控制器执行CAN总线协议,实现报文收发缓冲、总线错误处理等功能[6]。处理器对协议控制器操作,完成CAN总线工作模式选择、工作参数设置以及报文的发送和接收。CAN通信节点硬件组成框图如图2所示。

图2 CAN通信节点硬件组成

本设计中协议控制器和总线驱动器分别选择Philips公司的SJA1000和PCA82C250[7]。同时为提高节点的抗干扰能力,在SJA1000与PCA82C250之间增加光耦6N137,以实现CAN节点与总线通道的电气隔离。节点处理器FPGA选择XILINX公司的XQ4VSX55,由于FPGA与SJA1000之间接口电平不匹配,因此在二者之间增加双向总线收发器54AC164245,实现3.3 V TTL电平与5 V TTL电平之间的转换[8]。

1.3SJA1000工作方式

1.3.1SJA1000初始化

系统上电后首先需要对SJA1000进行初始化,通过设置模式寄存器、中断使能寄存器、验收代码寄存器、验收屏蔽寄存器、总线定时寄存器、输出控制寄存器和时钟分频寄存器完成SJA1000工作模式的选择、各类中断的使能、报文滤波的设置、波特率的设置以及输出特性的选择[9]。SJA1000的初始化必须在复位模式中进行,系统上电后,FPGA给SJA1000的RST管脚输出一个负脉冲,脉冲结束后通过读取模式寄存器RM位的值判断SJA1000是否进入复位模式,如果成功进入复位模式则依次给各个寄存器赋值,赋值完毕后,将模式寄存器的RM位写0,退出复位模式,进入工作模式。

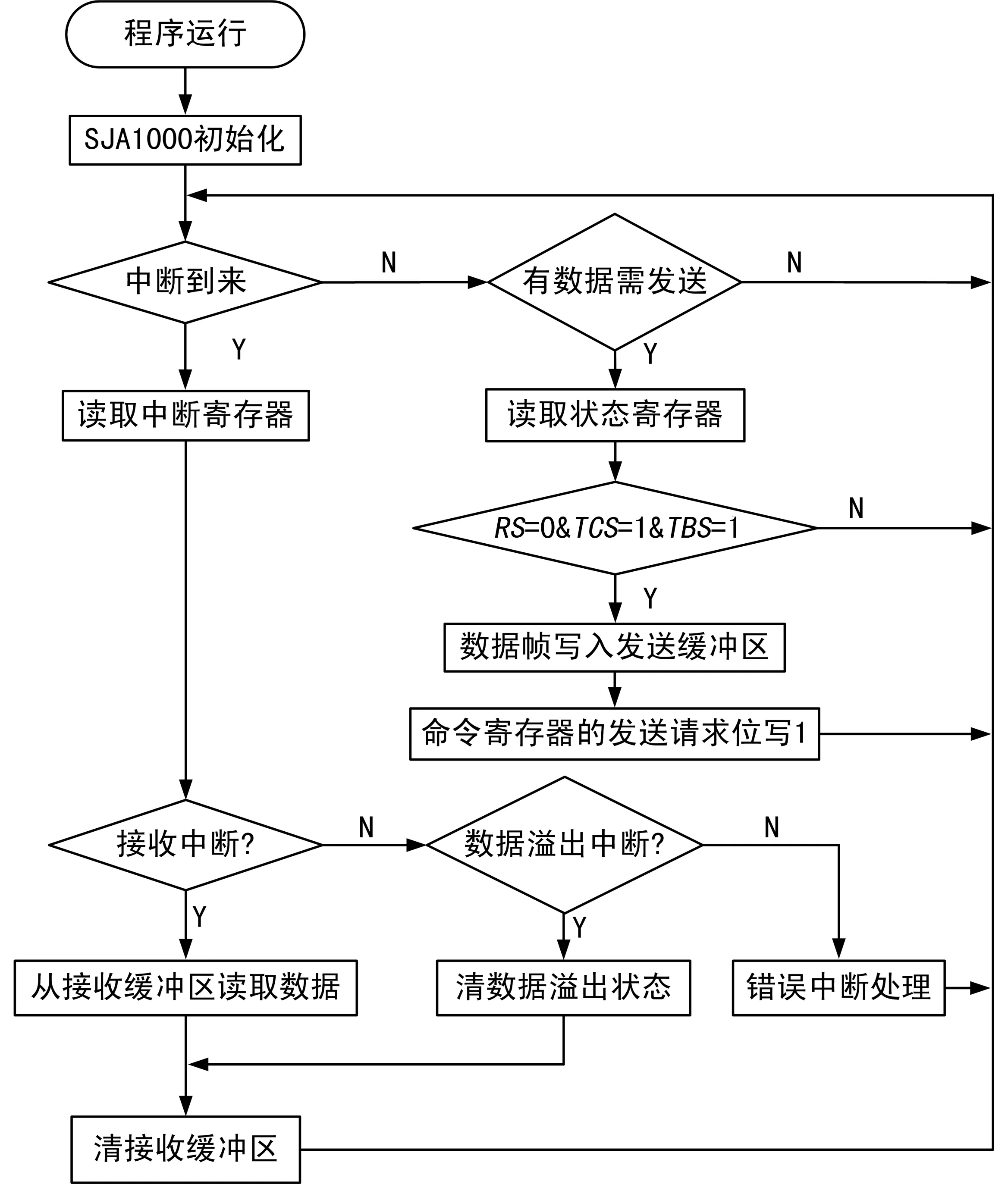

1.3.2报文发送

报文发送过程可以通过SJA1000的中断请求或查询状态标志控制实现,本设计中选择使用查询状态标志的方式发送数据。在发送数据之前,需要通过读取状态寄存器的接收状态位、发送完毕状态位以及发送缓冲区状态位值判断当前SJA1000是否具备发送条件,只有当接收状态位为0(空闲),发送完毕状态位为1(完毕),发送缓冲区状态位为1(非锁定)时,才可以进行发送。发送报文时,FPGA将报文内容、帧信息和标识符写到SJA1000的发送缓冲区,之后将命令寄存器的发送请求位写1,启动SJA1000发送。

1.3.3报文接收

与发送报文过程相同,接收报文也可以通过中断或查询2种方式实现。接收数据过程是被动的,如果采用查询方式,程序需要不断读取SJA1000的接收缓冲区状态来确认是否接收到了数据,实时性较差。因此,本设计中采用中断请求的接收方式[10]。设计中使用3种类型的中断:接收中断、数据溢出中断和错误中断,程序接收到中断后,通过读取中断寄存器判断中断类型,如果为接收中断,则读取接收缓冲区内容并释放接收缓冲区;如果为数据溢出中断,则清数据溢出状态并释放接收缓冲区,否则中断类型为错误中断,进行相应的处理。

1.3.4错误处理

本设计中SJA1000工作于PeliCAN模式,此时总线上出现错误的次数会在发送错误计数寄存器和接收错误计数寄存器的值上体现,如果错误计数器的值大于255,则总线会进入关闭状态,从而导致通信中断,该状态不会自主恢复,必须由程序进行处理[11]。程序接收到中断并通过中断寄存器的值判断类型为错误中断后,读取模式寄存器的值,如果其RM位为1则说明总线关闭,SJA1000进入复位状态,此时需重新进行SJA1000初始化流程,使SJA1000恢复工作状态。

1.3.5SJA1000控制流程

SJA1000控制程序工作流程如图3所示。程序运行后首先进行SJA1000初始化,初始化完成后进入空闲等待状态,如果在等待状态中有中断到来则进行中断类型判断并进行相应的处理,如果有数据需要发送则在确认发送条件满足后进行发送。

图3 SJA1000控制程序工作流程

2冗余处理

冗余处理是节点设计中的关键部分。在其他相关文章中,基本都是采用冷冗余方案,2条CAN总线链路中同时只有一条链路工作,当判断当前链路工作异常后,进行链路切换和数据重发。冷冗余方案虽然保证了冗余链路的增加不会提高节点功耗,但链路切换、数据重发机制会导致系统的实时性大大降低。本设计中采用了热冗余方案,2条CAN总线链路同时工作,互为热备份。发送报文时,数据通过2条链路同时发送,当一条链路出现故障时,另一条链路工作不受影响,保证了系统的实时性。接收报文时,节点需要对2条链路上的数据进行甄别、选择,避免同一条报文的重复接收,具体选择策略为:节点在一条链路上接收到一帧数据帧后,记录其帧类型码,如果在小于T的时间间隔内在另一条链路上收到了一帧具有同样类型码的数据帧,则认为该帧与之前接收的数据帧为同一帧,将其丢弃,其中时间间隔T根据不同类型报文的发送频率等条件灵活设置。与冷冗余方案相比,本设计中采用的热冗余方案实时性更好,判决策略简单,可靠性更高。

3FPGA顶层模块设计

FPGA顶层模块如图4所示。

图4 FPGA顶层模块功能

其中SJA1000_CTRL为SJA1000控制模块,负责完成SJA1000初始化、报文发送、报文接收以及SJA1000的错误处理[12]。SEND_FIFO为发送数据缓存FIFO,用于缓存待发送数据,实现前后端数据速率匹配,当FIFO中存储数据量大于预置的发送门限后,SEND_FIFO通过将其使能标志S_EN置1,告知SJA1000_CTRL模块有数据需要发送。RECIEVE_FIFO为接收数据缓存FIFO,用于存储从SJA1000读取到的数据,当FIFO接收完一帧数据帧后,RECIEVE_FIFO读使能标志R_EN置1,告知REDUNDANT_SEL模块将数据读出并进行处理。REDUNDANT_SEL模块负责冗余数据处理,完成2条链路数据的冗余判断和选择接收。

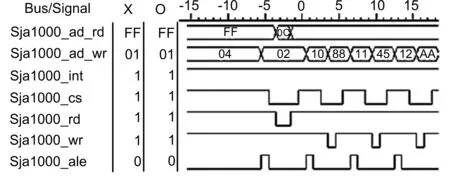

4仿真验证

FPGA程序设计通过ISE和Modelsim软件进行了综合以及功能仿真,并通过ChipScope软件进行FPGA程序的在线调试,主要对SJA1000控制模块收发数据时的信号时序进行了验证。发送数据内容为固定0xAA,接收数据内容为0x06、0x07、0x08、0x09、0x0A、0x0B、0x0C和0x0D,ChipScope中截取发送、接收数据时的相关信号波形如图5和图6所示。

图5 发送数据时的信号波形

图6 接收数据时的信号波形

5测试结果

利用周立功公司的USB-CAN II调试器和配套的CANtest软件进行了节点软硬件性能测试验证。首先对硬件性能进行了测试,测试内容为不同波特率、高低温条件下时的总线传输性能。测试中计算机通过调试器以5 ms为间隔给CAN节点发送固定内容数据帧,CAN节点收到数据帧后给将收到的帧内容发送回计算机,并且每隔1 s查询一次SJA1000总线错误寄存器值发送给计算机,计算机通过CANtest软件监测CAN节点发送帧数、帧内容以及SJA1000错误寄存器值,分析节点硬件性能,测试结果如表1所示。通过表1的测试结果可见,在高低温条件下,节点硬件工作均稳定可靠。

硬件性能测试完成后对冗余功能进行了测试验证。测试中计算机以20 ms间隔分别通过2条链路给CAN节点发送固定内容数据帧,CAN节点收到一帧数据帧后程序中的接收帧计数加1,同时将帧计数通过2条链路发送回计算机,计算机通过CANtest软件监测CAN节点返回的帧内容。分别测试2条链路之间发送时延小于T和大于T的情况,并测试2条链路发送同样帧类型码和不同帧类型码的情况,测试结果如表2所示。

表1 节点硬件性能测试结果

表2 冗余处理功能测试

从表2的测试结果可见,当2条链路上发送数据帧的帧类型码一致并且发送时延小于T,则节点将收到的2帧作为一帧处理,否则将2条链路上的数据帧认为是不同的2帧接收,测试结果与程序设计预期一致。

6结束语

采用FPGA作为CAN总线节点处理器,可靠性高,实时性好,接口灵活,并且应用层扩展方便,除航天应用外,在航空和高性能要求的工业控制等领域等都具有很好的适用性。通过在高低温条件下针对不同波特率进行总线传输性能测试,验证了节点在恶劣工作环境下的可靠性。

与大多数采用冷冗余方案的系统不同,本文采用的热冗余方案中,2条CAN总线链路同时工作互为热备份,当一条链路出现故障时另一条链路工作完全不受影响,不存在总线切换数据重发过程,系统实时性得到保证。

本设计经过测试验证后已成功应用于系统中,在轨工作稳定,为航空航天领域中的CAN总线系统设计提供了一种高可靠性的设计方案。

参考文献

[1]廉保旺,李勇,张怡.CAN总线系统设计与实现[J].无线电工程,2000,30(1):12-15.

[2]周新发,尚志,刘群.工业现场CAN总线技术在航天领域的应用[J].现场总线与网络技术,2006(1):60-63,96.

[3]禹春来,许化龙,刘根旺,等.CAN总线冗余方法研究[J].测控技术,2003,22(10):28-30.

[4]杨亮,贾庆轩,孙汉旭.冗余CAN总线系统设计[J].机电产品开发与创新,2007,20(5):4-5,8.

[5]邹志慧.CAN总线分析、实现及应用实例[J].无线电工程,2006,36(1):51-54.

[6]张培坤,高伟,宋宗喜,等.基于FPGA的CAN总线通信节点设计[J].仪表技术与传感器,2010(12):68-70.

[7]吴坎.基于SJA1000和PCA82C250的CAN总线接口设计[J].机械设计与制造,2010(7):55-57.

[8]苏虎平,沈三民,刘文怡,等.基于冗余CAN 总线的实时通信系统设计[J].总线与网络,2013(1):26-29,55.

[9]杜尚丰,曹晓钟,徐津.CAN总线测控技术及其应用[M].北京:电子工业出版社,2007.

[10]贾长春.基于SJA1000的CAN总线智能节点设计[J].工业控制计算机,2015,28(2):5-6.

[11]杜倩倩.双冗余CAN总线模块研制[D].哈尔滨:哈尔滨工业大学,2011.

[12]陈萍,姜秀杰.基于FPGA的CAN总线通信系统[J].计算机测量与控制,2009,17(12):2 482-2 484.

doi:10.3969/j.issn.1003-3106.2016.07.19

收稿日期:2016-03-09

基金项目:国家高技术研究发展计划(“863”计划)基金资助(SS2015AA011303)。

中图分类号TP391.4

文献标志码A

文章编号1003-3106(2016)07-0071-05

作者简介

孙大元男,(1985—),工程师。主要研究方向:航天测控。

闫冬女,(1985—),工程师。主要研究方向:航天测控。

Design of Redundancy CAN Bus Communication Node Based on FPGA

SUN Da-yuan,YAN Dong

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

AbstractIn view of the requirements for high reliability of the communication system in aerospace field,a design of redundancy CAN bus node is proposed based on FPGA,SJA1000 and PCA82C250.The selection principle of CAN bus redundancy mode is introduced,the hardware design of CAN bus node with controller redundancy and the design of the FPGA control program are described in detail.Then,the paper focuses on explaining the initialization flow of SJA1000,message sending/receiving process,error handling of SJA1000 and data selection strategy under hot backup condition of the link.The control timing of SJA1000 is verified by the simulation result of the FPGA program,and finally the transmission performance test under high and low temperature and the function test of redundancy data processing are made.The test results prove that the CAN bus node has high real-time performance and high stability,and the design is suitable for many fields which require high reliability such as space field and aviation field.

Key wordsCAN bus;FPGA;redundancy;CAN controller;SJA1000

引用格式:孙大元,闫冬.基于FPGA的冗余CAN总线通信节点设计[J].无线电工程,2016,46(7):71-75.