0.18 μm CMOS工艺的GPS/BDS双模可重构接收机射频前端*

江金光,唐亚男,周细凤,刘江华

(1.武汉大学 卫星导航定位技术研究中心, 湖北 武汉 430079; 2.武汉大学 物理科学与技术学院, 湖北 武汉 430072)

0.18 μm CMOS工艺的GPS/BDS双模可重构接收机射频前端*

江金光1,唐亚男1,周细凤2,刘江华2

(1.武汉大学 卫星导航定位技术研究中心, 湖北 武汉430079; 2.武汉大学 物理科学与技术学院, 湖北 武汉430072)

摘要:采用低中频架构设计了一种0.18μm CMOS工艺的GPS/BDS双模可重构接收机射频前端,能在GPS L1模式或BDS B1模式下工作。通过频率自适应电路调整中频滤波器的时间常数,降低其频率不确定度;压控振荡器中加入4位开关电容阵列,以提高频率调谐范围和相位噪声性能;通过硬件复用的方式降低系统功耗。测试结果表明,在1.8 V电源电压下,功耗37.8 mW,电压增益为103 dB,GPS L1和BDS B1波段噪声系数均小于3.2 dB。

关键词:可重构;低中频架构;射频前端;双模;GPS/BDS

全球导航卫星系统(Global Navigation Satellite System, GNSS)主要包括美国的全球定位系统(Global Positioning System, GPS),俄罗斯的GLONASS,欧盟的伽利略和中国的北斗卫星导航系统(BeiDou navigation satellite System, BDS)。移动定位服务的快速发展对GNSS接收机提出了新的要求[1-3],比如更小的体积、更低的功耗和更高的灵敏度。随着集成电路朝着系统芯片方向发展,以及CMOS工艺尺寸不断缩小,许多单模、单波段GNSS接收机已经集成在系统芯片上[4-8]。多模、多波段GNSS接收机较单模接收机在可用性、连续性和完好性方面具有优势,更加适合现代导航定位服务的需求,但会增加电路的复杂度、芯片面积和功耗。同时,为了适应复杂的电磁环境,要求GNSS接收机具有极强的抗干扰能力。因此,具有高集成度、低成本、低功耗和高灵敏度等特点的多模、多波段GNSS接收机成为研究热点[8-12]。

本文设计了一种单片、双模可重构的GPS/BDS接收机射频前端。采用电流源负载的增益可调低噪声放大器(Low-Noise Amplifier,LNA)兼顾高增益和低噪声系数的要求。出于对功耗、稳定性和闪烁噪声性能的考虑,混频器和镜像抑制滤波器都采用无源结构。一个带宽可调节的四阶有源带通滤波器(Band-Pass Filter,BPF)用于滤除干扰和通道选择。通过一个高精度的自适应电路补偿工艺和温度偏差,调节BPF的中心频率和带宽。采用两个可变增益放大器(Variable-Gain Amplifier, VGA),分别用于缓冲输入信号强度变化所产生的输出电压幅度变化和将信号幅度转换到后级数模转换器(Analog to Digital Converter, ADC)能接受的范围内。

1系统结构与信号频谱特性分析

GNSS接收机射频前端是指从接收机的天线端,经LNA、混频器、中频滤波器、VGA,直至ADC之间的电路模块,这一过程实现对信号的放大、下变频、信道选择和滤波,最后转换为数字信号。

1.1射频前端结构

射频前端分为超外差结构、零中频结构和低中频结构三种。超外差结构接收灵敏度高,但电路复杂、难以集成且功耗大;零中频结构集成度高、功耗低,但结构复杂,闪烁噪声大。所设计的带有镜像抑制功能的低中频结构射频前端如图1所示,包括LNA、I/Q两路下变频电路、镜像抑制电路、缓冲器、VGA、带通滤波器及其自适应电路和2位ADC。低中频结构中滤波器元件更容易单片集成,从而减少系统元件总数、降低功耗,且不存在直流偏置问题,闪烁噪声小。

图1 双模可重构射频前端结构Fig.1 Dual-mode reconfigurable radio frequencyreceiver architecture

1.2GPS与BDS信号频谱特性

GPS使用的频率资源有L1,L2和L5波段,BDS使用的频率资源有B1,B2和B3波段。选用GPS L1波段和BDS B1波段,其中GPS L1波段占用以1575.42 MHz为中心的2.046 MHz宽频率范围,BDS B1波段占用以1561.098 MHz为中心的4.092 MHz宽频率范围。

中频(Intermediate Frequency,IF)的选择对接收机的性能和设计有重要的影响:如果IF较高,对镜像抑制滤波器的要求会降低,但是频带选择滤波器难以抑制有用信号附近的干扰;如果IF较低,镜像抑制滤波器的设计难度加大,对频带选择滤波器的设计要求降低。考虑到GPS、BDS信号的带宽与IF的折中,中频选在4.092 MHz。

2详细电路设计

2.1增益可调低噪声放大器

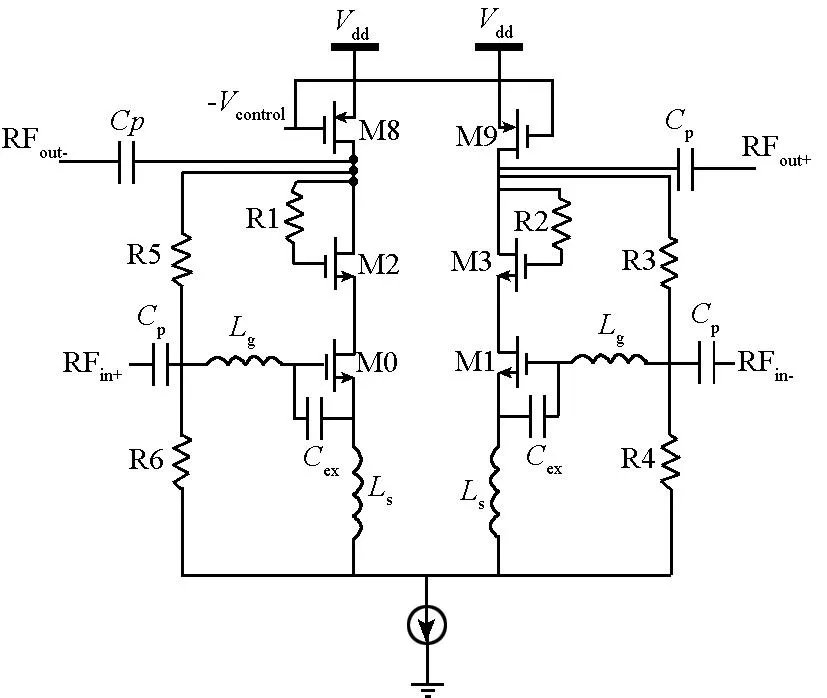

天线接收到的卫星信号十分微弱,因而对接收机噪声系数有严格的要求,其中LNA对整个接收机的噪声系数起决定作用。采用电流源负载的增益可调LNA,其电路结构如图2所示。

M8和M9是PMOS电流源负载,与LC负载的LNA相比,电流源负载的LNA具有增益高、面积小的优势。该电路跨导级由共源共栅MOS管M0~M3构成,它们的栅偏压采用自偏置方式。电阻R3~R6构成的自偏置结构使LNA的工作电流可以由PMOS电流源的偏置电压Vcontrol决定。

图2 增益可调LNAFig.2 Variable-gain LNA

Vcontrol由图3所示的偏置电路产生。

图3 LNA偏置电路Fig.3 Bias circuit of LNA

因为Mb2的宽长比很大,故Mb2的栅源电压约等于其阈值电压。流入Mb1和Mb3的电流I1,3如式(1)所示。

(1)

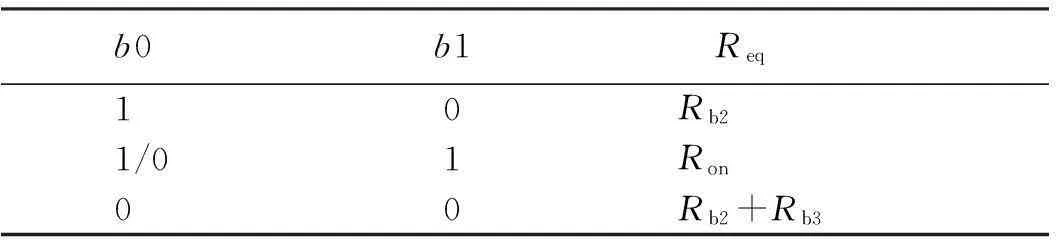

式中,VTH2是Mb2的阈值电压,Req是Mb1源端的等效电阻。I1,3决定了Mb3的栅电压,故Vcontrol由Req决定。根据b0和b1的不同组合,Req有三个不同的取值,表1列出了控制信号b0,b1和相应Req的关系,其中Ron是Mb5的导通电阻。b0和b1组合能得到三个不同的控制电压Vcontrol,因而LNA增益有三个不同取值。

表1 Req与控制信号关系

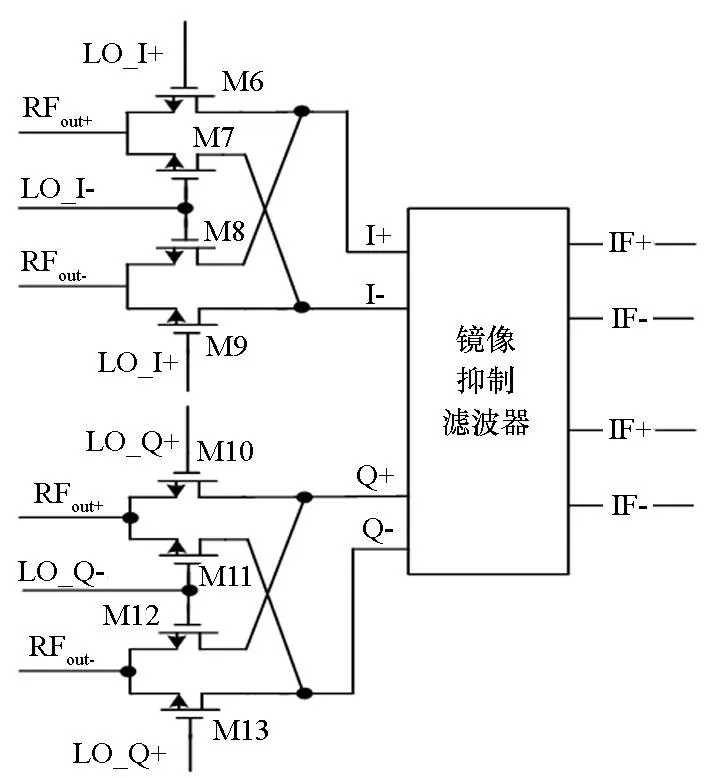

2.2混频器与镜像抑制滤波器

低中频架构射频前端要求混频器有正交解调功能来抑制中频的镜像信号,所以要用两个混频器产生两路正交相位的中频信号输出。出于低功耗考虑,采用无源双平衡混频器,其电路结构如图4所示。混频器的正交解调功能由两路相位正交的I/Q本振信号与射频信号混频实现。以I路输入为例,输入电压信号直接加到混频开关管M6~M9的源极,输出信号从开关的漏极取出。无源混频器的性能与本振信号幅度有较大相关性,电路中本振信号在进入混频器前通过一级反相器缓冲放大。通过对MOS开关的尺寸合理选取和对栅偏置电压的仿真优化,可使该电路的转化增益最优。混频器的两路输出信号I/Q通过镜像抑制滤波器消除镜像信号。

图4 混频器Fig.4 Schematic of the mixer

2.3频率综合器

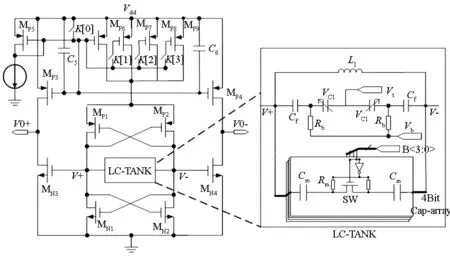

所采用的锁相环(Phase Locked Loop,PLL)频率综合器能产生两种频率的本振信号,两个参考频率由片外温度补偿晶体振荡器提供,分别是16.386 MHz和16.218 812 5 MHz。该PLL中使用的压控振荡器(Voltage Controlled Oscillator, VCO)电路结构如图5(a)所示,包含负阻电路、LC-TANK、电流偏置电路和缓冲电路四个部分。负阻电路由两对交叉耦合的MOS管组成,偏置电路采用低1/f噪声的PMOS管电流镜MP6~MP9,通过4位开关K[3:0]控制VCO核的电流大小,从而控制VCO输出电压幅度。在待机时通过K0关闭VCO,以减小功耗。LC-TANK的详细结构如图5(b)所示,包括串联对称电感L1、可变电容(包含可变电容VC1和Cf)、4位开关电容阵列C1~C4。通过调整4位开关电容阵列进行频率粗调节,使VCO的输出频率在一定范围内变化;通过加在可变电容上的控制电压的变化,对VCO的输出频率进行精确连续调整,最终达到锁定。

(a) VCO电路结构 (b) LC谐振电路(a) Circuit of VCO (b) LC-TANK图5压控振荡器Fig.5 Voltage controlled oscillator

2.4中频滤波器及其频率自适应电路

L1波段的带宽为2 MHz,B1波段的带宽4 MHz,因此可以采用一个带宽可调节的中频滤波器以便简化结构和降低功耗。为了在低频时候能够有很好的线性度和较大的动态范围,本文使用如图6所示的四阶Chebyshev有源带通滤波器。此电路由两个相同的二阶带通滤波器级联而成,其中二阶有源带通滤波器的传输函数为:

(2)

为了得到带通传递函数,需要满足:

(3)

令C1=C2,R1=R2,R3=R4,有:

(4)

(5)

由式(5)可见,通过调节C3能够改变中频滤波器的3 dB带宽BW3 dB。

图6 四阶带通滤波器Fig.6 Block diagram of the 4th-order band-pass filter

中频滤波器通过如图7所示的高精度、低失真片上滤波器频率自适应电路补偿工艺和温度的偏差,该电路采用主从调节方式,以离散的开关电容阵列作为可调元件。调节电路和信号处理电路相互独立,不会在信号通路中引入额外的噪声,而且具有较好的线性度和精度。

图7 频率自适应电路Fig.7 Architecture of auto-tuning circuit

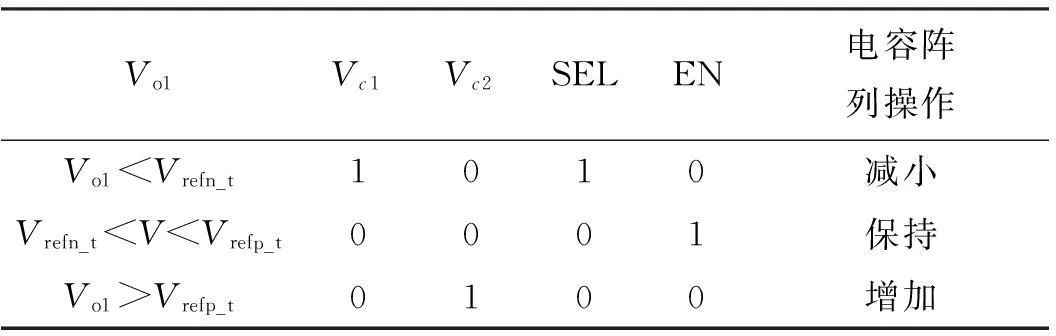

表2描述了积分器输出电压Vo1和二进制计数器操作模式之间的关系。

表2 Vo1与计数器模式关系

3测试结果

该射频前端芯片在TSMC 0.18 μm CMOS工艺下进行了流片验证,芯片面积为4.74 mm2。

输入S11参数测试结果如图8所示,在L1波段和B1波段分别为-17.968 dB和-15.326 dB。

图8 LNA S11参数测试结果Fig.8 Measured input S11of LNA

如图9和图10所示,在1 MHz频偏处L1波段和B1波段的相位噪声分别为-119.209 dBc/Hz和-117.719 dBc/Hz。

图9 输出端L1波段频谱和相位噪声测试结果Fig.9 Measured output spectrum andphase noise for L1 band

图10 噪声系数测试结果Fig.10 Measured noise figure

从图11可以看出,噪声系数小于3.2 dB @4 MHz。

GPS/BDS双模接收机射频前端的测量结果见表3,本表还列出与其他类似文献的性能比较。

图11 输出端B1波段频谱和相位噪声测试结果Fig.11 Measured output spectrum andphase noise for B1 band

参数本文文献[13]文献[14]文献[15]工艺0.18μmCMOS65nmCMOS0.18μmCMOS0.18μmCMOS架构Low-IFIF=4.092MHzDoubleIFIF=4.092/8.566MHzLow-IFIF=4.092MHzLow-IFIF=4MHz波段L1,B1L1,E1L1,E1L1噪声系数/dB3.21.8@L1,2.5@E14.54.8最大电压增益/dB103119@L1,111@E110892S11/dB-17.968dB@L1-15.326dB@B1-18—<-12本振相位噪声/(dBc/Hz@1Moffset)-119.209@L1-117.719@B1-108-126-112芯片面积/mm24.744.655.22.3电流/mA21282317电压/V1.81.21.81.6

4结论

采用0.18 μm CMOS工艺设计了一种GPS/BDS双模可重构接收机射频前端,测试结果表明,在1.8 V供电情况下,电流为21 mA,功耗为37.8 mW。L1/B1波段的噪声系数为3.2 dB,镜频抑制为19.65 dB。1 MHz频偏处本振相位噪声为-119.209 dBc/Hz@L1和-117.719 dBc/Hz@B1。

与已有研究相比,该前端设计对相位噪声、噪声系数、功耗等指标进行了折中和优化,混频器、中频滤波器等关键模块可重构,硬件复用的同时减少了芯片面积、降低了系统功耗,有较高的应用价值。

参考文献(References)[1]Tan C G, Song F, Choke T Y, et al. A universal GNSS SoC with a 0.25mm2radio in 40nm CMOS[C]//Proceedings of IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013: 334-335.

[2]Curran J T, Borio D, Lachapelle G, et al. Reducing front-end bandwidth may improve digital GNSS receiver performance[J].IEEE Transactions on Signal Processing, 2010, 58(4): 2399-2404.

[3]Chen D P, Pan W J, Jiang P C, et al.Reconfigurable dual-channel multiband RF receiver for GPS/Galileo/BD-2 Systems[J].IEEE Transactions on Microwave Theory and Techniques, 2012, 60(11): 3491-3501.

[4]Charlon O,Clamagirand S,Vathulya V,et al. A dual-mode zero-IF receiver for dual-band CDMA cellular and GPS[C]//Proceedings of 33rd European Solid State Circuits Conference, 2007: 432-435.

[5]Garmatyuk D, Morton Y, Mao X L.Radar and GPS system inter-operability with UWB-OFDM signals[J].IEEE Transactions on Aerospace and Electronic Systems, 2011, 47(1): 265-274.

[6]Wang M Y, Sheen R R B, Chen O T C, et al. A dual-band RF front-end for WCDMA and GPS applications[C]//Proceedings of IEEE International Symposium on Circuits and Systems(ISCAS), 2002, 4: 113-116.

[7]Spiegel S J, Kovacs I I G.An efficient integration of GPS and WCDMA radio front-ends[J].IEEE Transactions on Microwave Theory and Techniques, 2004, 52(4): 1125-1131.[8]Xu Y, Wang K, Pals T, et al. A low-IF CMOS simultaneous GPS receiver integrated in a multimode transceiver[C]//Proceedings of IEEE Custom Integrated Circuits Conference (CICC), 2007: 107-110.

[9]Bakkaloglu B,Fontaine P,Mohieldin A N, et al.A 1.5V multi-mode quad-band RF receiver for GSM/EDGE/CDMA2K in 90nm digital CMOS process[J].IEEE Journal of Solid-State Circuits, 2006, 41(5): 1149-1159.

[10]Yeh C H, Hsieh H C, Xu P, et al.Multi-band, multi-mode, low-power CMOS receiver front-end for sub-GHz ISM/SRD band with narrow channel spacing[C]//Proceedings of IEEE Custom Integrated Circuits Conference (CICC), 2012: 1-4.

[11]Hadjichristos A, Cassia M, Kim H,et al. Single-chip RF CMOS UMTS/EGSM transceiver with integrated receive diversity and GPS[C]//Proceedings of IEEE International Solid-State Circuits Conference-Digest of Technical Papers (ISSCC), 2009: 118-119.

[12]Xie H L,Oliaei O,Rakers P,et al.Single-chip multiband EGPRS and SAW-less LTE WCDMA CMOS receiver with diversity[J]. IEEE Transactions on Microwave Theory and Techniques, 2012, 60(5): 1390-1396.

[13]Rivela G, Scavini P, Grasso D, et al.A low power RF front-end for L1/E1 GPS/Galileo and GLONASS signals in CMOS 65nm technology[C]//Proceedings of International Conference on Localization and GNSS (ICL-GNSS), 2011: 7-12.

[14]Jo J G, Lee J H, Park D J, et al. An L1-band dual-mode RF receiver for GPS and Galileo in 0.18 μm CMOS[J].IEEE Transactions on Microwave Theory and Techniques, 2009, 57(4): 919-927.

[15]Gramegna G, Mattos P G, Losi M, et al.A 56mW 23mm2single-chip 180 nm CMOS GPS receiver with 27.2 mW 4.1mm2radio[J]. IEEE Journal of Solid-State Circuits, 2006, 41(3): 540-551.

A dual-mode reconfigurable GPS/BDS radio frequency front-end receiver in 0.18 μm CMOS process

JIANG Jinguang1, TANG Yanan1, ZHOU Xifeng2, LIU Jianghua2

(1. GNSS Research Center, Wuhan University, Wuhan 430079, China;2. School of Physics and Technology, Wuhan University, Wuhan 430072, China)

Abstract:A dual-mode reconfigurable GPS L1/BDS B1 radio frequency front-end adopting low intermediate frequency architecture was realized in 0.18μm CMOS process. An auto-calibrating circuit was used to adjust the intermediate frequency filter′s time constant and to reduce frequency uncertainty. A 4-bits capacitors array was designed to widen the frequency tuning range of the voltage controlled oscillator and to improve phase noise performance. The system power consumption was reduced by hardware reuse technique. Test results show that the power consumption is 37.8mW with 1.8V voltage supply, and the voltage gain is 103dB, while the noise figures are less than 3.2dB in both GPS L1 and BDS B1.

Key words:reconfigurable; low intermediate frequency architecture; radio frequency front-end; dual-mode; GPS/BDS

doi:10.11887/j.cn.201603004

收稿日期:2016-02-07

基金项目:国家自然科学基金资助项目(41274047);广东省科技计划资助项目(2013B090500049)

作者简介:江金光(1968—),男,湖南株洲人,教授,博士,博士生导师,E-mail:jgjiang09@aliyun.com

中图分类号:TN432

文献标志码:A

文章编号:1001-2486(2016)03-019-06

http://journal.nudt.edu.cn