高性能25~30 GHz 6位单片数控衰减器

张 博, 赵 晶, 张 晗, 李金蕾

(西安邮电大学 电子工程学院,陕西 西安 710121)

高性能25~30 GHz 6位单片数控衰减器

张博, 赵晶, 张晗, 李金蕾

(西安邮电大学 电子工程学院,陕西 西安 710121)

摘要:采用0.15 μm 砷化镓赝配高电子迁移率晶体管工艺,设计一款高性能25~30 GHz 6位单片数控衰减器芯片。电路采用6个基本衰减单元级联结构,通过控制不同衰减位导通状态组合形成64个衰减状态,给出在衰减电阻上并联的衰减结构。仿真结果表明,所设计的数控衰减器具有0.5 dB的衰减步进和31.5 dB的最大衰减范围;插入损耗小于5.7 dB,回波损耗优于-10 dB;所有状态衰减精度小于+0.5 dB,附加相移小于-6.0°,衰减幅度均方根误差小于0.21 dB,芯片尺寸为2.0 mm×1.0 mm,可提高衰减精度。

关键词:数字衰减器;高精度;砷化镓;赝配高电子迁移率晶体管

微波单片集成电路(MicrowaveMonolithicIntegratedCircuit,MMIC)数字衰减器[1]主要用于控制电路传输功率增益的设定和控制,已被广泛应用在相控阵雷达、移动通信系统及智能扫描天线中。数字衰减器是组成相控阵雷达的收发组件[2-3](T/R组件)中的核心部件,它的性能好坏直接影响到整个相控阵雷达的工作性能。将单片微波技术和衰减器相结合,高性能、超宽带、稳定性好的小型化MMIC数字衰减器成为了微波技术领域的研究热点和发展方向。

数字衰减器作为相控阵收发的关键部件,对衰减器的性能有很高的要求。低插入损耗衰减器[4-5]在参考状态下损耗较小,可以减小系统中能量损耗和对通道固有增益的影响;低插入相移衰减器[6-7]传输相移恒定,能够为系统省去幅度校准和相位校准所需要的复杂额外电路,降低了系统成本,提高了电路可靠性;高线性度衰减器[8]对信号的非线性度误差较小,保证电路工作在线性区,抑制信号干扰从而保证信号正常传输。上述设计中均忽略了衰减精度这一指标,准确的衰减值是数字衰减器最为重要的性能指标。

本文拟采用0.15μm砷化镓赝配高电子迁移率晶体管工艺(GaAsPHEMT),并基于ADS设计平台,采用GaAsPHEMT开关电路模型,给出一种提高衰减精度的并联电容衰减结构。

1数字衰减器基本理论

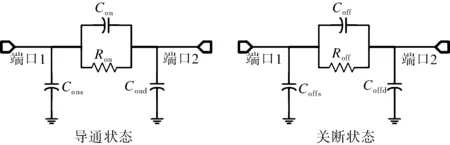

1.1GaAs PHEMT 开关电路模型

有源和无源器件的建模是单片集成电路设计的基础,尤其是有源器件的电特性机理和模型特点,对单片集成电路设计十分重要。在数字衰减器中,PHEMT管芯作为开关控制器件,通过栅极电压控制源极和漏极间的阻抗变换,实现开关的导通与关断。源级和漏极分别是输入和输出端。开关PHEMT的栅宽不同,其电路模型参数也不同。根据电性能优化的需求确定最佳栅宽,不同栅宽模型参数的比例缩放系数是实现电路性能优化的前提之一。图1为PHEMT管芯等效电路模型。

图1 PHEMT管芯等效电路模型

根据PHEMT管芯结构可得到各元件值与栅宽的关系[9]为

Ron=ron/WCon=con×WCons=Cond=cons×W

Roff=roff/WCoff=coff×WCoffs=Coffd=coffs×W

当PHEMT管芯具有源漏对称结构时,有

Cons=CondCoffs=Coffd

ron、roff、con、coff分别表示栅极导通态和关断态下本征电阻比例缩放参数和本征电容比例缩放参数,Ron和Roff分别表示栅极导通态和关断态下的本征电阻,Con和Coff分别表示栅极导通态和关断态下的本征电容,cons、coffs、cond、coffd分别表示管芯源级和漏极导通态和关断态下电容比例缩放参数,W表示栅宽。

1.2衰减器电路拓扑结构

数字衰减器常用的电路拓扑结构为T型和π型衰减器。对于固定衰减值,选择合适的拓扑结构,通过改变电路中电阻阻值实现衰减。图2是衰减器拓扑结构。

T型衰减结构简单,芯片占用面积小,是一种适用于小衰减值衰减结构,但T型结构两端的回波损耗偏大,很难达到匹配,对级联影响较大。相比较T型结构,π型结构两端的回波损耗优良,可以提供很大的衰减量,同时可以实现带内最大的平坦度。但π型结构的插入损耗和附加相移偏大[10-12]。

(a) T型衰减器拓扑结构

(b) π型衰减器拓扑结构

1.36位衰减器工作原理

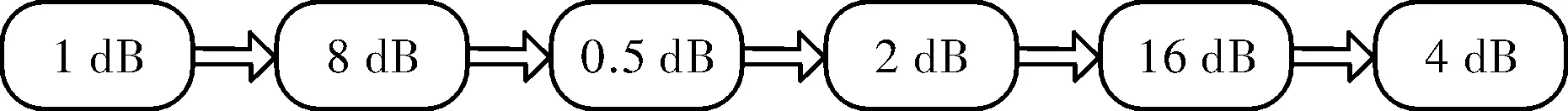

6位数字衰减器由6个基本衰减位0.5dB、1dB、2dB、4dB、8dB、16dB通过级联够成整体电路。利用数字编程控制开关PHEMT的栅极电压来实现对开关导通和关断的切换,从而控制单个衰减器的导通和截止,组合形成不同的衰减状态,输出不同的衰减量。

对每一个衰减位的设计,高精度的衰减量和良好的端口驻波性直接决定了整体电路的性能。将6个基本衰减位依据驻波特性交叉排列,减小因为相邻两个衰减位驻波不理想造成的衰减精度、回波损耗和附加相移等性能的相互影响。图3为六位数字衰减器的结构框图。

图36位数字衰减器的结构

2电路芯片设计与优化

基于ADS软件设计平台,采用MOMENTUM联合仿真优化法,对6个基本衰减单元进行设计优化,电路设计和优化中采用性能冗余优化策略[13],以保证较高的成品率。

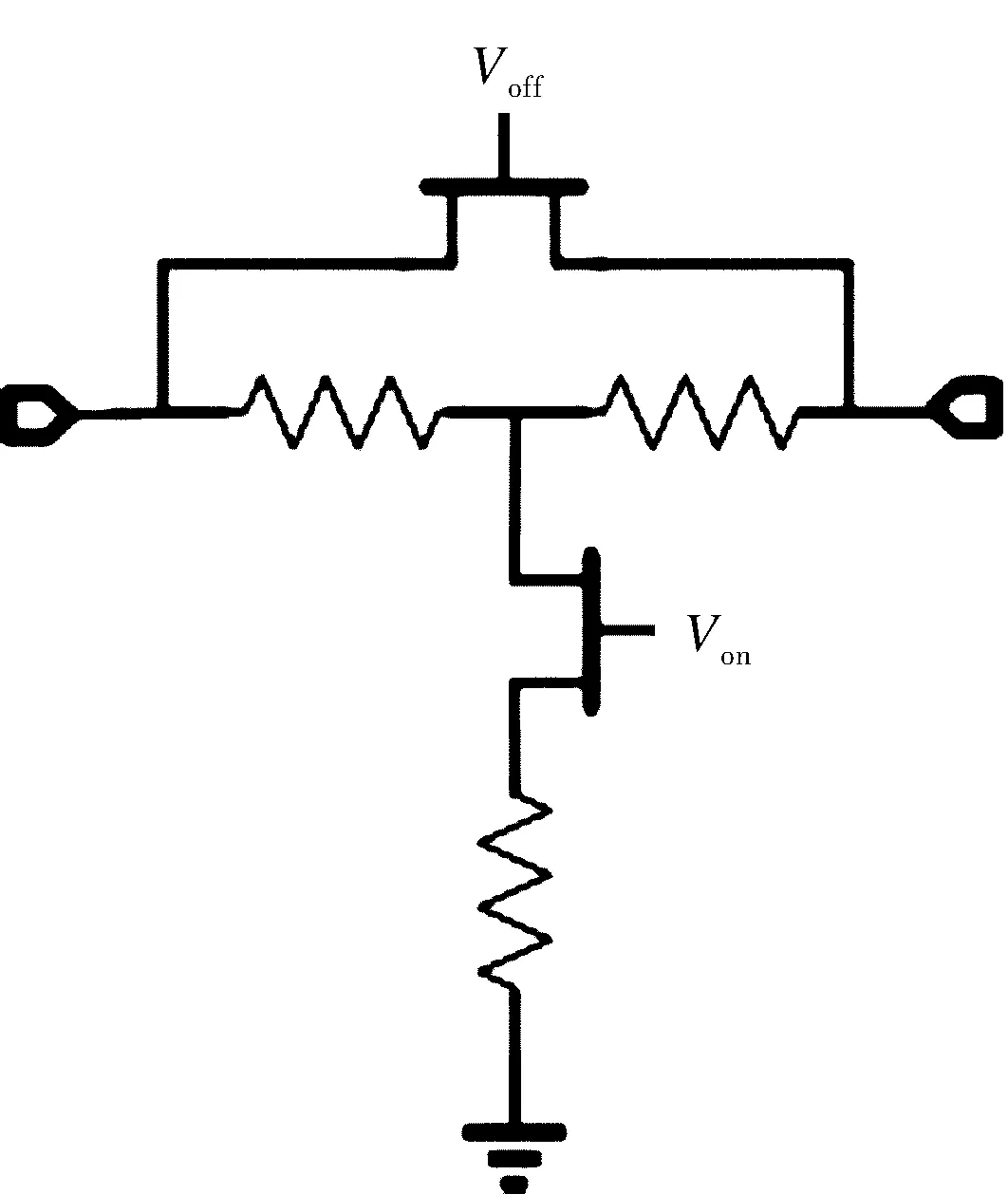

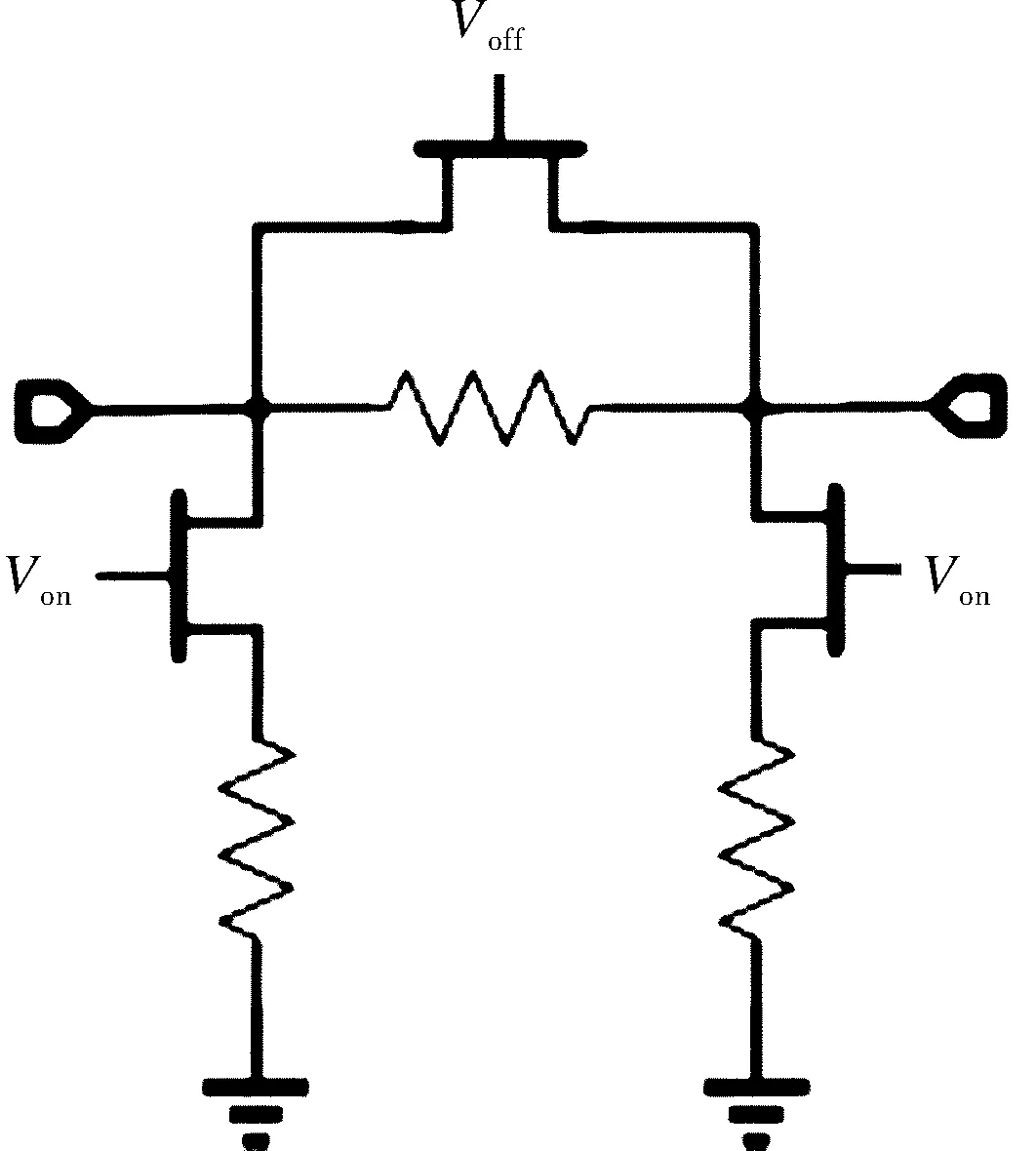

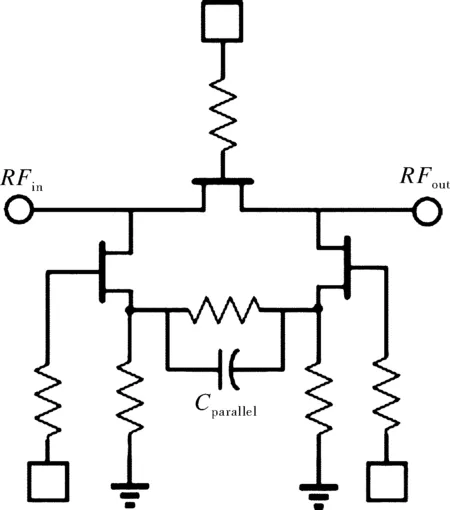

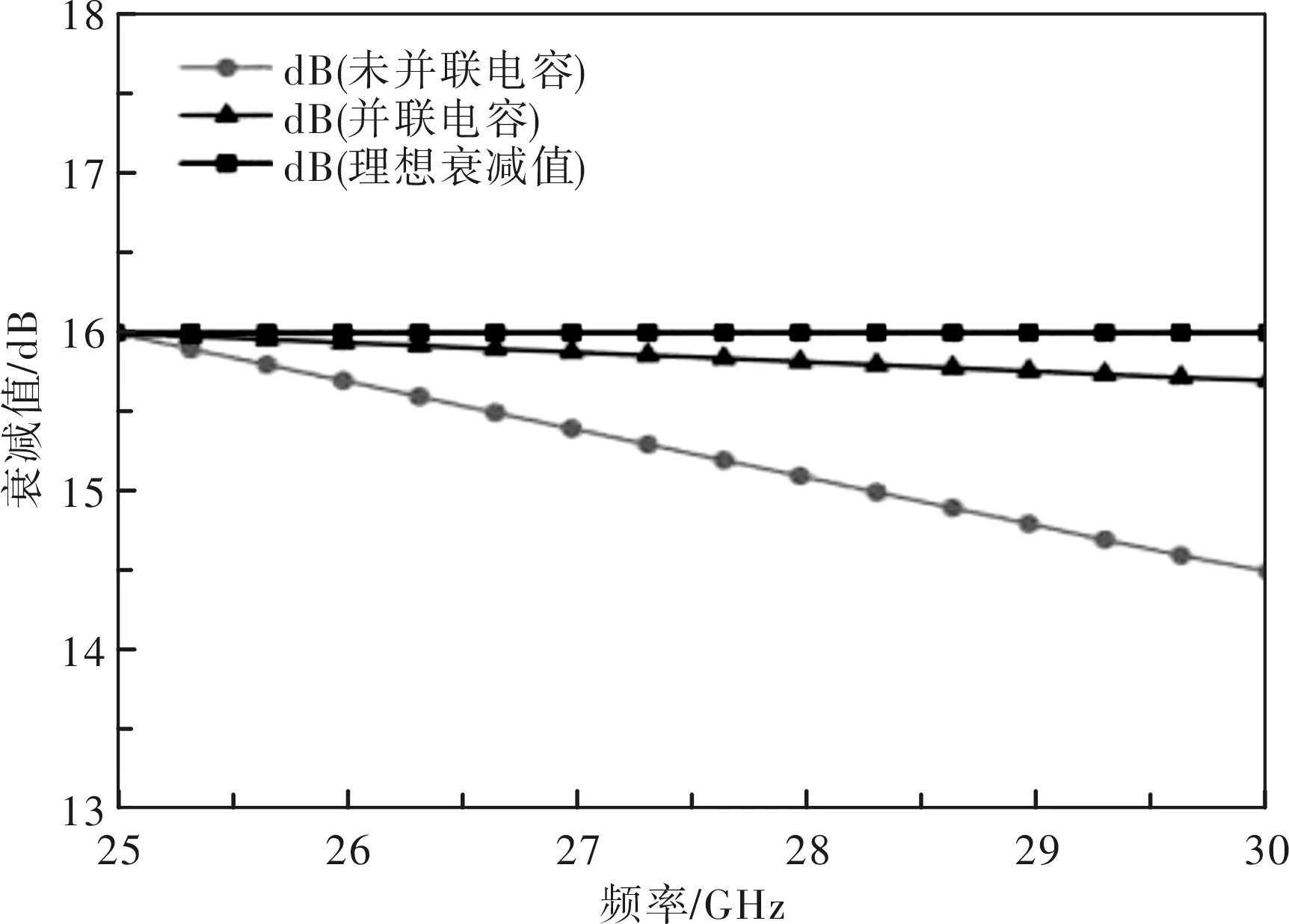

对于0.5dB和1dB小衰减位的设计,传输线对通过信号的衰减与电阻衰减相近,可以用传输线代替电阻,采用简化的T型衰减网络,获得较小的插入损耗和芯片面积。对于2dB和4dB中等衰减位的设计,采用T型拓扑结构。对于8dB衰减位来说,PHEMT的寄生电容和与分流相关的电感限制了高频部分的衰减平坦度,随着频率的升高,衰减量会下降。采用π型拓扑结构,实现较大的衰减量和带内最大平坦度。对于16dB衰减位来说,为了满足衰减精度和芯片面积的要求,同样选用π型拓扑结构。相比较8dB衰减位,16dB衰减位的寄生电容和分流电感对衰减平坦度的影响也更加明显。因此,提出一种并联电容的结构将高频部分衰减量拉高,实现带内的平坦,从而提高衰减精度,如图4所示。图5为并联电容对衰减量的影响。

图4 改进的并联电容衰减结构

图5 并联电容对衰减量的影响

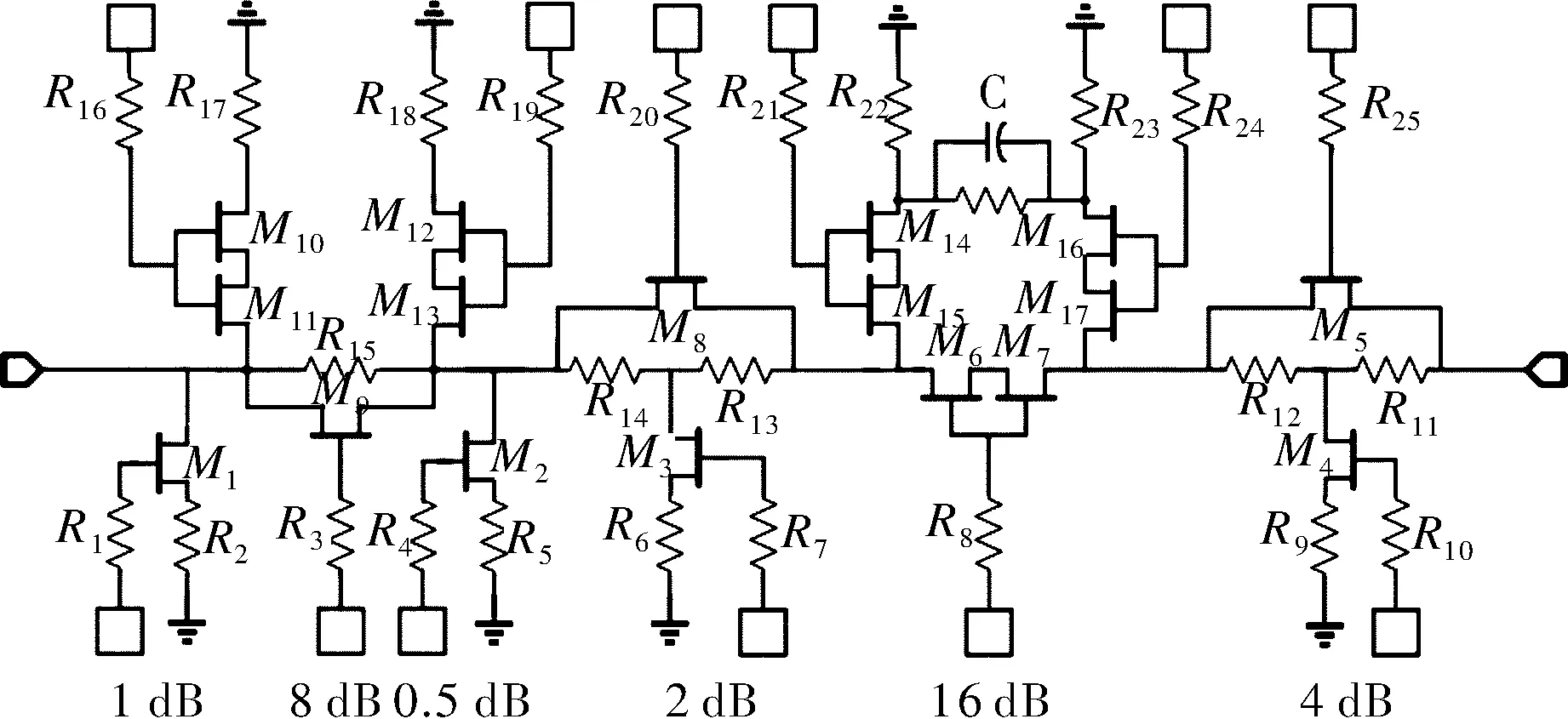

为了提高宽带范围内的隔离度,采用两个PHEMT串联结构。图6为6位数字衰减器的原理图。

图6 6位数字衰减器原理

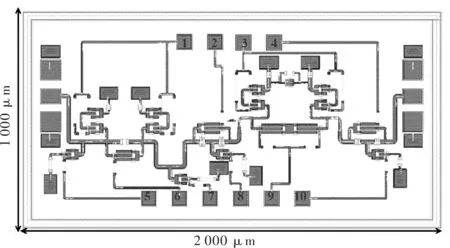

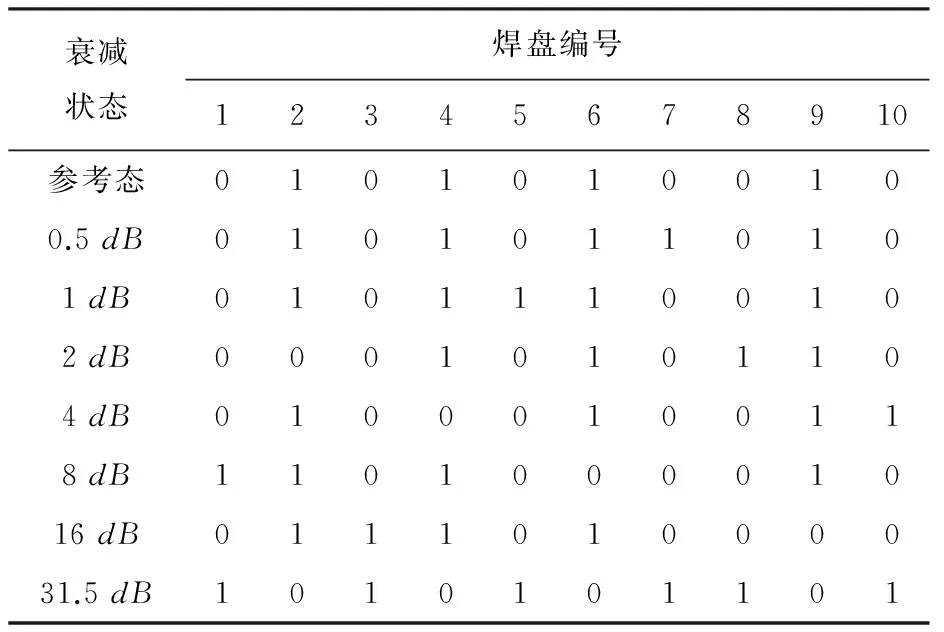

在电路版图设计过程中,为了减小芯片尺寸,降低芯片生产制造成本,应在满足设计规则的前提下,对版图进行合理布局,避免高密度布局布线引起元件间的耦合。图7为6位衰减器版图。芯片中共有10个电压控制端焊盘,当控制端电压为0.5V,PHEMT导通,控制端电压为-2V,PHEMT截止。通过控制端电压的不同组合(见真值表1)实现64个衰减状态。

图7 6位数字衰减器版图设计

衰减状态焊盘编号12345678910参考态01010100100.5dB01010110101dB01011100102dB00010101104dB01000100118dB110100001016dB011101000031.5dB1010101101

3电路电磁仿真结果

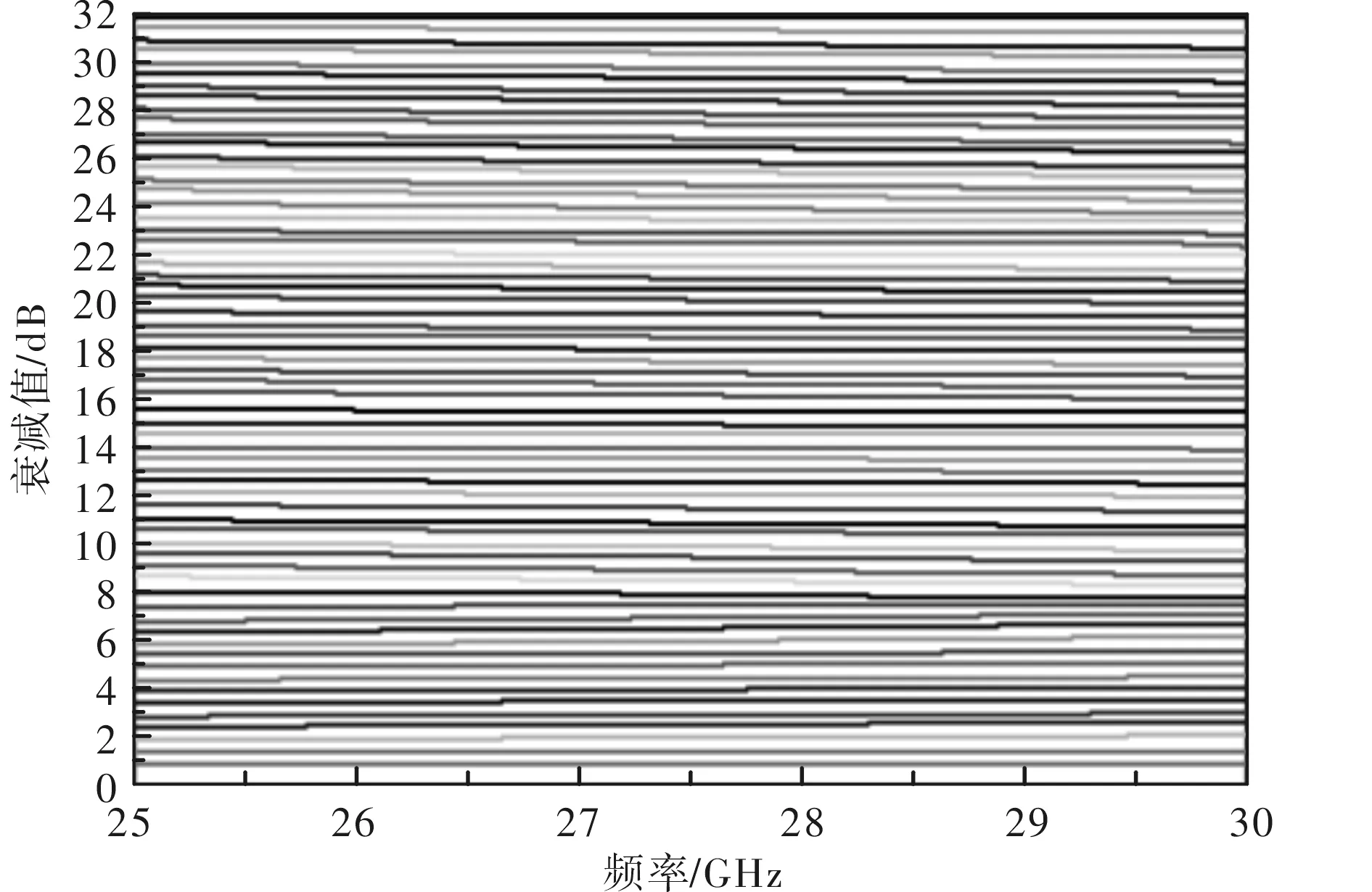

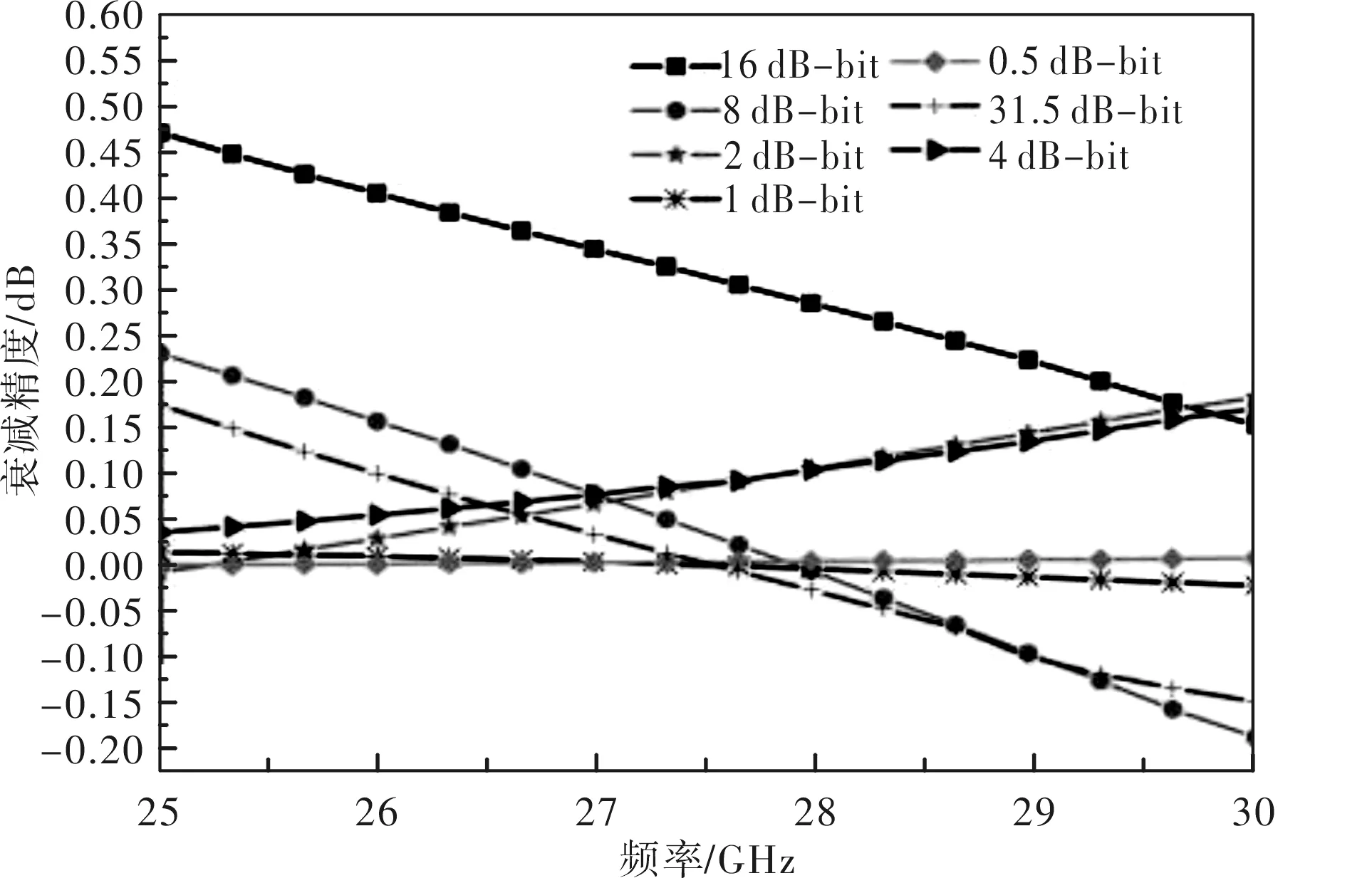

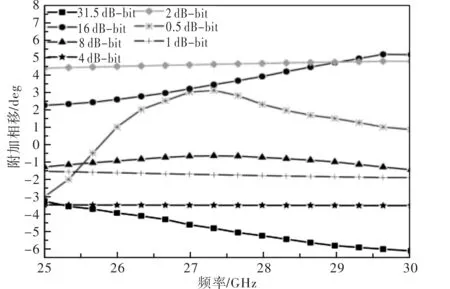

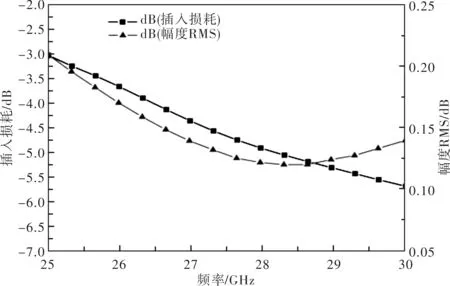

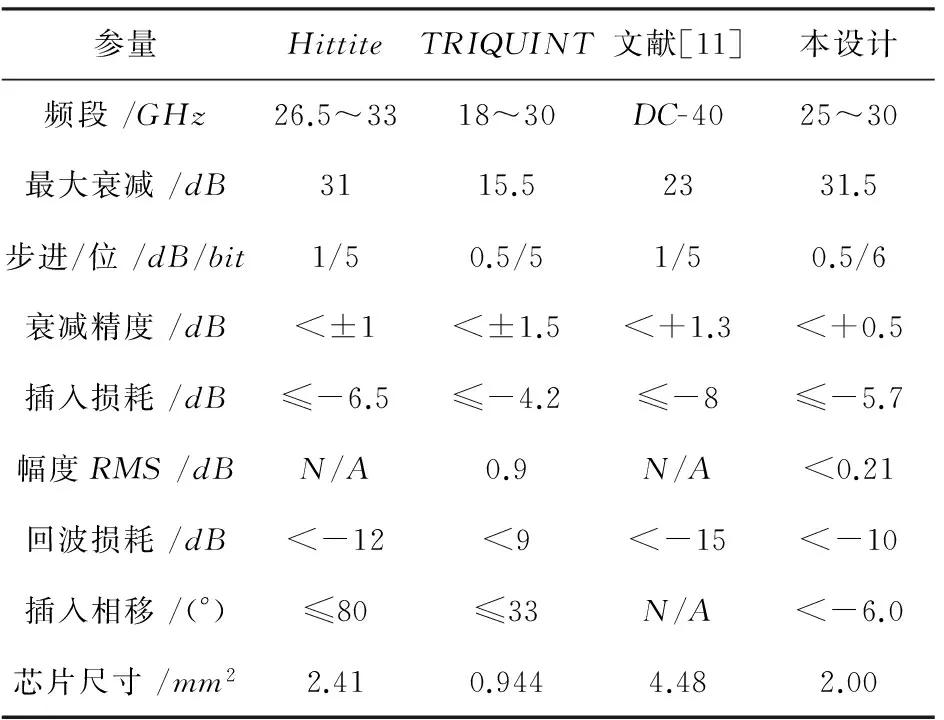

采用0.15μmGaAsPHEMT圆片工艺线制作25~30GHz6位单片数字衰减器芯片。电磁(Electromagneticsimulation,EM)仿真结果如图8所示。表2为所设计的衰减器与Hittite、TRIQUINT同类商用芯片以及文献[11]中所设计的衰减器性能比较。

(a) 64个衰减状态衰减特性

(b) 主要衰减状态衰减精度

(c) 主要衰减状态附加相移

(d) 插入损耗和幅度RMS

参量HittiteTRIQUINT文献[11]本设计频段/GHz26.5~3318~30DC-4025~30最大衰减/dB3115.52331.5步进/位/dB/bit1/50.5/51/50.5/6衰减精度/dB<±1<±1.5<+1.3<+0.5插入损耗/dB≤-6.5≤-4.2≤-8≤-5.7幅度RMS/dBN/A0.9N/A<0.21回波损耗/dB<-12<9<-15<-10插入相移/(°)≤80≤33N/A<-6.0芯片尺寸/mm22.410.9444.482.00

与同类衰减器性能指标比较表明,所设计的数字衰减器衰减精度高,插入损耗、插入相移[14-17]相对较低,且芯片面积较小。

4结束语

设计了一款25~30GHz6位单片数字衰减器芯片,采用0.15μmPHEMT圆片工艺进行芯片的设计和流片。芯片衰减步进为0.5dB,具有31.5dB最大衰减范围,插入损耗小于5.7dB,回波损耗优于-10dB;所有状态衰减精度小于+0.5dB,附加相移为小于-6.0°,衰减幅度均方根误差小于0.21dB,芯片尺寸为2.0mm×1.0mm。结果表明,给出的衰减结构提高了衰减精度,该芯片衰减精度高,且插入损耗和附加相移相对较低,芯片面积小。

参考文献

[1]ROBERTSONI,LUCYSZYNS.单片微波射频集成电路技术与设计[M].文广俊,谢甫珍,李家胤,译.北京:电子工业出版社,2007:268-269.

[2]阴亚芳, 张虹, 张博,等. 基于GaAs电感模型的微波功率放大器[J]. 西安邮电大学学报, 2014,15(2):94-97.DOI:10.13682/j.issn.2095-6533.2014.02.018.

[3]巩稼民, 李欢, 张博,等. 40Gb/s光通信系统驱动放大器设计[J]. 西安邮电大学学报, 2014, 15(4):85-89.DOI:10.13682/j.issn.2095-6533.2014.04.017.

[4]张岩龙, 庄奕琪, 李振荣,等. 一种5~20GHz低插损低相位误差的CMOS衰减器[J]. 西安电子科技大学学报(自然科学版), 2015(2):89-94.DOI:10.3969/j.issn.1001-2400.2015.02.015.

[5]甄建宇. 一种低插损大衰减量的MMIC6位数控衰减器[D].成都: 电子科技大学, 2014:1-60.

[6]李宇昂. 超宽带低相移5位数控衰减器的研究和设计[D]. 西安:西安电子科技大学, 2013:1-57.

[7]戴永胜, 陈曦, 陈少波,等. 微波毫米波超宽带低相移6位数字衰减器,中国 ,CN102055427A[P].2011.

[8]庄奕琪, 李振荣, 张岩龙,等. 硅基高线性度低相移超宽带数字衰减器,中国 ,CN103427781A[P].2013.

[9]戴永胜,方大纲.GaAsMMIC开关MESFET电路建模技术研究[J].南京理工大学学报,2006,30(5):612-617.

[10]ZHAOL,LIANGWF,XUXJ,etal.AnIntegratedQ-band6-bitDigitalAtteunatorwithLowInsertionLoss[C]//Asia-PacificMicrowaveConference,Sendai,Japan:IEEE,2014:1196-1198.

[11]CHENNa.AMillimeter-wave6-bitGaAsMonolithicDigitalAttenuatorwithLowInsertionPhaseShift[C]//MicrowaveandMillimeterWaveCircuitandSystemTechnology(MMWCST),Chengdu:IEEE, 2013:440-443.DOI:10.1109/MMWCST.2013.6814545.

[12]戴永胜,陈曦,陈少波,等. 6~18GHzGaAsPHEMT5位MMIC数字移相器[J].微波学报,2012,28(1):66-69.

[13]戴永胜, 李平, 孙宏途,等. 高性能2~18GHz超宽带MMIC6位数字衰减器[J]. 微波学报, 2012, 28(6):80-83.

[14]DAIYS,ZHANGJ,DAIBQ,etal.AnUltraBroadband2~18GHz6-BitPHEMTMMICDigitalAttenuatorwithLosInsertionPhaseShift[C]//Ultra-Wideband(ICUWB2010)IEEEInternationalConference.Nanjing:IEEE, 2010:1-3.DOI:10.1109/ICUWB.2010.5614714.

[15]DAIYS,LIP,HanQF,etal.ResearchonANovel2~18GHzPHEMTMMICDigitalAttenuatorwithLowInsertionPhaseShift[C]//MicrowaveandMillimeterTechnology(ICMMT),Shenzhen:IEEE,2012:1-4.DOI:10.1109/ICMMT.2012.6230309.

[16]JUI,NOHYS,YOMIB.UltraBroadbandDC-40GHz5-bitpHEMTMMICDigitalAttenuator[C]//EuropeanMicrowaveConference,European:IEEE,2012:1-4.DOI:10.1109/EUMC.2005.1610096.

[17]DODDAMANIND,HARISHCHANDRA,NANDIAV.DesignofSPDTSwitch, 6BitDigitalAttenuator, 6BitDigitalPhaseShiftforL_BandT/RModuleusing0.7μmGaAsMMICTechnology[C]//ICSCN’07.InternationalConference,Chennai:IEEE, 2007:302-307.DOI:10.1109/ICSCN.2007.350752.

[责任编辑:祝剑]

Ahighperformance25~30GHz6-bitMMICdigitalattenuator

ZHANGBo,ZHAOJing,ZHANGHan,LIJinlei

(SchoolofElectronicEngineering,Xi’anUniversityofPostsandTelecommunications,Xi’an710121,China)

Abstract:A 25~30 GHz 6-bit MMIC digital attenuator with 0.15 μm GaAs PHEMT process is proposed, which is composed of six main attenuation units. by controlling the states of different attenuation units it can get all 64 attenuation states. To enhance the attenuation accuracy, a structure using capacitor in parallel is presented as well. Simulation results show that, this digital attenuation has 0.5 dB resolution and 31.5 dB dynamic attenuation rage, the insertion loss is less than 5.7 dB while the return loss is better than -10 dB over all states and the entire frequency range, its accuracy is less than 0.5 dB while the insertion phase shift is less than -6.0°, besides, RMS attenuation error is less than 0.21 dB while the chip size is 2.0 mm×1.0 mm, so, a presented structure using capacitor in parallel can enhance the attenuation accuracy greatly.

Keywords:digital attenuator,high accuracy,GaAs,PHEMT

doi:10.13682/j.issn.2095-6533.2016.02.012

收稿日期:2015-07-02

基金项目:国家自然科学基金资助项目(61201044)

作者简介:张博(1983-),男,博士,副教授,从事射频模拟集成电路设计研究。E-mail:zhangbo@xupt.edu.cn 赵晶(1990-),女,硕士研究生,研究方向为射频集成电路设计。E-mail:760104060@qq.com

中图分类号:TN715

文献标识码:A

文章编号:2095-6533(2016)02-0063-05