基于SERDES的雷达数据高速传输的实现与应用

王平安,吴 卫,于志伟,陈文攀

(中国船舶重工集团公司第七二四研究所,南京 211153)

基于SERDES的雷达数据高速传输的实现与应用

王平安,吴卫,于志伟,陈文攀

(中国船舶重工集团公司第七二四研究所,南京 211153)

摘要:针对宽带高速数据传输需求,提出了一种利用FPGA内部SelectIO资源实现SERDES高速传输的解决方法。通过对OSERDES和ISERDES原语的使用来实现对数据的并串转换和串并转换。在实际工程应用中实现了对32个通路、每路400 Mb/s的稳定传输,验证了系统的有效性与可靠性,满足了项目需求。该设计易于移植,对于高速、多路数据传输系统的设计具有一定参考意义。

关键词:数据传输;串行器/解串器;现场可编程门阵列;高速

0引言

现代高速密集数字处理技术和计算技术的发展,使得对多通道大带宽数据进行实时处理成为可能。在相控阵体制雷达系统中,往往有几十路甚至成百上千路的实时数据。如此庞大数据的高速、实时传输对系统设计来说是一个挑战。传统的单端互联设计方式由于易受干扰、噪声的影响,传输速率最高只能达到200~250 Mb/s/Line。在更高速率的接口设计中,多采用包含有源同步时钟的差分串行传输方式[1]。高速串行技术不仅能够带来更高的性能、更低的成本和更简化的设计,克服了并行的速度瓶颈,还节省了I/O资源,使印制板的布线更简单,因此被越来越广泛地应用于各种系统设计中。

本文采用SERDES串行传输方法,对接收到的多路雷达数据在两片FPGA之间实现实时稳定传输,从而通过双FPGA并行处理的方式解决了用单片FPGA处理所有通路数据时资源不足、并行传输引脚众多、光纤互联通道数有限等问题。

1SERDES方案对比

SERDES(Serializer-Deserializer)是串行器和解串器的简称,是一种主流的时分多路复用(TDM)、点对点的串行通信技术。在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本[2]。

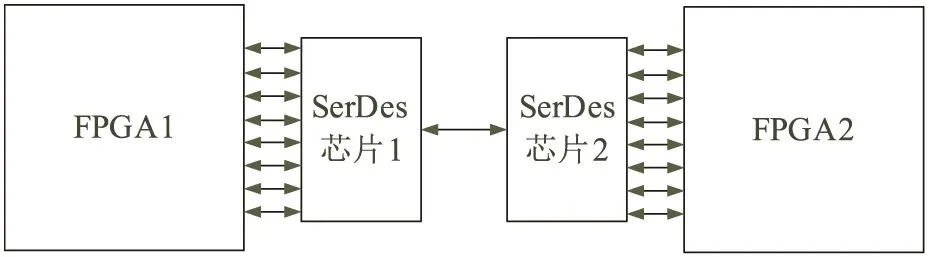

1.1采用SERDES芯片

在传统设计中多采用外置转换芯片来完成数据的并/串转换。如在发送端利用并/串转换芯片DS92LV8028完成数据的串行化,在接收端利用串/并转换芯片SCAN926260恢复出并行数据,如图1所示。但是,此方法需依赖额外的硬件资源且占用宝贵的嵌入式管脚资源[3],当通道数成倍增加时对PCB布局布线、系统功耗及成本造成影响。

图1 用SERDES芯片完成并串转换

1.2采用Rocket I/O传输

随着FPGA技术不断发展,很多类型的FPGA都内嵌有高速收发器SERDES硬核,如Xilinx公司的Virtex-6系列FPGA内置有36个Rocket I/O硬核,能够实现单通道传输速率高达11.2 Gb/s。考虑到方案的通用性与交互性,在设计FPGA板卡时只利用了部分Rocket I/O硬核,其中大部分需要被用于和其他系统进行数据及控制命令的传输,且Serial RapidIO也需要占用部分Rocket I/O链路资源。因此,当光纤传输链路无法满足所有数据链路需求时,需寻找其他方法来实现片间多路数据的高速互传。

1.3利用FPGA内部的SelectIO资源实现

在本方案设计中,利用FPGA内部SelectIO资源,通过对ISERDES和OSERDES等xilinx原语逻辑资源的使用,在发送芯片上实现数据的并串转换,在接收芯片上实现数据的串并转换,最终实现对数据的高速串行传输。采用的信号处理芯片为Xilinx Virtex-6系列FPGA,所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准[4]。

ISERDES解串器是专用的串并转换器,具有专门实现高速源同步应用的时钟控制与逻辑功能,可以实现高速数据传输。此转换器支持单倍数据速率(SDR)和双倍数据速率(DDR)两种模式。每个ISERDES最大支持1∶6的串并转换,因此构建大于1∶6的串并转换器需要用两个ISERDES。通过将主ISERDES的SHIFTOUT 端口连接到从ISERDES的SHIFTIN端口,可以将串并转换器最大扩展到1∶10(DDR)和1∶8(SDR)。

OSERDES是专用的并串转换器。每个OSERDES模块包括1个用于数据和三态控制的专用串行器。数据和三态串行器都可以配置成SDR和DDR模式。和ISERDES类似,构建大于1∶6的并串转换器需要用两个OSERDES。每个I/O模块中有一主一从两个OSERDES模块,可以将并串转换器最大扩展到10∶1(DDR)和8∶1(SDR)[5]。

2链路方案实现

本方案所涉及的目标系统中,信号处理器中的一块FPGA板卡需要接收前端DBF处理模块传过来的16路IQ数据,并对这16路IQ数据进行数字信道化及对每一信道滤波检测和脉冲参数测量处理。因信道数众多,信号处理需要占用大量资源,导致一片Virtex-6难以完成如此庞大的数据处理设计。而所用FPGA板卡上有两片Virtex-6,其间有100对IO通过LVDS电平进行互连。因此,设计使FPGA1(U1)接收到的16路数据中的8路通过SERDES传到FPGA2(U2)上进行处理,再将FPGA2的处理结果传回到FPGA1,最后再将两片FPGA的处理结果一起打包通过FPGA1发送到后端数据处理分机。FPGA1和FPGA2之间的数据传输链路如图2所示。

2.1数据的串行化与解串

FPGA1对并行数据进行并/串转换,利用两个OSERDES构成主从模式,通过将主OSERDES的SHIFTIN端口连接到从OSERDES的SHIFTOUT端口,使并串转换器扩展到8∶1进行传输,如图3所示。在接收端FPGA2上,ISERDES也构成主从模式,实现对串行数据的1∶8的解串功能。ISERDES输出并行数据的顺序和输入到OSERDES的并行数据是颠倒的(如图4所示),在传输数据时需要做数据位颠倒处理。由于1路并行I/Q数据共有32位,因此需要4对LVDS差分线进行传输。而8路I/Q数据(共256位)则需要32对LVDS差分线进行传输。设计时将其分成两组,每组传输128位,如图2所示。为实现源同步时钟设计,串行时钟通过ODDR模块在发送端进行转发,在接收端通过BUFIO和BUFR得到相位匹配的并行时钟和串行时钟。因此,每个链路组需要16对LVDS传输数据,1对LVDS传输源同步时钟,同时增加1对LVDS用于传输状态标识信号。

图2 两片FPGA间数据传输SERDES链路

SERDES发送端并行数据的处理时钟为50 MHz。这里采用DDR(Double Data Rate)双沿方式进行传输,则串行时钟为200 MHz。OSERDES的数据率为400 Mb/s(8b×50 MHz),相应的ISERDES也配置成DDR模式,其串行时钟、并行时钟分别为200 MHz和50 MHz。

图3 主/从OSERDES模式实现1路8∶1并串转换

图4 主/从ISERDES模式实现1路1∶8串并转换

2.2数据训练与对齐

为达到数据时序的动态调整,在传输真实数据之前,SERDES链路有一个训练的过程。在发送端有一个多路复用器,选择是发送真实数据还是训练序列。当接收端所有通道都对齐后,资源共享控制模块(RESOURCE_SHARING_CONTROL)产生一个TrainDone高电平有效信号送到发送端,来控制发送真实数据,否则发送训练序列。

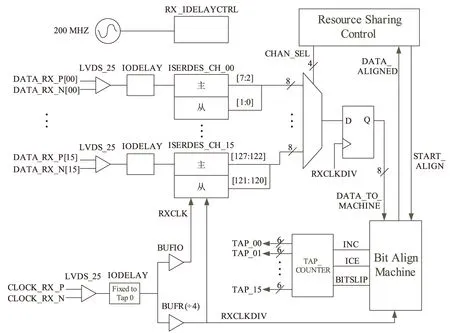

每个链路组传输16个通道的串行数据,在接收端需要对这16个通道的数据做对齐处理,其主要功能模块如图5所示。位对齐控制模块(BIT_ALIGN_MACHINE)用于分别对每个通道进行对齐,START_ALIGN信号用于通知位对齐控制模块(BIT_ALIGN_MACHINE)多路复用器的输出已经稳定,当前通道的对齐工作可以正常开始。资源共享控制模块控制多路复用器选择哪一路进行对齐,当其收到DATA_ALIGNED信号时,则说明当前通道已经完成对齐,以确保一路完成对齐后再转向下一路。此外,位对齐控制模块(BIT_ALIGN_MACHINE)产生3个控制信号来调整ISERDES的时序。INC、ICE通过IODELAY使数据通道的延时增加或减少75 ps的整数倍(当参考时钟为200 MHz时)。BITSLIP使每一个ISERDES的并行数据流重新排序,从而促进字对齐的进程。

2.3CRC校验

为保证数据传输的可靠性,达到高效检错功能,在传输数据的每帧数据中加入循环冗余校验码字段(CRC码)。在接收端用同样方法解出CRC码后与接收到的CRC码进行比较,若相同则传输过程中没有出现错误,若不相同则传输过程有错误,并送出错误标识。

2.4复位

图5 接收单元数据对齐框图

当FPGA2接收到的数据发生错误(CRC码有误)或序列未完成训练时,产生一个复位信号SendNeedRst_U2toU1。FPGA1收到该复位信号后产生一个Oserdes_RST信号对其OSERDES进行复位,同时产生一个FPGA1到FPGA2的控制信号OnLine_U1toU2。FPGA2接收到该信号后产生对接收端的复位信号Rx_Module_RST,其时序图如图6所示。图中,A区域为发送的训练序列,B区域为发送真实数据。

图6 SERDES链路复位时序图

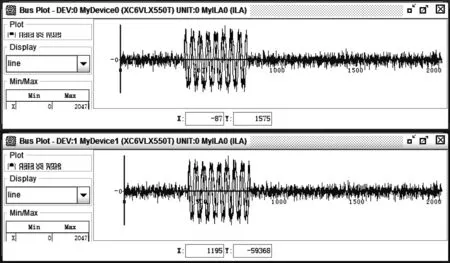

3实际传输结果

在本设计中,信号处理板卡上的FPGA1接收到16路DBF数据后,将其中的8路数据(每路32bit)通过SERDES进行并/串、串/并转换送到了FPGA2上,每路SERDES传输速率为400 Mb/s。用ChipScope抓取到的一路IQ数据传输结果如图7所示。FPGA2能够实时、稳定、无误地接收到FPGA1传过来的数据。

根据Xilinx手册,若采用-3速度等级的FPGA,则SERDES的传输速度将可以达到1.2 Gb/s,可满足绝大部分更大带宽更多通道数据传输要求。

图7 一路IQ数据传输结果

4结束语

本文主要研究了一种利用FPGA内部ISERDES和OSERDES资源,通过普通IO管脚实现了两片FPGA间的高速串行数据传输方法。该方法经实际工程试验,结果表明传输数据稳定可靠,能够很好地满足系统使用需求,解决了工程中使用单片FPGA信号处理时资源不足、光纤传输接口有限、并行传输引脚众多且受速度瓶颈影响等一系列问题。

参考文献:

[1]徐文波,田耘. Xilinx FPGA开发实用教程 [M]. 2版. 北京:清华大学出版社,2012.7:20-22.

[2]沈竞宇.基于SerDes芯片8b/10b编解码电路的设计及验证[D]. 电子科技大学硕士学位论文, 2011.

[3]张峰.自适应动态延时调整的SERDES技术在宽带数据传输中的应用[J].电讯技术,2014,54(4):468-471.

[4]李大鹏,李雯,王晓华. 基于FPGA的高速LVDS接口的实现[J].航空计算技术,2012,42(5): 115-118.

[5]Xilinx corporation. 16-Channel,DDR LVDS Interface with Per-Channel Alignment[EB/OL]. http://www.xilinx.com, 2006.

Realization and application of high-speed radar data transmission based on SERDES

WANG Ping-an, WU Wei, YU Zhi-wei, CHEN Wen-pan

(No.724 Research Institute of CSIC, Nanjing 211153)

Abstract:According to the demand of high-speed wideband data transmission, a solution to the realization of the SERDES-based high-speed transmission is proposed making use of the SelectIO resources in the FPGA. The parallel and serial data conversion is realized through the OSERDES and ISERDES primitives. In the practical engineering application, 32-channel data transmission is stable, with the speed of 400 Mb/s per channel, verifying the effectiveness and reliability of the system and satisfying the requirements of the project. The design is easy to transplant and has a reference value for the design of high-speed, multi-channel data transmission systems.

Keywords:data transmission; SERDES; FPGA; high speed

收稿日期:2016-03-09

作者简介:王平安(1988-),男,助理工程师,硕士,研究方向:雷达信号处理与FPGA硬件开发;吴卫(1977-),男,高级工程师,硕士,研究方向:雷达信号处理与FPGA硬件开发;于志伟(1988-),男,助理工程师,硕士,研究方向:波束控制系统研究;陈文攀(1989-),男,助理工程师,硕士,研究方向:协同信号处理。

中图分类号:TN919.3

文献标志码:A

文章编号:1009-0401(2016)02-0038-05