PIN光电探测器用反外延片工艺研究

李 杨,李明达

(中国电子科技集团公司第四十六研究所 天津300220)

PIN光电探测器用反外延片工艺研究

李 杨,李明达

(中国电子科技集团公司第四十六研究所 天津300220)

创新性使用反外延法工艺,介绍了适用于制备近红外波段PIN光电探测器的硅外延材料的研制工艺,在区熔单晶抛光片上进行重掺导电层和支撑层的外延层制备。通过对硅源流量与掺杂剂浓度的精确控制,实现了快速外延生长和高浓度掺杂。通过精细的后期加工工艺,将高阻区熔层加工为厚度和表面质量均满足器件要求的有源层。结果显示,采用反外延法工艺得到的反外延材料片应用到PIN光电二极管中,不仅节省器件制备中的工艺程序,而且大大提高了器件耐压性。

PIN光电探测器 反外延片 重掺导电层 支撑层

0 引 言

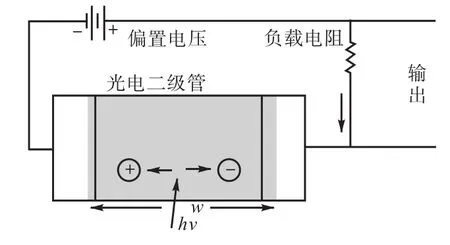

光电探测器在军事和国民经济的各个领域有着广泛用途,例如:在可见光或近红外波段主要用于射线测量和探测、工业自动控制、光度计量等;在红外波段主要用于导弹制导、红外热成像、红外遥感等方面。通常禁带宽度或杂质离化能合适的半导体材料都具有光电效应,但是制造实用性器件还要考虑性能、工艺、价格等因素。一般用于可见光波段的光电导探测器材料有CdS、CdSe、CdTe、Si、Ge等;近红外波段有PbS、InGaAs、PbSe、InSb、Hg0.75Cd0.25Te等;大于8,μm的波段有Hg1-xCdxTe、PbxSn1-x、Te、Si掺杂、Ge掺杂等;其中,CdS、CdSe、PbS等材料可以制成多晶薄膜形式的光电导探测器。最普通的光电探测器为PIN光电二极管。其结构如图1所示。

图1 外加反向偏置电压的PIN光电二极管的电路示意图Fig.1Diagram of additional reverse bias voltage of PIN photodiode circuit

光电探测器的工作原理为光电效应,当一个入射光子能量大于或等于半导体的带隙能量时,将激励价带上的一个电子吸收光子的能量而跃迁到导带上,此过程产生自由的电子-空穴对。在光电二极管的PN结中间引入一层浓度很低的N型半导体,就可以增大耗尽区的宽度,达到减小扩散运动影响,提高响应速度的目的。由于这一掺入层的掺杂浓度低,近乎本征半导体,故称I层,因此这种结构成为PIN光电二极管。I层较厚,几乎占据了整个耗尽区。绝大部分的入射光在I层内被吸收并产生大量的电子-空穴对。在I层两侧是掺杂浓度很高的P型和N型半导体,P层和N层很薄,吸收入射光的比例很小。因而光产生电流中漂移分量占了主导地位,这就大大加快了响应速度。[1]

由于硅材料的物理特性,应用本征高阻硅外延片(电阻率>1,000,Ω·cm,厚度:50~100,μm)制备的PIN光电二极管主要应用于民品领域;近红外探测器对硅材料要求极高——超高电阻率、超厚层,外延工艺无法实现。长期以来,器件研究单位均采用区熔单晶作基底,但是由于接触电阻过大,器件性能受到极大的制约。

本文转换设计思路,采用反外延工艺,即与普通的外延片用法相反,把外延层作为衬底,而把衬底作为制作器件PN结的区域。整个材料制备过程为:选用器件所需电阻率的区熔单晶为衬底,在高阻区熔衬底上利用外延工艺生长重掺导电层和支撑层,为器件制造提供电极及物理支撑层,利用减薄和机械化学抛光工艺将高阻区熔层加工为厚度、表面质量符合要求的有源层,为其提供N型反外延材料。其优点为:制作PN结的区域(区熔单晶衬底区域)电阻率可达到几千Ω·cm,接近于绝缘体,并且厚度可通过后期加工至器件要求值,可大大提高器件的耐压性,降低器件的插损;外延层作为基底层,需尽量降低串联电阻,外延层浓度需在1018,cm-3以上,并且外延层要有一定厚度,防止碎片。

1 工艺实验

1.1 外延设备

硅外延的沉积设备为意大利LPE公司生产的PE-3061D平板式外延炉,基本结构如图2所示。该外延炉采用高频感应的加热方式,具有维护简单、生产效率高的特点,是目前各外延制造企业主流的15.24~20.32,cm硅外延片的生产设备。此设备为单圈平板炉,每炉可生产8片15.24,cm外延片。

图2 PE3061D平板式外延炉结构图Fig.2 Plate-type epitaxial furnace structure of PE3061D

1.2 工艺技术

本文采用常压外延工艺,反应室压力维持在0.1,MPa。采用高纯度三氯氢硅(SiHCl3)作为硅源,腔内反应化学式如下:

反应气体H2经过纯化器的纯化,纯度可以达到6,N以上,生长温度保持在1,150,℃。

2 实验结果及分析

在反外延材料片的制备过程中,面临的难点有3个方面:①如何实现厚层外延片的快速生长;②如何得到低电阻率的重掺导电层;③如何对反外延片进行加工,使其厚度、表面质量符合要求。本文针对上述3个方面开展了大量实验工作。

2.1 快速外延生长

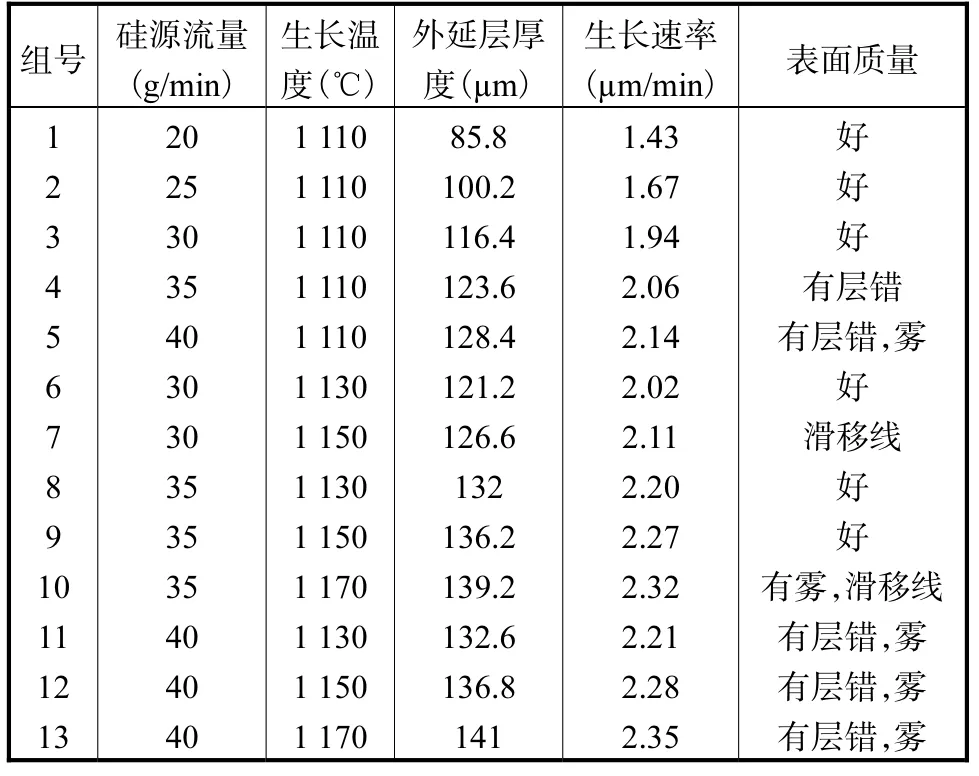

根据外延生长机理,影响外延生长速率的因素主要有硅源浓度和外延生长温度。[2-3]为了提高外延生长速率,从这两方面着手试验。首先为了提高硅源的浓度,尝试4种不同硅源流量,记录其生长速率。同时,适当提高外延反应温度,以提高外延生长速率。从改变外延生长温度和硅源流量着手,以不同的生长条件进行了13组实验,生长速率结果及外延表面状况如表1所示。

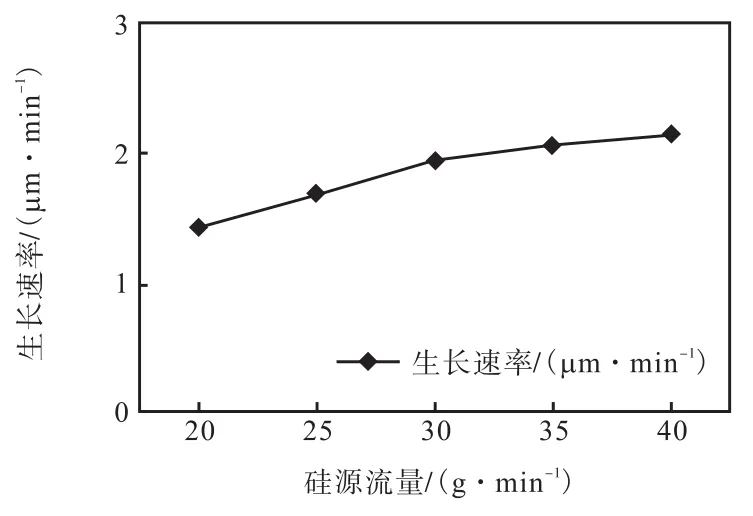

根据表1的前5组实验测试结果,绘制出图3所示的曲线。可以看出,在1,110,℃时,随着硅源流量的增大,外延生长速率也随着增加,当SiHCl3的流量增加到30,g/min前,生长速率增长最快;继续增加SiHCl3流量至35,g/min后,增长趋缓。这是由于随着硅源浓度的增加,外延反应的副产物HCl的浓度也增加,腐蚀作用增强,生长速率增长趋势减缓。同时使用过大的硅源流量,因温度固定,表面迁移速率过小,外延层结晶质量变差,外延层表面出现层错。

表1 外延生长速率工艺试验条件Tab.1 Test conditions for epitaxial growth rate process

图3 硅源流量与生长速率关系曲线Fig.3 Relationship between the growth rate curves and silicon source traffic

但从上面结果来看,硅源流量过大时,因温度过低,表面质量变差,出现雾状表面缺陷。所以本文针对高SiHCl3流量的3种规格(30,g/min、35,g/min、40,g/min)相应提高工艺温度,相应结果在表1中列出。当硅源流量一定时,升高温度,生长速率增大,但温度过高时,外延表面会出现滑移线等表面缺陷。当硅烷流量达到40,g/min,温度升高至1,170,℃时,结晶质量仍然较差。

本文主要针对高速外延生长,从实验结果发现,在35,g/min的硅源流量下,温度控制在1,130~1,150,℃范围生长出结晶质量较好的外延片,生长速率为2.27,µm/min。这也是研究中在生产重掺导电层和支撑层时最终采用的主工艺条件。

2.2 高浓度掺杂

硅外延掺杂剂的掺入,受含掺杂剂气体的输入分压、生长温度和生长速率的影响[4-5],而输入分压是决定因素。本文所研制的PIN光电二极管用硅反外延材料,外延层掺杂浓度要求在4.7×1018,cm-3以上,属高浓度掺杂。由于硅外延层的掺杂浓度受掺杂剂气体的输入分压影响较大,因此从提高掺杂剂的输入分压入手。实验选用了常规的磷烷做n型掺杂剂,先后采用含量为2%,和4%,的磷烷分别进行了实验,结果如表2所示。发现当把系统设定在一个较高值,即采用4%,浓度的PH3时,载流子浓度为7×1018,cm-3,达到参数指标要求。

表2 外延生长不同磷烷浓度工艺试验Tab.2Epitaxial growth process under different concentrations of phosphine

2.3 反外延片后期加工

使用外延工艺在区融衬底上得到重掺导电层和支撑层之后,研究人员对反外延片进行后道加工,使其厚度和表面质量满足器件使用要求。采用减薄机对外延片进行减薄,之后通过机械化学抛光去除表面损伤层、优化几何参数和表面质量。最终加工结果如表3所示。区熔材料厚度维持在(212±1)μm,总厚度变化、翘曲度、弯曲度都在10,μm以内,表面达到免洗水平。

表3 反外延片加工最终结果Tab.3 Anti-epitaxial wafer processing and the final result

3 结 论

通过增加反应原材料浓度和适当提高温度的方法来提高外延生长速率,最终得到2.27,µm/min的生长速率,成功研制出超厚外延层的外延片。同时采用提高磷烷输入分压的方法,解决重掺导电层超高浓度掺杂的问题。最后对反外延片进行后期精细加工,使区熔层的表面质量达到较高水平。经过以上方案,成功研制出厚度为200,μm、掺杂浓度4.7×1018,cm-3以上的重掺导电层;厚度150,μm以上的支撑层。反外延片应用到PIN光电二极管中,不仅节省了器件制备中的工艺程序,而且大大提高了器件的耐压性。

[1] 江利. 微波PIN二极管的设计与制备工艺研究[D].合肥:合肥工业大学,2005.

[2] 王鹏. 外延层的工艺控制与实际应用[D]. 天津:天津大学,2012.

[3] 甄可龙. 硅外延生长电阻率与厚度一致性的研究[D].天津:河北工业大学,2003.

[4] 张文清. 6英寸IGBT用硅外延材料制造工艺的设计与实现[D]. 南京:东南大学,2011.

[5] 郭锐. 毫米波雪崩管用硅外延材料的研究及应用[D].南京:东南大学,2010.

On Preparation Technology of PIN Photodetector with Anti-Epitaxial Wafer

LI Yang,LI Mingda

(The 46th Research Institute of China Electronics Technology Group Corporation,Tianjin 300220,China)

This paper introduces the research of silicon epitaxy material process applicable to the near infrared band PIN photodetector by using the anti-epitaxy method of process innovation ideas to carry out epitaxial layer preparation for heavy doped conductive layer and support layer on FZ monocrystalline polished wafer.Through a precise control of silicon source flow and dopant concentration,rapid epitaxial growth and high concentration of doping were achieved.By using elaborate post-processing technology,the high resistance zone melting layer thickness and surface processing for active layer quality can satisfy the requirements of the device.The results show that with the application of anti-epitaxial material to PIN photoelectric diode,not only can device preparation process be saved,but also voltage resistance of the device greatly improves.

PIN photodetector;anti-epitaxial wafer;heavy doped conductive layer;support layer

TN304

:A

:1006-8945(2016)04-0034-03

2016-03-11