基于时序图的异步时序逻辑电路的设计

高美蓉

(宝鸡文理学院 物理系,陕西 宝鸡 721016)

基于时序图的异步时序逻辑电路的设计

高美蓉

(宝鸡文理学院 物理系,陕西 宝鸡 721016)

摘要:在异步时序逻辑电路的设计过程中,以波形分析为基础,通过电路的状态转换图得到电路的时序图,通过时序图的分析确定触发器的时钟方程,在时钟方程的作用下得到状态转换,填写次态卡诺图,通过次态卡诺图的化简得到输出方程和状态方程的设计方法。该方法简单实用,学生易于理解和接受。

关键词:异步时序逻辑电路;时序图;时钟信号

在逻辑电路中,任一时刻的输出不仅取决于该时刻电路的输入信号,而且还取决于前一时刻电路的状态,具有这种逻辑功能特点的电路称为时序逻辑电路。时序逻辑电路按照动作特点又可分为同步时序逻辑电路和异步时序逻辑电路。同步时序逻辑电路是所有触发器状态的变化都是在同一时钟信号操作下同时发生;异步时序逻辑电路是触发器的状态变化不是同时发生的。实际应用中,时序问题千变万化,一些现成的功能集成块往往不能满足需要,所以时序电路的设计方法就显得十分重要。在异步时序电路设计过程中,关键是如何确定时钟脉冲。为此,本文总结多年的教学经验,探讨一种以波形分析为基础,通过电路的状态转换图得到电路的时序图,通过时序图的分析确定触发器的时钟信号的通用设计方法。教学实践证明,这种方法简单易掌握,不容易出错。

1设计方法

异步时序电路的设计过程与同步时序电路的设计大体相同,在设计异步时序电路时,除了需要完成设计同步时序逻辑电路所应做的各项工作外,还要为每个触发器选定合适的时钟信号。而异步时序电路中各个触发器的时钟并不是来源于同一个,所以除了要确定各触发器的激励函数表达式外,还要确定各个触发器的时钟信号表达式,这就是设计异步时序电路时所遇到的特殊问题。通常情况下,异步时序逻辑电路各触发器的时钟是由函数计算得到的,改进后的方法是通过分析时序波形图来确定的,这样就省去了一些复杂的计算步骤。归纳起来,异步时序逻辑电路的设计可按下述步骤进行[1-2]:1)进行逻辑抽象,列出电路的原始状态转换图和状态转换表;2)进行状态化简,分析每个状态是否都是必不可少的,是否需要进行状态化简;3)确定二进制代码的位数,即确定触发器的数目,对电路状态进行编码,画出编码后的状态图;4)选择触发器的类型,列出时钟方程、输出方程和状态方程表达式;5)根据得到的方程式画出逻辑电路图;6)检查设计的电路能否自启动。

在异步时序逻辑电路的设计过程中应注意如下几点。

1)在列输出方程时,无效状态对应的最小项应该当成约束项处理。因为电路工作时,这些状态是不会出现的[3]。

2)在列状态方程时,注意一些特殊约束项的确认和处理,以得到更加简单的状态方程。

3)为每个触发器挑选合适的时钟信号是异步时序逻辑电路设计的难点,挑选时钟信号的原则是在触发器的状态应该翻转时必须有时钟信号发生,触发器的状态不应翻转时多余的时钟信号越少越好,这将有利于触发器状态方程和驱动方程的化简;因此,可以由状态转换图画出电路的时序图,通过时序图的分析来确定各触发器的时钟信号。

2设计举例

使用JK触发器设计一个十二进制的异步加法计数器,并要求所设计的电路能自启动,设计步骤如下。

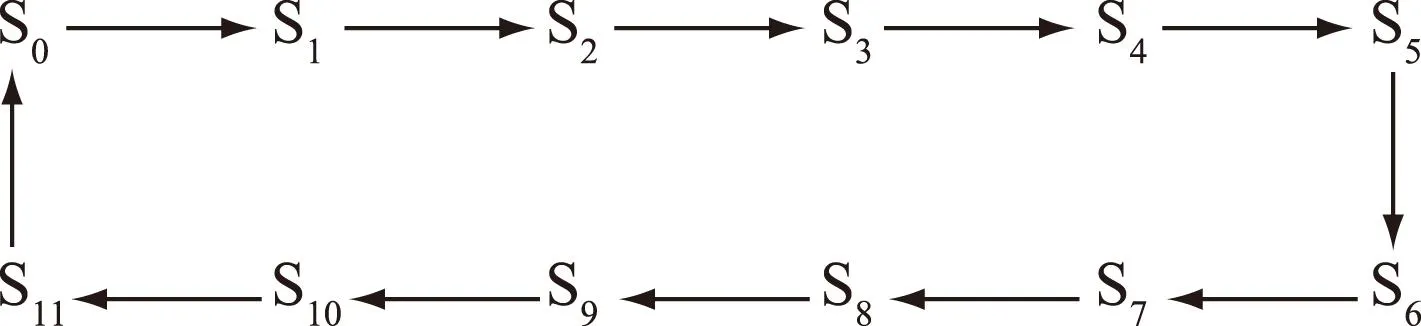

1)根据十二进制加法计数器规则,必须有12个有效状态,依次为S0、S1、S2、S3、S4、S5、S6、S7、S8、S9、S10和S11,电路的原始状态转换图如图1所示。

图1 电路的原始状态转换图

2)通过分析这12个状态都是必不可少的,不需要进行状态化简。

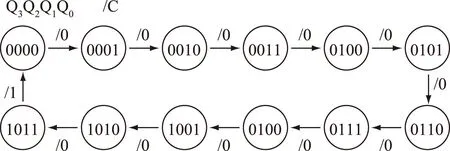

3)十二进制的加法计数器有12个有效状态,需要用4位的二进制码表示。依次为0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010和1011,即用4个触发器。若令Si=Q3Q2Q1Q0,进行编码得到电路的状态转换图(见图2)。

图2 电路的状态转换图

4)选取下降沿JK触发器设计该电路,列时钟方程、输出方程和状态方程表达式[4]。

列各个触发器的时钟方程时,可以由电路的状态转换图画出电路的时序图(见图3)。观察电路的时序图,确定每个触发器的时钟信号。为触发器挑选时钟信号的原则是:触发器的状态翻转时必须有时钟信号发生;触发器的状态不应翻转时多余的时钟信号越少越好,这将有利于触发器状态方程和驱动方程的化简。根据上述原则,观察图3电路的时序图可见,Q0的状态每次改变时,观察clk0、Q1、 Q2和Q3的波形,只有在clk0的每个下降沿到来时, Q0的状态发生改变。故只能用clk0作为触发器FF0的触发脉冲CP0;同理,对Q1每次状态发生改变时,有clk0和Q0的下降沿来临,故可用clk0或Q0作为FF1的触发脉冲CP1。依此类推,Q2可用clk0、Q1或Q0作为其触发脉冲CP2; Q3可用clk0、Q1或Q0作为其触发脉冲CP3。当选用CP0=CP1=CP2=CP3=clk0时,所设计的电路为同步时序逻辑电路。依据触发器挑选时钟信号的原则, 得到时钟方程CP0= clk0,CP1=Q0,CP2=Q1,CP3= Q1。

图3 电路的时序图

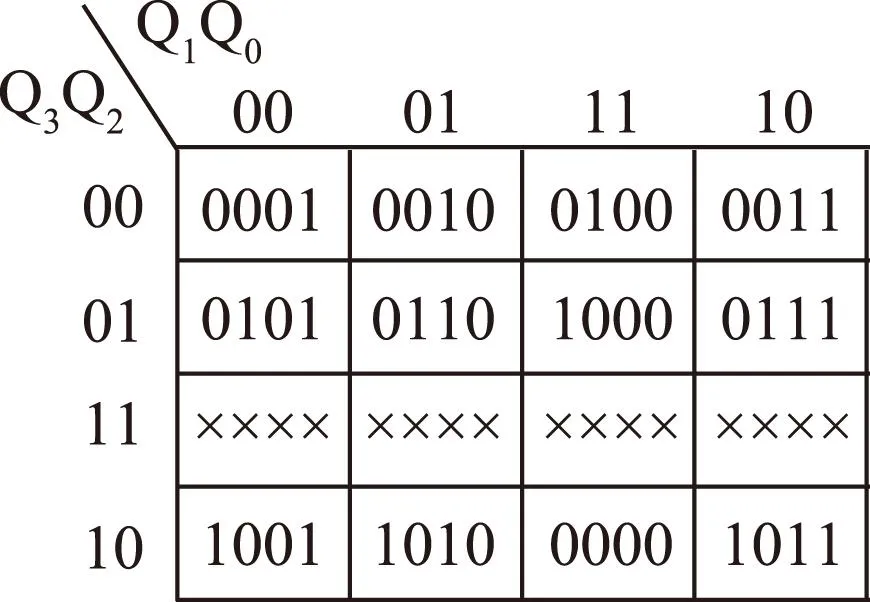

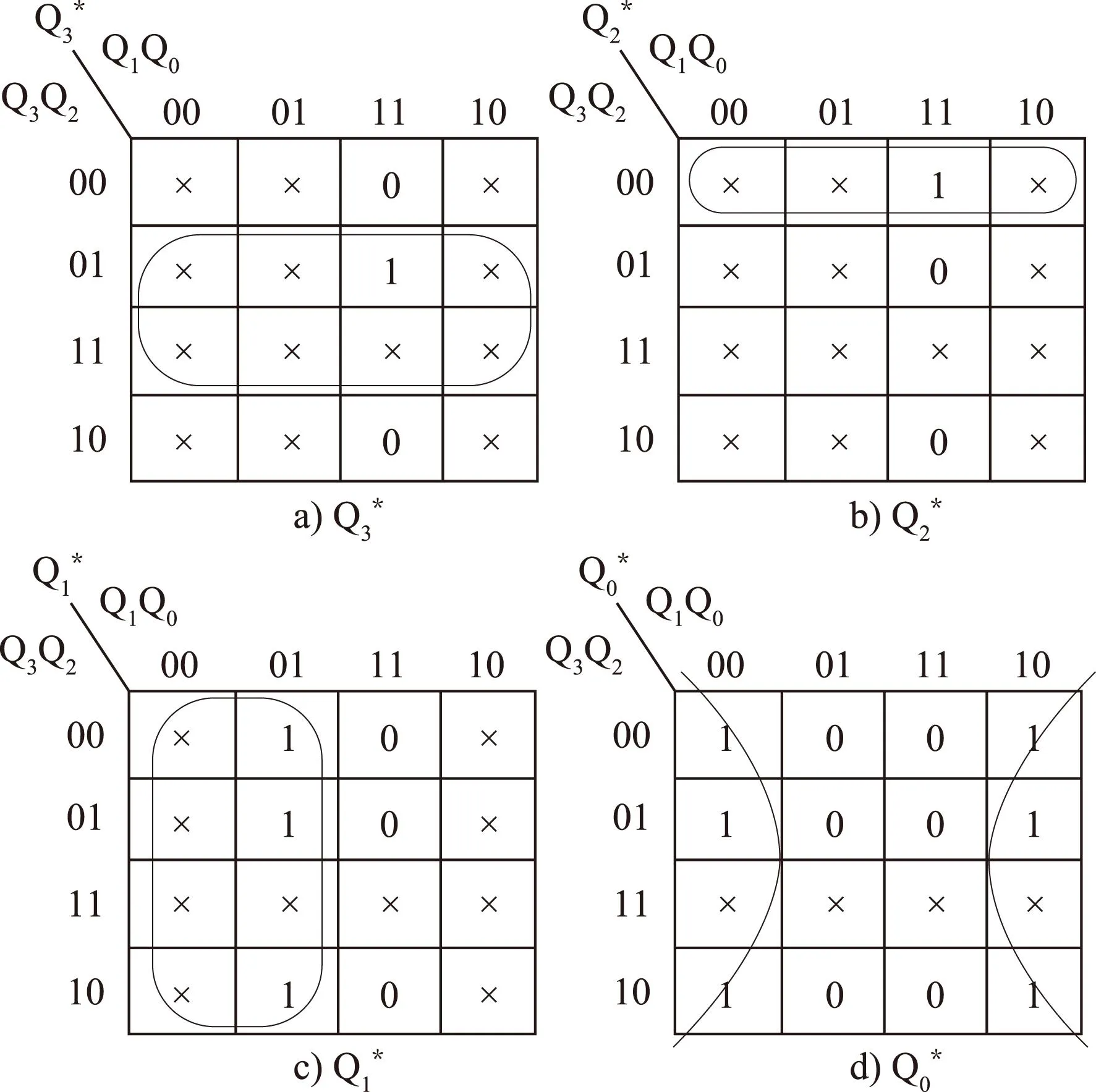

列电路的状态方程,需要做出电路的次态卡诺图(见图4),然后将它分解为表示Q3*、Q2*、Q1*和Q0*的卡诺图[5](见图5)。在次态卡诺图的表示过程中,把没有时钟信号的次态也作为任意项处理,以利用状态方程的化简。例如,在图5所示的Q3*的卡诺图中,当现态为0000、0001、0010、0100、0101、0110、1000、1001和1010时,电路向次态的转换过程中时钟信号Q1没有下降沿产生,因而这9个状态作为卡诺图的无关项处理。另外,由于正常工作时不会出现1100、1101、1110和1111这4个状态,因而也把这4个状态作为无关项处理。同理,可得Q2*、Q1*和Q0*的次态卡诺图。

图4 电路的次态卡诺图

图5 卡诺图的分解

对图5所示的次态卡诺图进行化简,得到电路的次态方程为:

该电路选取下降沿JK触发器设计,则应将该状态方程变换成JK触发器特性方程的标准形式,即Q*=J Q′+K′Q,然后就可以找出驱动方程了。为此,将上式改写为:

经变形后的逻辑式与JK触发器的特性方程对比,得到各触发器的驱动方程为:

根据电路的状态转换图,画出输出C的卡诺图(见图6),由图6得到:

C= Q3Q1Q0

图6 电路输出的卡诺图

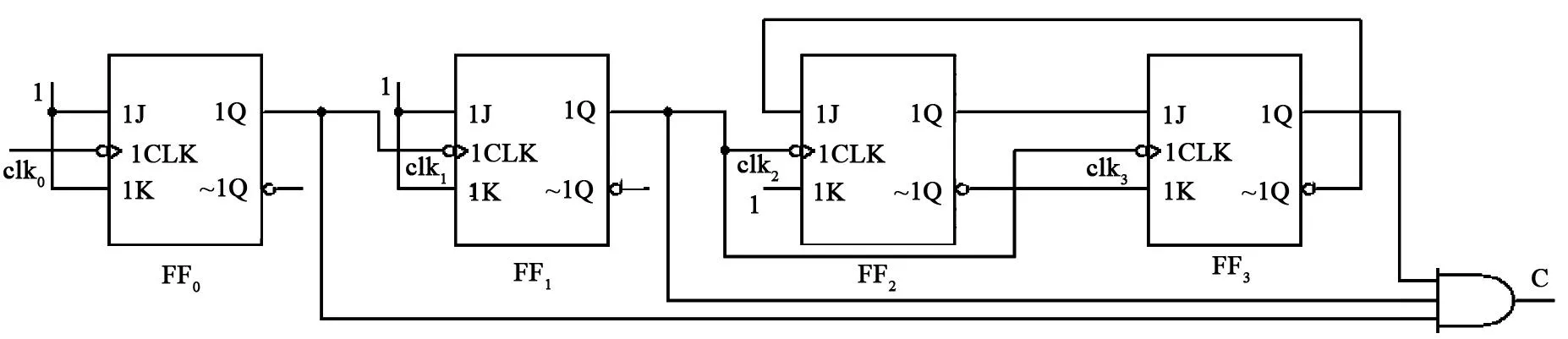

图7 逻辑电路图

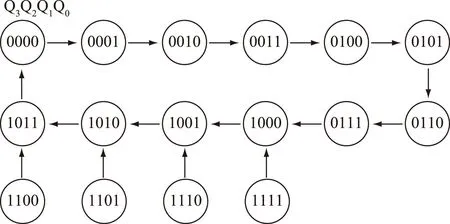

5)根据得到的时钟方程、输出方程和状态方程,画出逻辑电路图(见图7)。6)检查设计的电路能否自启动。将1100、1101、1110和1111这4个无效状态分别代入状态方程,求其次态,得到完整的电路状态转换图(见图8)。这4个无效状态分别经过1个时钟脉冲进入到有效循环,表明电路是可以自启动的。

图8 完整的电路状态转换图

3结语

在异步时序逻辑电路的设计过程中,通过电路时序图的分析可以很方便地确定时钟方程,进而利用广泛的约束条件,得到最简次态方程,对比列出驱动方程,使逻辑电路最简化,为异步时序逻辑电路的设计提供了一种新的设计思路。设计实例表明, 使用该方法在设计和分析异步时序逻辑电路时,更加快捷、准确,并易于理解和接受。该设计方法同样也适用于同步时序电路设计,是传统同步时序电路设计的延伸。教学实践证明,该方法能普遍为学生所掌握。

参考文献

[1] 张继军.同步和异步时序逻辑电路统一设计的新方法[J].计算机工程与应用,2003(17):136-138.

[2] 康华光.电子技术基础.数字部分[M].4版.北京:高等教育出版社,2000.

[3] 赵兴强.异步时序逻辑电路设计的一种简明方法[J].西华师范大学学报:自然科学版,2004(6):227-230.

[4] 吕虹,张海峰.基于时钟设计的异步时序逻辑电路设计法[J],电气电子教学学报,2002(6):72-74.

[5] 雷 轩,卢 超. 异步时序逻辑电路的分析与设计[J]. 计算机时代,2014(5):19-22.

责任编辑马彤

The Circuit Self Starting Design of the Improved Method based on the JK Drive Equation

GAO Meirong

(Physics Department, Baoji College of Arts and Sciences, Baoji 721016, China)

Abstract:The Design of asynchronous sequential logic circuit is based on the waveform analysis,and through the state of the circuit transition diagram circuit timing diagram.The flip-flop clock equation is determined by the analysis of the sequence diagram. Obtain state transitions under the action of a clock equation,and fill in the next state karnaugh map.Design the method of output equation and the equation of state by state Karnaugh graph simplification. The method is simple and practical,and can easy be understood and accepted by students.

Key words:asynchronous sequential logic circuit, timing sequence diagram, clock signal

收稿日期:2015-08-31

作者简介:高美蓉(1980-),女,讲师,硕士,主要从事应用电子技术教学等方面的研究。

中图分类号:TN 79

文献标志码:A