基于ZYNQ的多传感器实时图像拼接技术研究

冯 鑫,汪陈跃,孙爱平,赵 强,雷旭峰,董海翔,康丽珠,杨增鹏

基于ZYNQ的多传感器实时图像拼接技术研究

冯 鑫,汪陈跃,孙爱平,赵 强,雷旭峰,董海翔,康丽珠,杨增鹏

(昆明物理研究所,云南 昆明 650223)

为满足高速多传感器大视场图像处理系统结构紧凑、高实时性的迫切要求,进行了以全可编程平台ZYNQ为基础的多传感器实时图像拼接技术研究。重点介绍了该设计的基本架构、工作原理及ZYNQ的功能模块设计等,通过对图像处理的结果表明,该技术满足高速实时图像处理的要求,同时可以扩展到更为复杂的多传感器大视场实时图像处理任务。

ZYNQ;图像拼接;实时图像;多传感器

0 引言

随着军事分离口径成像系统的发展,在多传感器实时图像处理系统中,如何在规定时间内完成大量图像数据的处理,满足系统的实时性要求一直是人们重点关注的问题。随着大规模集成电路的发展,各种处理器及专用集成电路的性能不断得到提高,人们对图像处理系统的功能、性能、功耗、体积等都提出了更高的要求。常见的多传感器大视场图像处理系统大多采用多DSP+FPGA架构[1-2]或者CPU+GPU架构[3],这样的架构造成了该系统成本高、体积大、功耗高、设计相对不灵活、设计复杂,增加系统开发周期等缺点。本系统鉴于满足多传感器图像处理系统中数据运算量大、实时性强,数据传输率高,尤其是对体积、功耗要求严苛的情况下,开展了以全可编程SOPC为基础的多传感器实时图像拼接技术研究,不仅可以通过软件增加系统的灵活性和可扩展性,同时还能通过可编程硬件实现执行更多的数据处理和决策功能[4]。

1 系统框架

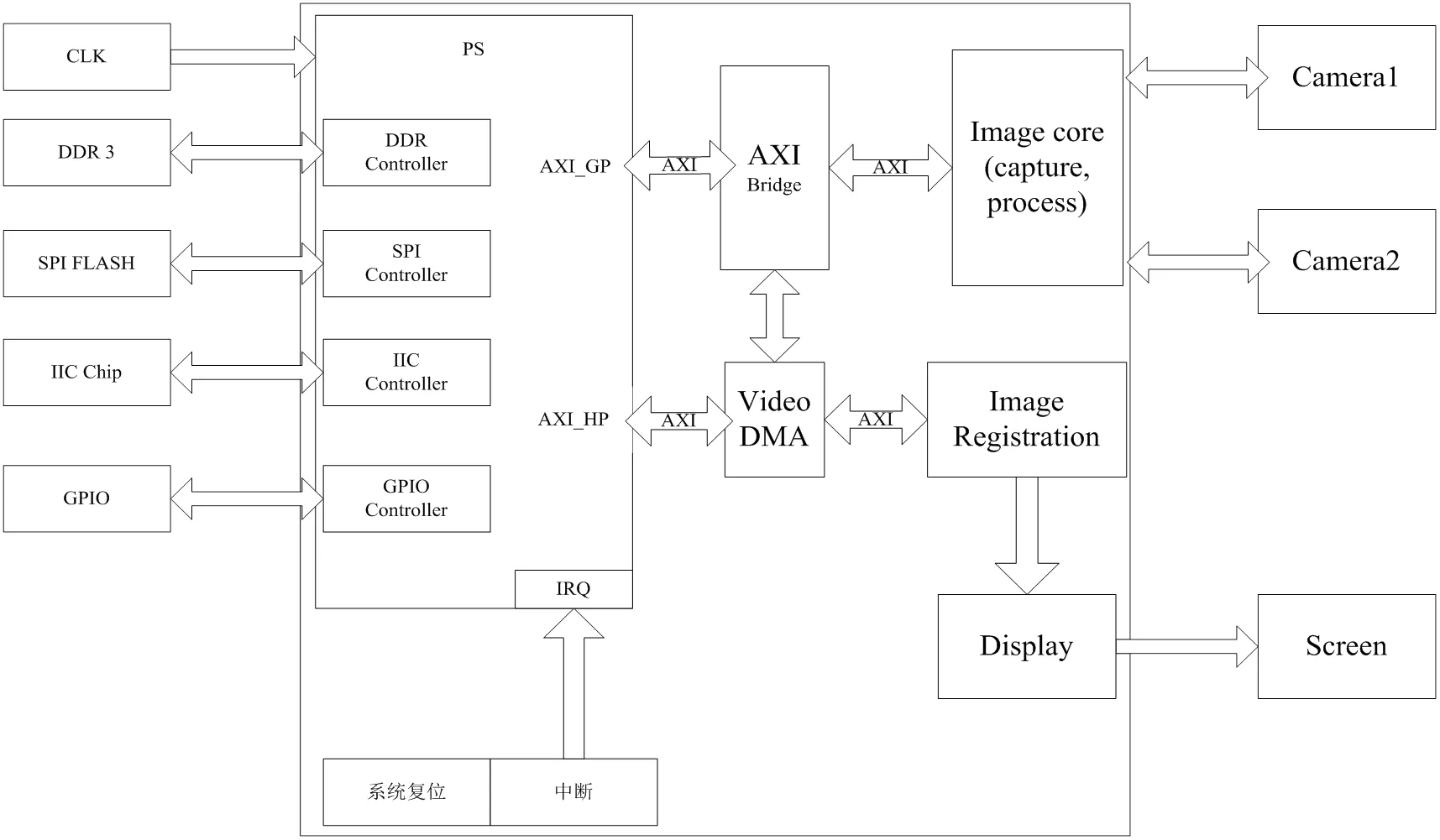

本系统采用美国Xilinx公司推出的业界第一款全可编程平台ZYNQ作为图像拼接技术研究的主要硬件平台。主要包括图像采集、图像预处理、图像传输、图像配准及图像拼接显示几个模块。系统设计框图如图1所示。

系统通过2个图像传感器采集图像,经过ZYNQ内部的图像采集及预处理,图像传输,图像存储,图像配准后,最终图像显示。ZYNQ片内的PL(可编程逻辑)和PS(处理器系统)之间的数据是通过基于AXI4.0协议的片内总线传输的,AXI4.0是由ARM和Xilinx公司基于ARM公司的AMBA3.0总线协议共同提出的,是一种高性能、高带宽、低延迟的片内总线[5],通过AXI总线将Zynq-7000内PS和PL紧密地耦合在一起。通过采集外部摄像头1和摄像头2的图像数据,经过图像预处理模块,将数据打包成AXI4-Stream总线格式数据,然后经过Video DMA控制器,将数据从AXI_HP接口写入DDR3控制器后,写入外部DDR3存储器,再将数据从DDR3中读出,完成数据的高速率吞吐。数据以较高速率流入图像配准模块,最后至图像显示模块,完成跨时钟域图像处理,将数据解调成符合显示时序的数据格式。

图1 系统框图

2 功能模块设计

2.1 图像捕获及预处理模块

本文采用CMOS传感器,传感器阵列为640×480。CMOS传感器具有高帧频、可配置、功耗低、成本低等优点,在众多领域都有应用。本系统通过I2C总线对CMOS进行配置,输出RAW RGB格式的图像数据,每个像素为8bit。其配置电路,捕获及预处理模块如图2、图3所示。

图像传感器通过I2C接口配置后,给出配置结束信号i2c_cfg_done,接收此信号后才开始进行完整帧图像采集。在像素时钟cmos_pclk的节拍下,图像数据cmos_data[7:0]在图像传感器的行有效信号cmos_href及场有效信号cmos_vsync的作用下,将数据输入至ZYNQ。在ZYNQ内部,对2路视频流同时捕获,将数据送至图像预处理模块。图像预处理模块接收到图像采集模块的数据,通过插值算法将RAW RGB格式的数据转换为RGB888格式的数据,进而得到了每秒60帧24位640×480像素。

2.2 图像传输模块

图像数据是基于AXI4-Stream总线协议进行传输的,通过调用Xilinx公司提供的AXI Video DMA IP软核实现数据传输。CPU通过接受来自图像捕获和预处理模块的完成标志信号,通过AXI4-Lite总线配置AXI Video DMA模块,初始化结束后开始传输数据。图像预处理模块的输出数据要转化为基于AXI4-Stream总线协议格式,数据经过AXI-HP接口,以DMA(Direct Memory Access)的方式将数据存储至外部数据存储器DDR3,在适当的时候再以DMA的方式从DDR3中读出,再进行后续的图像配准处理。DMA搬移数据的方式是PL与外部数据存储器数据交互的时间最快、吞吐率最高的一种方式,可以极大的满足系统的实时性,数据传输的过程中并不占用CPU,进而提高了系统性能。

图2 图像传感器配置电路连接框图

图3 图像捕获及预处理框图

2.3 图像配准模块

图像拼接算法的性能主要取决于图像配准的精度,配准算法既要保证配准精度算法的运算时间又要满足实时性的要求[6]。系统通过机械结构固定好图像传感器,保证所成的图像之间只存在水平方向的位移,所以这里采用可以有效提取出图像位移的图像配准算法——相位相关法进行图像配准点的提取。图像的相位相关配准算法,主要是将图像进行傅里叶变换,计算2幅图像的互功率谱,再对互功率谱求傅里叶反变换得到冲激函数,找出使该冲激函数取得最大值的位置,即为图像的平移量。具体原理描述如下:

其中1(,)和2(,)分别代表2幅图像,那么2幅图像的变换关系可以表示为:

2(,)=1(-0,-0) (1)

根据傅里叶变换性质可得:

式中:2(,)和1(,)是2(,)和1(,)的傅里叶变换。它们的互功率谱为:

式中:1*(,)是1(,)的复共轭,对互功率谱求傅里叶反变换,找到峰值的位置,即可以确定平移参数0与0。

计算一个点基2的快速傅里叶变换,需要有(/2)×log2次蝶形运算和2×log2次数数据访问。图像数据的傅里叶变换是对行列数据分别做傅里叶变换。一次复数的乘法运算包括包含4次乘法运算及3次加法运算。一幅×的图像经过傅里叶变换后产生2个复数,经过开方及除法运算后,算法的复杂度大大提高。考虑到硬件实现的局限性及硬件算法的精度问题,这里将采用Matlab对图像进行相位相关运算[7]。固定好图像传感器之后,采集图像,提取平移量,利用此平移量参与ZYNQ配准控制逻辑。

2.4 图像拼接显示模块

图像拼接显示模块的主要功能是完成基于AXI4-Stream总线数据的跨时钟域处理。本文设计了图像拼接显示模块用于完成AXI4-Stream总线的控制,发出DMA占用总线请求,访问DDR3存储器,同时将基于AXI4-Stream总线数据解调为符合终端显示的时序的数据。图像拼接显示模块如图5所示。

总线请求及数据解耦模块通过发动总线占用请求,发起读取内存请求,接收来自DMA控制器的数据,并将总线数据解码,将数据进行行缓存。图像显示控制模块根据接收到的coordinate[10:0]配准点信息,发出控制地址pixel_addr_0[9:0]和pixel_addr_1[9:0],读取相应的像素数据frame_pixel_0[23:0]和frame_pixel_1[23:0]。最终经过图像显示模块,可以输出2路视频图像的所有信息。

图4 图像配准模块功能图

图5 图像拼接显示模块框图

3 硬件资源消耗分析

表1表明在处理2路分辨率为640×480,帧率每秒60帧的数据所消耗的硬件资源数量。利用片内PS的硬核处理器(ARM CortexA9处理器)完成相应的硬件控制,极大地节省了相应的逻辑资源。同时借助于外部存储器及片内总线数据传输结构,最大限度地节省PL的存储资源。

表1 硬件资源消耗分析

4 实验测试结果

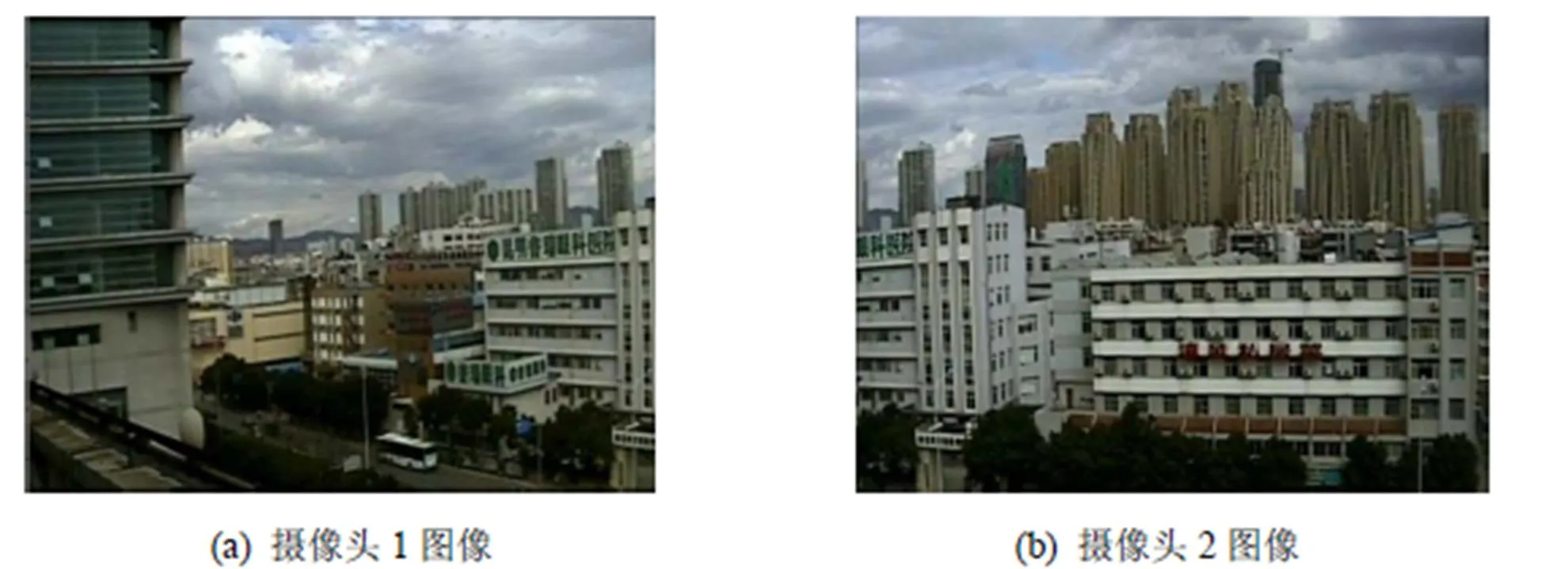

设计要求2幅图像的重叠区不大于7%。重叠区相对大,监控的目标视场角相对变小,信息损失,拼接起来相对容易。重叠区相对小,监控的目标视场角相对变大,信息丰富,拼接起来相对困难。图6给出了2个具有重叠区的摄像头所采集的图像。图7给出了拼接后的图像。拼接后的图像信息量大,没有冗余信息,经过实时处理之后,图像的大小为1180×480,帧率为每秒60帧,图像成像清晰。

表2给出了2路图像的拼接前后的参数,通过拼接前后的参数对比,可以看出每个图像传感器的水平视场角度为30°,拼接后的水平视场角为58.5°,有效地增大了目标观测的视场范围,且重叠区保持在5%左右,满足重叠区小于7%的设计要求。具备较好的成像效果,保证了系统的实时性,达到了预期的效果。

图6 两路采集图像

图7 ZYNQ拼接结果图

表2 拼接前后参数对比

5 结论

基于ZYNQ全可编程平进行图像拼接技术研究,进行了实时图像处理系统的采集、预处理、传输、拼接显示的模块设计,完成了每秒60帧640×480p的图像处理,与传统设计方案相比,可以使多传感器图像处理系统体积更小,成本更低,同时具有较好的实时性,更符合未来实时图像处理系统的发展需求。

[1] HAO Wei. Designing and develpoment of multi-DSP real-time image processing system based on FPGA[C]//, 2011: 1263-1265.

[2] 银志军. 基于多DSP和FPGA的实时图像处理系统设计[J]. 光电技术应用, 2012, 27(1): 76-80.

YIN Zhingjun. Design of real-time image processing system based on FPGA and multi-DSP[J]., 2012, 27(1): 76-80.

[3] 王雨曦, 王义坤, 葛明峰. 基于点特征算子的红外图像实时拼接系统[J]. 红外技术, 2015, 37(3): 204-209.

WANG Yuxi, WANG Yikun, GE Mingfeng. Point feature-based read-time infrared image mosaicking system[J]., 2015, 37(3): 204-209.

[4] 何宾. Xilinx All Programmable Zynq-7000 Soc设计指南[M]. 北京: 清华大学出版社, 2012: 13.

HE Bin.7000[M]. Beijing: Tsinghua university press, 2012: 13.

[5] Xilinx Inc. Xilinx AXI Reference Guide[R/OL]. [2015-09-09]. http:// www.xilinx.com/support/documentation/data_sheets/axi_reference_guide.

[6] 张云峰. 基于DSP的实时图像拼接技术[J]. 液晶与显示, 2013, 28(6): 963-966.

ZHANG Yunfeng. Real-time image mosaic technology based on DSP[J]., 2013, 28(6): 963-966.

[7] 杨磊, 任龙, 刘庆, 等. 基于FPGA的大视场图像实时拼接技术的研究与实现[J]. 红外与激光工程, 2015, 44(6): 1929-1935.

YANG Lei, REN Long, Liu Qing, et al. Research and implementation of large field image real-time mosaic technology based on FPGA[J]., 2015, 44(6): 1929-1935.

Research on Real-time Multi-sensor Image Mosaic Technology Based on ZYNQ

FENG Xin,WANG Chenyue,SUN Aiping,ZHAO Qiang,LEI Xufeng,DONG Haixiang,KANG Lizhu,YANG Zengpeng

(,650223,)

This paper conducts a research on a real-time multi-sensor image mosaic technology based on the all programmable platform, ZYNQ,in order to satisfy the urgent requirement of the compact structure and high level real-time in high-speed multi-sensor image processing system. This paper focuses on the basic architecture, operation principle and functional module design in ZYNQ. The result of processing digital images proves that the technology satisfies the requirement of high-speed real-time image processing. It can expand into the task for more complicated multi-sensor real-time image processing.

ZYNQ,image mosaic,real-time image,multi-sensor

TP311

A

1001-8891(2016)03-0207-04

2015-09-09;

2016-01-12.

冯鑫(1989-),吉林通化人,硕士研究生,主要研究方向为图像处理。