军用大规模集成电路关键外协工序控制

张 玲,田 泽

(1.中国航空工业集团公司 西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

军用大规模集成电路关键外协工序控制

张 玲1,2,田 泽1,2

(1.中国航空工业集团公司 西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

随着半导体技术的进步和发展,专业化分工越来越精细,后端设计、流片加工、封装、测试都已成为专门领域。而集成电路设计、加工各个环节环环相扣密不可分,任何一个环节出现问题都可能导致整个芯片流片的失败。因此如何保证每一个环节的正确性,是每一个集成电路设计单位都面临的问题,其中如何控制集成电路设计的关键外协工序也就变得尤为重要。文中对目前军用大规模集成电路的后端设计、芯片制造、封装的流程及关键工序进行了分析和论述,总结了设计方应重点关注的芯片的后端设计、流片、封装的工艺流程、关键工序及检查方法,对集成电路设计关键外协工序质量控制有较好的指导意义。

后端设计;芯片制造;芯片封装;关键工序控制

0 引 言

集成电路是信息产业的核心,随着半导体技术的进步和产业发展,专业化分工越来越精细,集成电路产业从最初的IDM模式发展到目前设计[1-2]、制造、测试[3]分离的局面,产生了众多专业从事集成电路设计的公司。通常情况下,集成电路设计公司只负责电路设计,芯片的流片、封装、测试均由专业机构承担,外协过程的质量,在很大程度上直接决定着集成电路产品的质量和成本。对于广大设计公司而言,集成电路的外协过程进行质量控制已成为产品成败的关键。对供应商的质量控制已成为集成电路设计企业项目及质量管理[4-5]的重要组成部分。

为提升芯片产品质量,需要建立科学规范的流程,设置质量控制点,建立质量控制方法和程序,按照PDCA的思想持续改进[6-7]。文中根据外包外协的材料或服务对集成电路产品特性影响的重要程度,重点对物理设计、制造、封装三个环节进行分析,总结提出了每个环节的质量控制点和控制方法。

1 关键外协工序质量控制方法

1.1 集成电路后端设计流程及关键工序

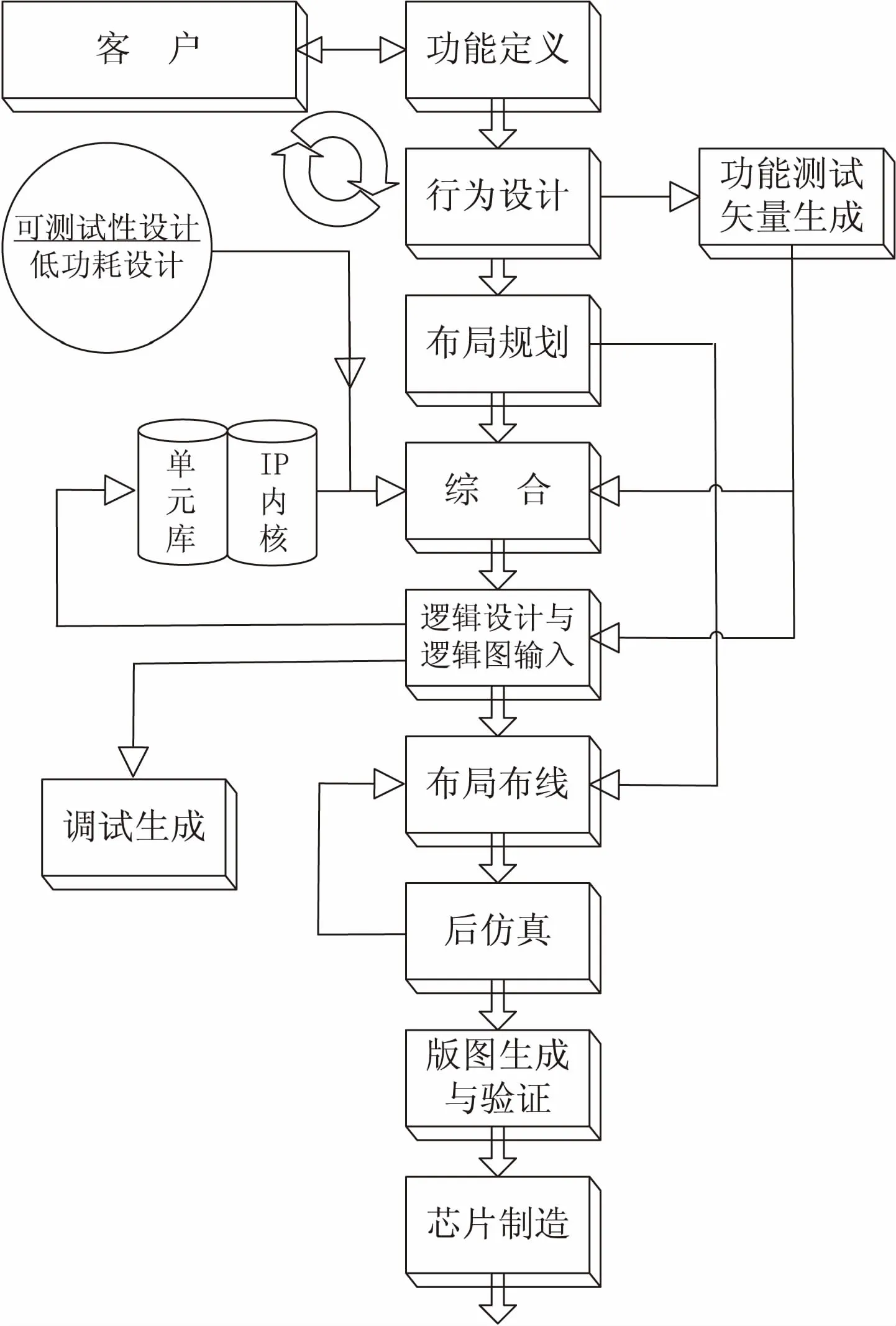

随着集成电路专业分工的日益精细,后端版图设计已经发展为一个独立的专业,版图设计是制造集成电路的基础。计算机辅助的版图设计将电路中所有元器件及其相互连接转换成能进行芯片光刻加工、正确可靠的掩模图形数据。专门的掩模制备公司利用所提供的数据,制备出符合流片需要的多层掩模版。通常的集成电路后端设计流程如图1所示。

图1 集成电路后端设计流程

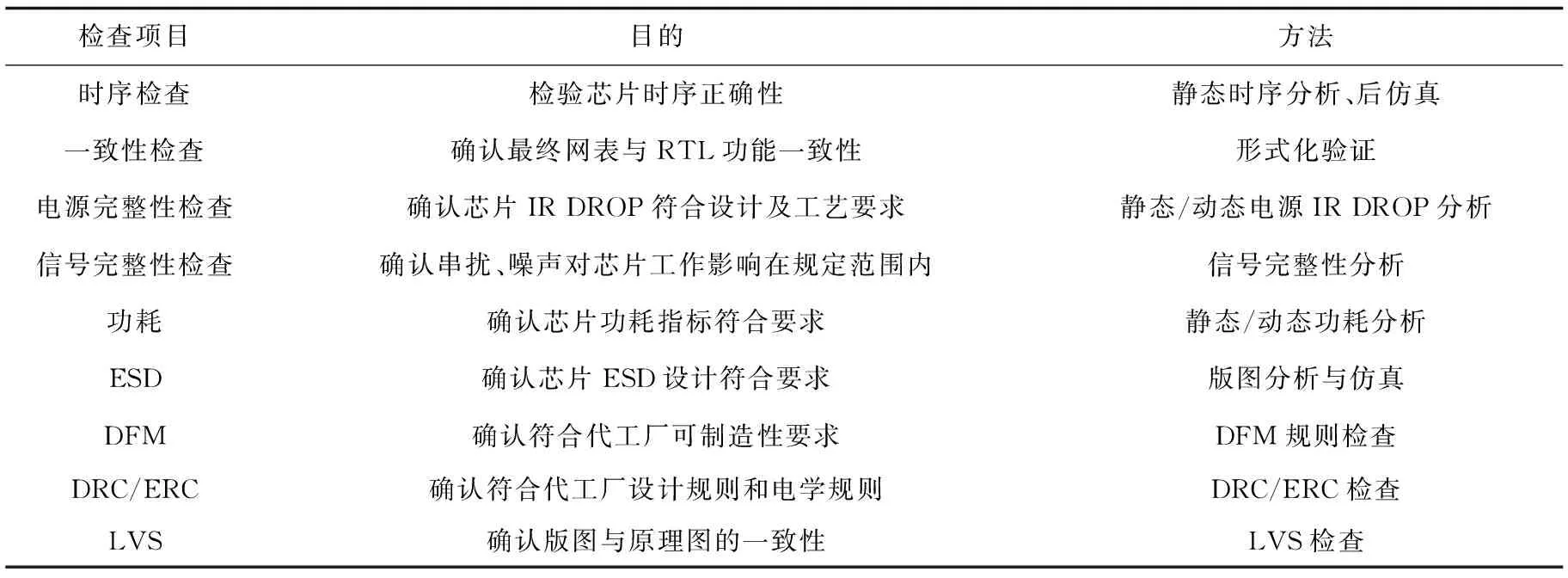

后端设计工程师可以根据前端设计的数据及约束要求完成后端设计工作[8-9],委托方只需要进行预定步骤的检查以确定后端设计与前端设计的一致性。传统的检查主要是设计规则检查(DRC)、电学规则检查(ERC)、版图与电路图一致性检查(LVS)。随着电路复杂度的提升和工艺尺寸的进一步缩小,在投片前Signoff时需要检查的内容也日益增多,包括时序分析与检查、功能一致性检查、电源及信号完整性检查、功耗分析与确认、ESD[10-11]及可靠性相关检查。具体检查项目与方法如表1所示。

1.2 集成电路制造工艺流程及关键工序控制

芯片制造与互联组成了微电子工业的高端谱线,在微电子工业中,性能和小型化保持着每18个月翻一番的发展速度,新材料和新工艺不断提高以满足工业性能和小型化目标。目前,集成电路的流片几乎都是采用代工方式完成。

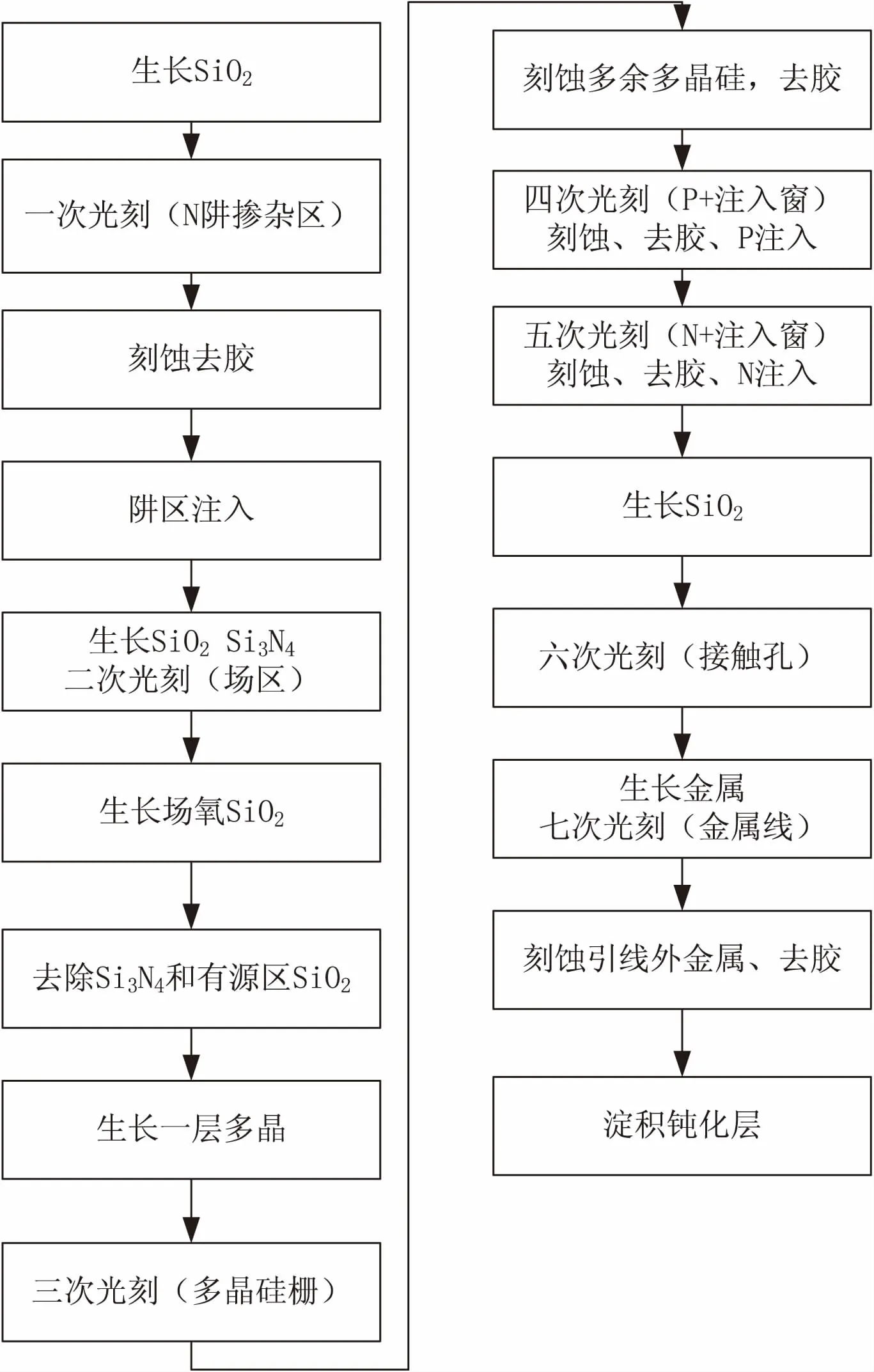

图2是典型的集成电路制造工艺流程示意图。

图2 典型的集成电路制造工艺流程

集成电路流片费用随着工艺的提高,价格也是成倍增加。例如,130 nm工艺工程批流片费用在200万左右,65 nm工艺工程批流片费用在400万左右,40 nm工艺工程批流片费用在800万元左右。如果流片成功,由于可产生管芯数量较多,单只管芯成本并不高,但是一旦流片失败,损失是非常大的。因此,如何保证流片不产生除设计缺陷以外的问题,保证芯片一

表1 集成电路后端检查项目

次投片成功至关重要。流片工序的检查依据是,按照GJB548B[12]方法5013 GaAs工艺的晶圆制造控制和接收程序通过对工艺检测图形和目检进行检查,工艺检测(PM)图形是一组为工艺控制和确定晶圆可接收性提供数据的测试结构,PM可以插入于每个晶圆的特定位置,位于划片槽位置,或包含在每个芯片中,也可以是这些方案的组合。建议的用于PM中的测试图形如表2所示。

表2 PM中的测试图形

晶圆接收要依据在制造过程中进行的PM室温测试所提供的信息,对每一个晶圆逐片检查。另外,在晶圆制造期间,应在关键工序进行光学显微镜或SEM检查,检查可以包括图形对准标记和临界尺寸测量。最终外包方应检查所有规定的PM电参数的测量和数据记录,必要时可以要求加工方提供除PM以外所有检查的或测试的结果,每批的接收、拒收晶圆数目,返工晶圆数目和返工原因等。

1.3 集成电路封装流程及关键工序控制

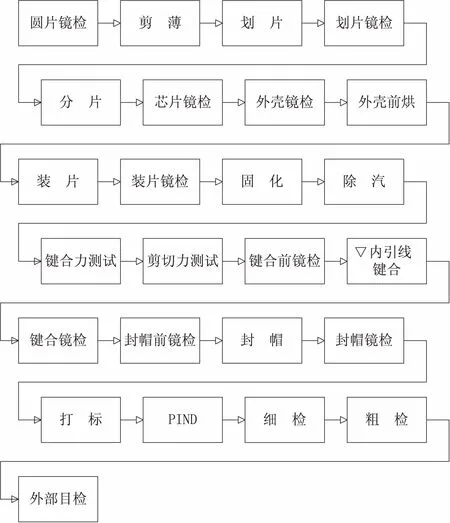

集成电路的封装目的是为芯片提供一个接口,将内部电性讯号通过引脚将芯片连接到系统,并避免硅芯片受外力与水、湿气、化学物的破坏与腐蚀,IC封装属于半导体产业的后段加工制程,主要是将前制程加工完成(即晶圆厂所生产)的晶圆上的IC予以分割,黏晶、打线并通过管壳实现对外部的链接。图3为IC芯片的封装流程。

集成电路封装作为一个专门的专业分支,具有非常复杂的流程及质量管控体系[13]。现有的军级电路基本都是陶瓷封装的,国内拥有军用集成电路封装贯标线资质的单位有两家:中电58所及航天772所。在贯标生产线上封装的产品,用户只需要检查封装工艺流程卡及生产线用于证明工艺一致性的首件产品的测试报告即可。划片、键合和封帽是芯片封装过程的关键工序,此三个步骤后的检查(芯片镜检、键合检查、气密性检查)应该在封装工艺流程卡里面留有实验记录及具体测量数据。

对于塑封电路,国内可以完成芯片塑封的单位有很多,如天水华天、航天771所、深南电路等等;但是由于工艺水平的限制,目前国内尚无军用塑封的贯标生产线。2011年,国内第一个指导塑封电路军品认证的文件GJB7400-2011(合格制造厂认证用半导体集成电路通用规范[14])正式颁布,但目前国内还没有企业通过认证。

图3 IC芯片的封装流程

2 结束语

集成电路的设计、实现、流片、封装、测试是一个非常复杂的系统工程,每一个环节都是一个专门的学科,而集成电路各环节环环相扣密不可分,任何一个环节出现问题都可能导致流片的失败,因此如何保证每一个流程的正确性是每一个集成电路设计单位都面临的难题。文中总结了集成电路后端设计、流片、封装工艺流程及关键工艺检查流程,从而尽量减少外协合作环节中可能引入的各类问题,提高一次流片成功率。

[1]FurberS.ARMSystem-on-ChipArchitecture(ARMSoC体系结构)[M].田 泽,于敦山,译.台北:五南图书出版公司,2003.

[2] 田 泽.航空专用集成电路-设计理论与工程实践[M].北京:航空工业出版社,2013.

[3] 田 泽.SoC设计与测试[M].北京:航空工业出版社,2003.

[4] 科兹纳.项目管理[M].北京:电子工业出版社,2006.

[5] 项目管理协会.Projectmanagementinstitute[M].北京:电子工业出版社,2009.

[6] 刘 锐,姚世锋.半导体集成电路芯片质量与可靠性保证方法[J].兵工自动化,2013,32(6):17-19.

[7] 杨建生,李守平.对集成电路封测项目进度、投资与质量控制管理的探讨[J].电子工业专用设备,2015(1):1-4.

[8] 罗志华,权进国,杨华中.基于层次法实现EOS芯片的后端设计[J].微计算机信息,2008,24(14):5-7.

[9]HodgesDA,JacksonHG,SalehRA.Analysisanddesignofdigitalintegratedcircuitsindeepsubmicrontechnology[M].[s.l.]:[s.n.],2005.

[10] 蒋玉贺,王 爽.CMOS集成电路ESD设计[J].微处理机,2008,29(3):19-21.

[11]KerKD,ChenTY,WuCY.ESDprotectiondesignonanalogpinwithverylowinputcapacitanceforhigh-frequencycurrent-modeapplication[J].IEEESolid-StateCircuits,2000,35(8):1194-1199.

[12] 陈裕焜,贾新章,张德胜,等.微电子器件试验方法和程序[S].北京:总装备部军标出版发行部,2005.

[13] 韩忠华,王长涛,马 斌,等.半导体封装生产线工艺流程分析[J].科技广场,2010(8):147-149.

[14] 李 锟,陈裕焜,秦国林,等.合格制造厂认证用半导体集成电路通用规范[S].北京:总装备部军标出版发行部,2011.

Critical Outsource Procedure Control for Military VLSI

ZHANG Ling1,2,TIAN Ze1,2

(1.AVIC Computing Technique Research Institute,Xi’an 710068,China;2.Key Laboratory of Aviation Science and Technology on Integrated Circuit and Micro-system Design,Xi’an 710068,China)

With the rapid advance and development of semiconductor technology,the division of labor has become more and more elaborate.The back-end design,chip processing,packaging and test has already developed into special areas.Integrated circuit design,processing and other steps are tied closely to each other,problems in any part of the whole procedure may lead to a chip tape-out failure.Therefore,how to ensure the correctness of every aspect of the whole procedure is always an important problem for every IC designer,especially for the problem of how to control the outsourcing procedure.Based on analysis of the process of back-end design,fabrication and packaging for military VLSI,it summarizes the key procedures and control methods of the back-end design,fabrication and packaging and checking in this paper,which is meaningful for the quality control of military VLSI outsourcing design.

back-end design;fabrication;packaging;key procedure control

2014-10-13

2015-01-05

时间:2016-05-05

中国航空工业集团公司创新基金(2010BD63111)

张 玲(1982-),女,硕士,研究方向为项目管理;田 泽,博士,研究员,中国航空工业集团首席技术专家,研究方向为SoC设计、嵌入式系统设计、VLSI设计等。

http://www.cnki.net/kcms/detail/61.1450.TP.20160505.0814.012.html

TP39

A

1673-629X(2016)05-0170-03

10.3969/j.issn.1673-629X.2016.05.037