基于PowerPC架构的通用处理器系统虚拟验证

王 婷,马 超,田 泽

(1.中国航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点试验室,陕西 西安 710068)

基于PowerPC架构的通用处理器系统虚拟验证

王 婷1,2,马 超1,2,田 泽1,2

(1.中国航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点试验室,陕西 西安 710068)

基于PowerPC架构通用处理器系统在全球军用/宇航微处理器等长寿命、高可靠领域应用非常广泛,与此同时其规模和复杂度之大给设计和验证带来了巨大挑战。文中基于一款PowerPC架构的通用处理器系统,构建软硬件协同工作的虚拟验证平台,开发验证模型和测试程序,并采用模块级到系统级的分层验证策略。验证结果表明,基于PowerPC架构通用处理器系统虚拟验证能够有效地进行系统的功能和性能验证,提高了验证效率,缩短了设计中的查错纠错时间,从而降低风险,加快设计、验证进度。

PPC通用处理器;验证平台;验证模型;虚拟仿真

0 引 言

PowerPC架构通用处理器系统在多媒体、计算机、汽车等领域及卫星、军用飞机、弹道发射系统、舰船和海军设备等军用领域有非常广泛的应用[1-3]。考虑到通用处理器系统的规模和设计复杂度之大,保证其通用性和灵活性的同时兼顾处理效率,大多采用软硬件协同设计的方法,在设计难度增大的情况下,进行行之有效的仿真验证工作也变得至关重要[4-5]。

文中基于一款PowerPC架构的通用处理器系统,通过搭建虚拟验证平台模拟其工作过程,采用模块级到系统级的分层验证策略,能够有效进行系统的功能和性能验证,缩短设计中的查错纠错时间,从而降低风险,加快设计和验证进度。

1 PowerPC架构通用处理器系统解决方案

文中的PowerPC架构通用处理器系统是一款以PowerPC处理器为核心,集成浮点处理单元、二级Cache,对外提供SDRAM存储器接口、以太网接口和PCI接口,并提供UART、GPIO、I2C、EBC等丰富外设接口的高性能、低功耗处理器系统,如图1所示。

图1 处理器系统结构框图

高带宽、低延迟的处理器局部总线PLB负责连接高性能的外围设备[6-7],如DMA控制器、片上存储等。片上外设总线OPB则用来连接低速外围设备,如看门狗、实时时钟等。PLB总线与OPB总线之间用PLB-OPB的桥接器连接,以减轻PLB总线的负荷。设备控制寄存器总线DCR把所有连接在PLB和OPB上的模块用雏菊链的方式进行互连,通过它来对所有设备的控制寄存器进行操作,以减少零碎的寄存器访问对PLB和OPB总线带宽的占用。二级Cache用于提升PPC处理器的处理性能,节省PLB访问带宽,增加PLB总线上的其他主设备可访问总线带宽。浮点处理单元与PPC处理器核配合使用,包含可并行执行的五级算术流水线和四级存储加载流水线。

2 验证平台搭建

虚拟验证平台具有精确、便于调试的特点。文中依照PowerPC架构通用处理器系统的功能、性能需求,提取功能点,搭建验证平台,实施验证。

2.1 验证环境

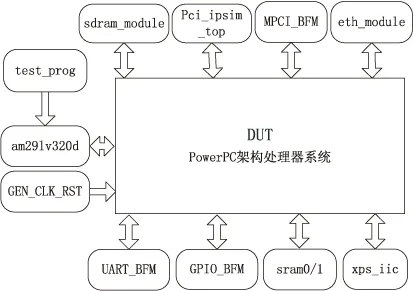

基于PowerPC架构的通用处理器系统的虚拟验证平台如图2所示。采用软硬件协同验证方法,开发相应的验证模型和测试程序。

2.2 验证模型

PowerPC架构通用处理器系统验证模型挂接在系统的对应外接口上模拟处理器实际工作时的周边元件,验证模型及说明见表1。

图2 虚拟验证平台

组件作用GEN_CLK_RST产生系统所用时钟am29lv320d连接EBC的外部flash模型,存储Boot程序sdram_module外部SDRAM模型MPCI_BFMPCIHost模型,支持故障注入;PCIMonitor检查协议一致性Pci_ipsim_topPCIAgent模型eth_module接收系统发出来的帧,并转发回去;构造超长和超短帧,测试系统中以太网模块对超长超短帧的处理UART_BFM接收及产生串行数据GPIO_BFM驱动输入,监控输出sram0/1EBC存储器接口的外部SRAM模型xps_iic作为I2C总线上的主从设备,发送和接收数据

2.3 测试程序

测试程序的通用功能主要包括定义入口地址、建立异常中断处理向量、初始化外部存储器、初始化堆栈指针、初始化I/O设备、初始化C程序需要的存储空间,以及进入C语言程序运行等[8]。程序跳转到C程序的入口函数main(),main()函数是验证程序的顶层,它初始化所有全局变量,调用各个测试模块并报告总体测试结果。

软件应用工程包含五类源文件:.c源代码、.h头文件、.ld连接脚本文件、.s汇编文件以及makefile文件。其中:.c源代码是.c文件用户源程序,基于标准的C语言,是应用程序的主要部分,用户根据验证策划及验证规范编写相关代码;.h头文件是用户编写的头文件;.ld连接脚本文件用于连接用户源代码,指定生成的目标二进制文件保存具体的段信息;.s汇编文件用于设置处理器核的指令数据缓存、处理中断等操作,一般用于初始化和BootLoop应用中;makefile文件用户对软件代码的编译进行配置,确定所使用的编译器、连接器等信息,完成软件代码的编译,并最终生成用于仿真的.v文件。

2.4 工作流程

虚拟仿真的工作流程一般为:首先编写C语言测试程序,经过编译链接后,把程序转化成处理器能识别的二进制文件,输入到片外存储器模型中,由处理器读取并执行指令来控制整个平台的运作[9];同时,由外设和接口对应的模型模拟外部输入,和片上处理器程序的运行相结合,进行虚拟仿真工作。虚拟仿真结果的正确性,可以通过处理器系统的程序进行判断,或者通过外部模型判断。

3 验证策划

虚拟验证平台通过模拟待测系统工作过程,验证集成后模块功能、模块互连,以及整体功能、性能是否满足设计需求,重点关注各个模块在互连之后彼此之间的互操作性、数据流控制和一些简单的应用操作。

虚拟平台的验证主要包括两大方面[10-11]。一方面是系统集成后的模块级验证,即模块寄存器写读操作、相对独立的功能、模块对外I/O功能、边界条件、设计间的断点、错误条件及异常情况处理的验证;另一方面是集成后的系统功能验证,包括时钟复位功能、功耗管理、地址空洞、各数据通路互连关系、数据通路上的存储器映射关系等系统整体功能和性能的验证。

各模块的功能重点在IP级进行验证[12],系统集成后对IP级验证项进行相应的删减以及移植修改进行系统集成后的模块级验证,这里不再一一赘述。特别指出的是,PPC处理器作为整个系统的核心中枢,在系统集成后的模块级验证中对其进行了全面的验证,包括复位功能、指令或数据Cache的控制和管理功能,内存管理单元的读写访问控制,各类中断的功能验证,计时器功能验证,指令集功能验证等。

虚拟平台系统功能验证包括五类[13-14],分别是时钟复位功能、功耗管理功能、地址空洞验证、数据通路验证以及数据存储及传输性能验证。

(1)时钟复位功能验证中时钟频率配置验证即不同主时钟频率下的各PLL锁相环的配置及输出;复位功能验证包括系统上电复位功能、外部复位输入功能、软件复位功能、调试复位功能和看门狗复位功能的验证。

(2)功耗管理功能验证了通过配置寄存器实现模块的休眠控制。

(3)地址空洞包括了PLB总线和DCR总线访问地址空洞的功能验证。

(4)数据通路验证分别是以太网通路和PCI通路的验证。以太网的发送和接收通路,涉及PPC处理器、以太网接口、SDRAM存储器接口、片内SRAM控制器、EBC存储器接口、DMA控制器等模块;PCI通路的验证分别是处理器访问外部PCI从设备通路验证和PCI主设备访问PLB端地址通路验证,涉及PPC处理器、PCI主机接口、SDRAM存储器接口、片内SRAM控制器、EBC存储器接口、DMA控制器等模块。

(5)数据存储及传输性能验证以通用嵌入式处理器的主要性能参考指标(如整型运算能力、浮点运算能力等)作为评判基准,验证包括CPU整型运算性能、浮点运算性能、PCI接口性能、SDRAM接口性能、以太网接口数据传输能力及以太网数据协议解析传输能力测试。

4 验证结果

通过文中设计的验证平台及策略的验证,PowerPC架构通用处理器系统功能正确,在处理器时钟250 MHz,SDRAM频率为100 MHz时,SDRAM读写效率分别为167.8 Mbps和362 Mbps,PCI频率66 MHz时PCI读写效率分别为35.7 Mbps和221.7 Mbps,处理器系统性能为1.58 DMIPS/MHz,浮点运算性能为1.35 DMIPS/MHz。

5 结束语

文中在对一款PowerPC架构通用处理器系统进行功能分析和特性提取的基础上,详细介绍了基于软硬件协同工作的虚拟验证平台的搭建及工作流程,并描述了模块级和系统级的分层验证策略及验证重点。该虚拟验证系统能够有效地进行处理器系统的功能和性能验证,加快设计和验证进度,并且进行简单的修改移植便可以进行同类型系统的虚拟验证工作,具有可移植性。

[1] 陈 帅,张斌峰,王旭东.基于PowerPC的处理器模块研究及故障分析[J].大众科技,2014,16(4):35-37.

[2] 尚何章,李春涛.基于Power PC的小型无人机飞行控制系统设计[J].伺服控制,2012(4):50-52.

[3] Lam W K,Microsystems S.Hardware design verification:simulation and formal method-based approaches[M].[s.l.]:Prentice Hall PTR Publisher,2005.

[4] 吴晓成,田 泽,郭 蒙,等.AFDX交换芯片虚拟验证关键技术研究[J].计算机技术与发展,2013,23(8):177-180.

[5] 申 敏,曹聪玲.基于SoC设计的软硬件协同验证技术研究[J].电子测试,2009(3):9-12.

[6] Wolberg G.Digital image warping[M].Los Alamitos Califor-nia:IEEE Computer Society Press,1990:208-209.

[7] Wolf W.High performance embedded computing architectures,applications,and methodologies[M].New York:Elsevier,2007.

[8] Sefraoui O,Aissaoui M,Eleuldj M.Open stack:toward an open-source solution for cloud computing[J].International Journal of Computer Application,2012,55(3):38-42.

[9] 郭 蒙,田 泽,蔡叶芳,等.1553B总线接口SoC验证平台的实现[J].航空计算技术,2008,38(6):99-101.

[10] 一个成功的百万门级芯片验证平台[J].中国集成电路,2005(6):36-43.

[11] 吴英攀,于立新,薛 可,等.基于层次化验证平台的存储器的控制器功能验证[J].微电子学与计算机,2009,26(2):25-28.

[12] 杨海波,田 泽,蔡叶芳,等.FC IP软核的仿真与验证[J].计算机技术与发展,2009,19(9):168-172.

[13] 韩 霞,杨洪斌,吴 悦.面向SoC的事务级验证研究[J].计算机技术与发展,2007,17(3):33-36.

[14] 田 靖,田 泽.AFDX-ES SoC虚拟仿真平台的构建与应用[J].计算机技术与发展,2010,20(8):192-194.

Virtual Verification of General Processor System Based on PowerPC Architecture

WANG Ting1,2,MA Chao1,2,TIAN Ze1,2

(1.Aeronautics Computing Technique Research Institute,Xi’an 710068,China; 2.Key Lab of Aeronautics Science and Technology of Integrate Circuit and Micro-system Design, Xi’an 710068,China)

The general processor system based on PowerPC architecture is outstanding in the military/astronautics microprocessor field with longer life and higher reliability.At the same time,with the increasing of the transistor number and the complexity,the design and verification has been brought huge challenge.Based on the general processor system based on PowerPC architecture,the hardware/software co-design virtual verification testbench is proposed,and verifying model and testcase is developed,and the verification method from module to system is adopted.The simulation results show that the virtual verification for general processor system based on PowerPC architecture can conduct the verification of function and performance,which improves the efficiency and reduces the time of error correction in design,to reduce the risk and increase the degree of design and verification.

PPC general processor;testbench;verifying model;virtual simulation

2015-06-16

2015-09-22

时间:2016-03-22

中国航空工业集团创新基金(2010BD63111)

王 婷(1985-),女,工程师,研究方向为集成电路设计与验证;田 泽,博士,研究员,中航首席技术专家,研究方向为SoC设计、嵌入式系统设计、VLSI设计。

http://www.cnki.net/kcms/detail/61.1450.TP.20160322.1517.006.html

TP39

A

1673-629X(2016)04-0136-03

10.3969/j.issn.1673-629X.2016.04.030