基于CPLD的高响应高精度伺服系统位置信息实时采集系统设计与实现

基于CPLD的高响应高精度伺服系统位置信息实时采集系统设计与实现*

虞志源1,鲁文其1,2,顾小卫1,2,袁嫣红1,张建亚1,胡东轩1

(1. 浙江理工大学,浙江 杭州310018; 2. 浙江大学,浙江 杭州310018)

摘要:阐述了绝对式光电编码器的工作原理,设计了一套基于17bit串行编码器的位置检测方案,给出了串行编码器位置检测方式的硬件框图。按照功能将CPLD代码分成4个模块,并对各个模块的设计原理进行了详细的阐述。搭建了试验平台进行了位置读取的试验测试。由试验结果知,此方案能很好地读取位置信息,且精度很高,适用于高响应高精度的伺服系统。

关键词:交流伺服系统; 串行编码器; 位置检测; 高响应高精度

基金项目:* 国家自然科学

通讯作者:虞志源

中图分类号:TM 383.4文献标志码: A

收稿日期:2015-03-17

Location Information Acquisition in Real Time System’s Design and Application

in High Response and High Precision Servo System Based on CPLD

YUZhiyuan1,LUWenqi1,2,GUXiaowei1,2,YUANYanhong1,ZHANGJianya1,HUDongxuan1

(1. Zhejiang Sci-tech University, Hangzhou 310018, China;

2. Zhejiang University, Hangzhou 310018, China)

Abstract:The study expounded absolute photoelectric encoder’s principle, designed a set of position detection scheme based on 17 bits serial encoder, and presented serial encoder position detection method’s hardware block diagram. The system divided the CPLD code into four modules according to function, and expounded the of each module’s design principle in detail. At last, we set up the experimental platform to read the position information. According to the experiment, the solution can read the location information with high precision. It is suitable for high response and high precision servo system.

Key words: AC servo system; serial encoder; position detection; high response and high precision

0引言

目前,伺服系统被广泛应用于工业、民用、军工等各种领域。它能快速、精确地跟踪输入信号,还能实现对被控对象的位置、速度、转矩的精确控制[1]。想要很好地实现对位置、速度、转矩的闭环控制,必须先实现对转子位置的精确检测。因此,整个系统的精度往往受转子位置检测精度的影响或制约[2,3]。

永磁交流伺服系统中,编码器根据其输出信号是数字量还是模拟量,可以分为数字量编码器和模拟量编码器。常见的绝对式光电编码器和增量式编码器就是数字编码器,而模拟量编码器则有旋转变压器和正余弦编码器[4]。2500线编码器是国内较为常用的增量式编码器,但是该编码器只有11bit的分辨率,精度完全不能满足高性能高精度的伺服系统,旋转变压器解码之后的位置信息分辨率可达到16bit,精度相对于2500线编码器已经有了很大的提高,能较好地应用于一般的大功率高精度场所[5]。美中不足的是,旋转变压器虽然属于绝对式编码器,但是其以模拟量的方式输出位置信息,必须进行复杂的解码[6,7]。与旋转变压器相比,17bit光电编码器精度更是高达17bit,而高响应高精度的伺服系统对位置检测精度的要求相当高,因此本研究选用17bit光电编码器作为反馈位置信息的元件,并做了位置检测相关的各种试验。

1位置检测方案设计

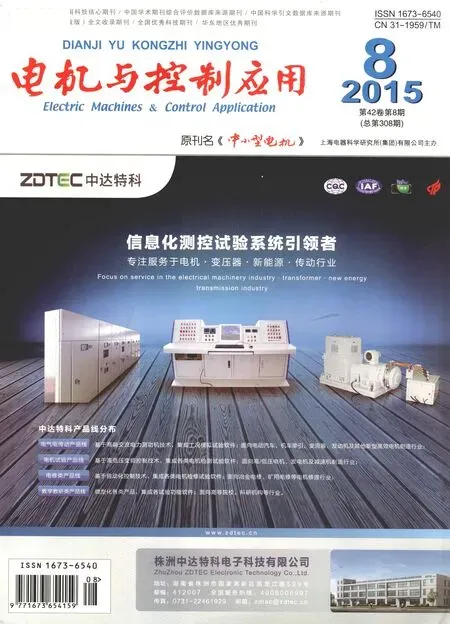

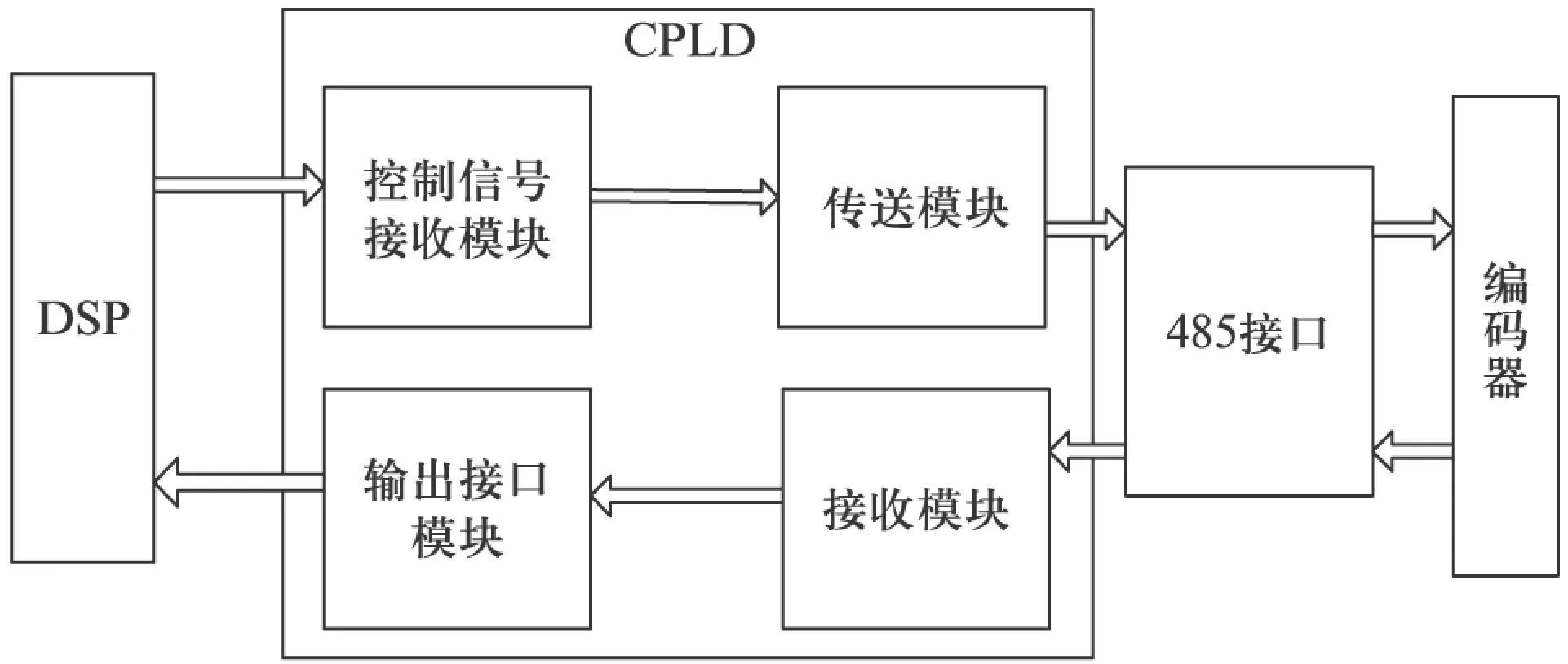

对于编码器返回的数据,可以用解码芯片进行解码,但是解码芯片的价格较为昂贵,不利于成本的控制。另外一种办法就是通过编程来实现返回数据解码[8,9]。本文利用CPLD强大的逻辑处理功能,采用VHDL语言编程来实现编码器返回数据解码的方案。具体的方案如图1所示。

图1 位置检测方案流程图

DSP发送控制指令给CPLD,CPLD对控制指令进行译码,得到的数据通过485接口发送给编码器,编码器收到控制指令后再延迟3μs之后返回位置数据信息,同样是经过485接口,传给CPLD,CPLD经过解码并且把数据存储在不同的位置供DSP读取。

2光电编码器原理

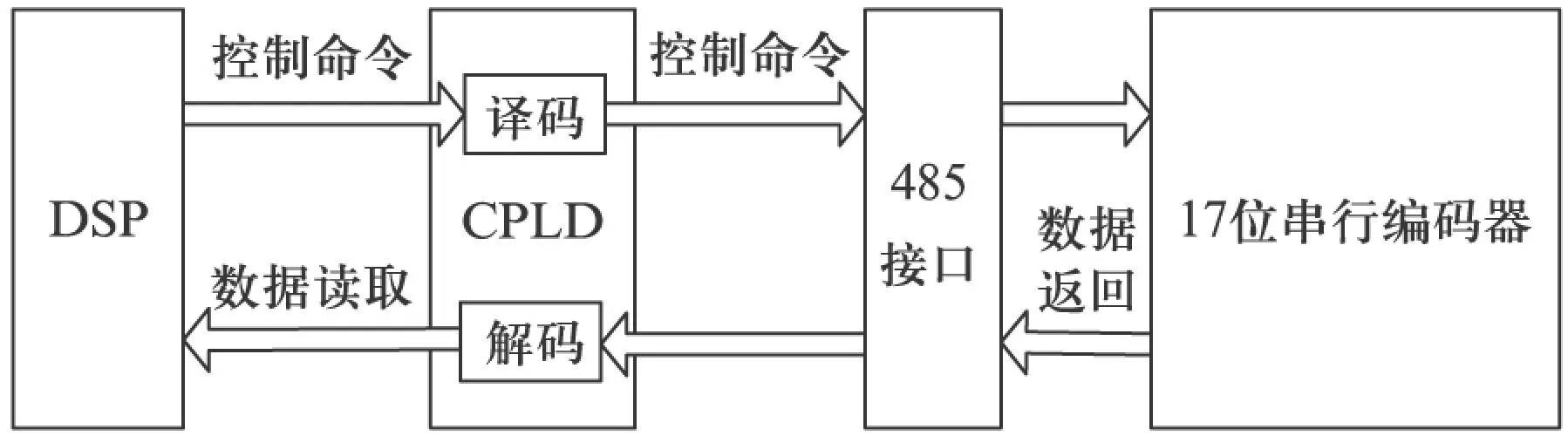

图2 码盘俯视图

绝对式光电编码器可直接输出转子绝对位置角度数字量,在它的圆形码盘上有若干码道,每个码道从里到外依次分为1、2、4、8……个区域,并黑白相间,如图2所示。绝对式光电编码器的码盘上有很多码道,而码盘上的码道数就是其二进制数码的位数,也就是其分辨率的位数,17bit编码器拥有17个码道(图2中所示是一个拥有4码道的编码器),每个码道上从里到到外依次分为1、2、4……个区域。在码盘的两侧分别是光源和吸光元件,当码盘处于不同位置时,各吸光元件便能根据有无接收到光线来决定转子位置的数值。

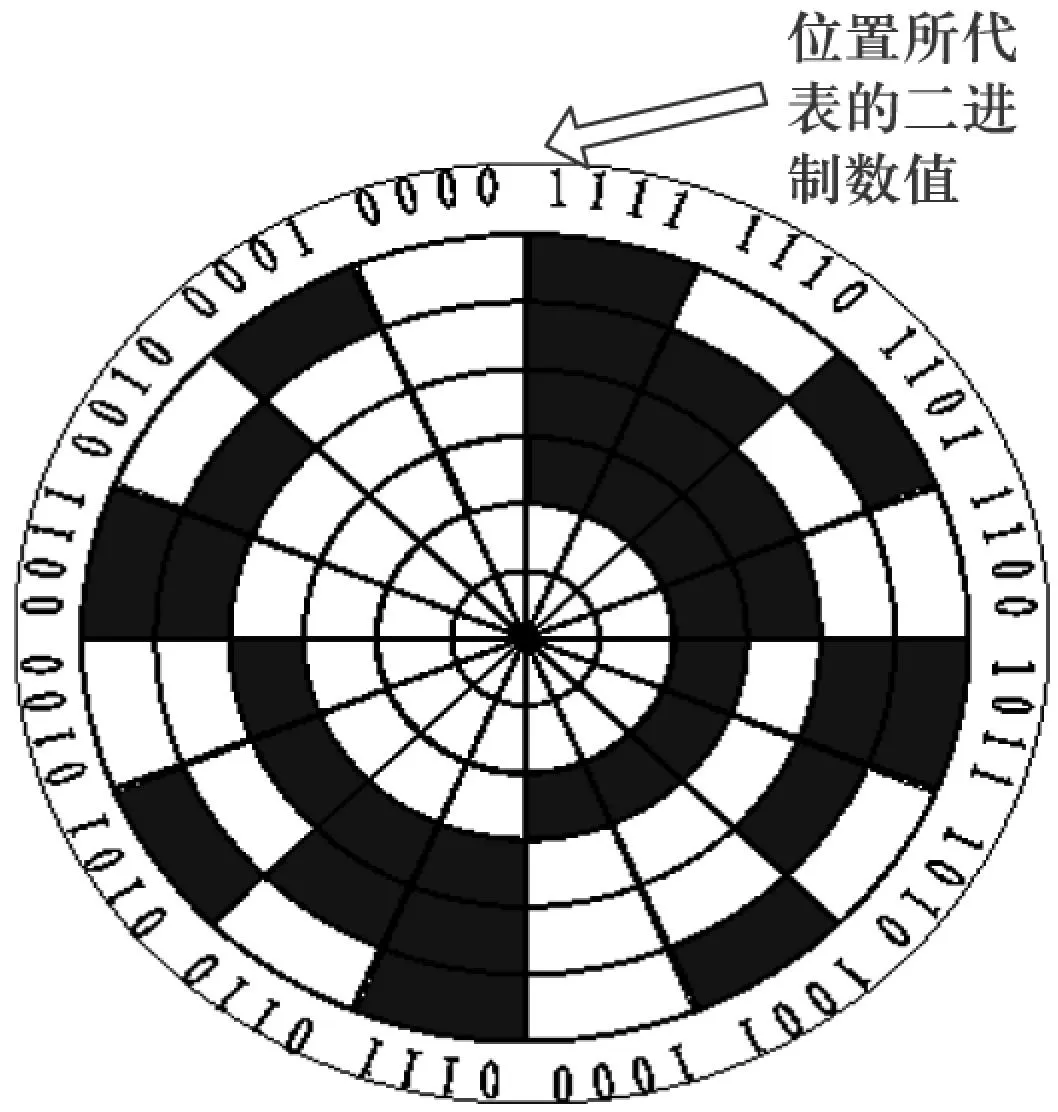

3位置检测硬件设计

位置检测硬件设计框图如图3所示。DRCNT信号能确定CPLD传输方向。CPLD通过RQ传输控制信号,通过SD接受数据信号。DSP通过片选地址A0~A5、CS_ZONE0、WE向CPLD传送控制指令,CPLD对其进行译码并通过RQ,经485接口传输给编码器。接收到控制指令后的编码器在经过3μs之后,返回所需要的数据,经485接口,并通过SD传回给CPLD,经CPLD解码,然后把相应的数据存储在对应的地址中。DSP可以通过切换地址来读取需要的不同数据。

图3 位置检测硬件设计框图

CPLD作为17位串行编码器与DSP之间的接口,其与编码器之间的通信采用485接口通信。由于485接口是差分形式传输的,能有效抑制干扰。

4位置检测软件设计

DSP发送控制指令,CPLD作为DSP的外部接口对指令进行译码,然后传送给编码器,控制编码器返回位置数据,再经由CPLD进行解码,由DSP读取需要的信息。控制信号接收模块、传送模块、接收模块以及输出接口模块构成了整个CPLD。位置检测软件设计框图如图4所示。

图4 位置检测软件设计框图

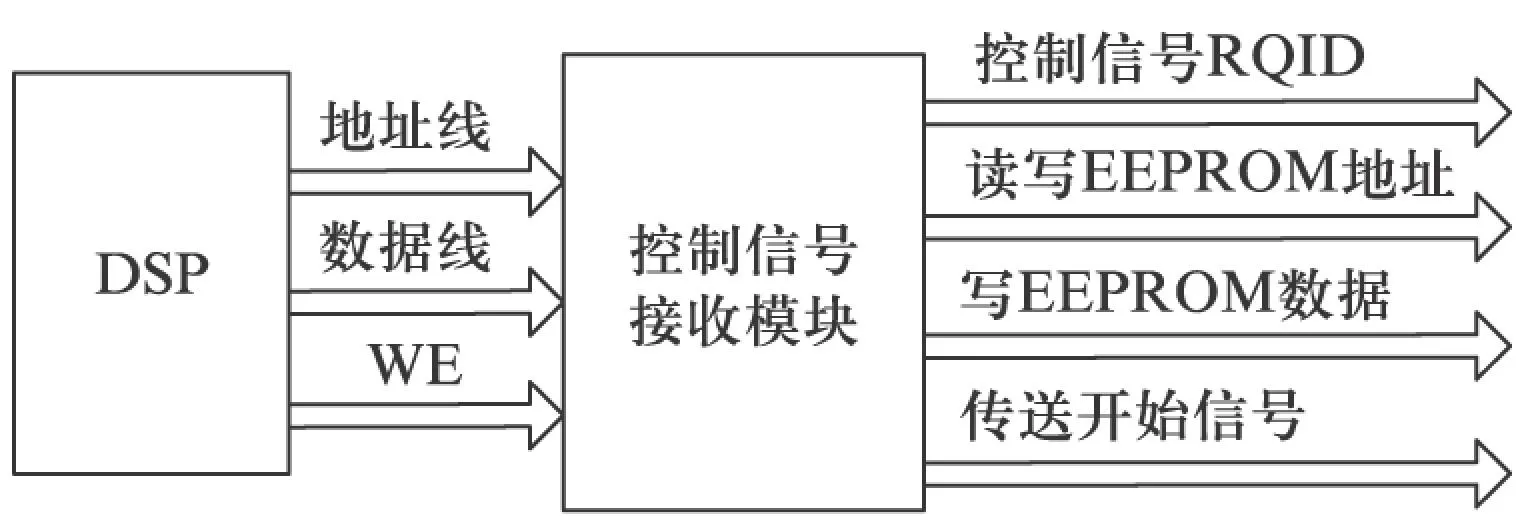

4.1控制信号接收模块

控制信号接收模块框图如图5所示。接收模块主要是CPLD用来接受DSP传输过来的控制命令,且对控制信号进行整理,并将最后整理完毕的控制信号传输给传送模块。

图5 控制信号接收模块

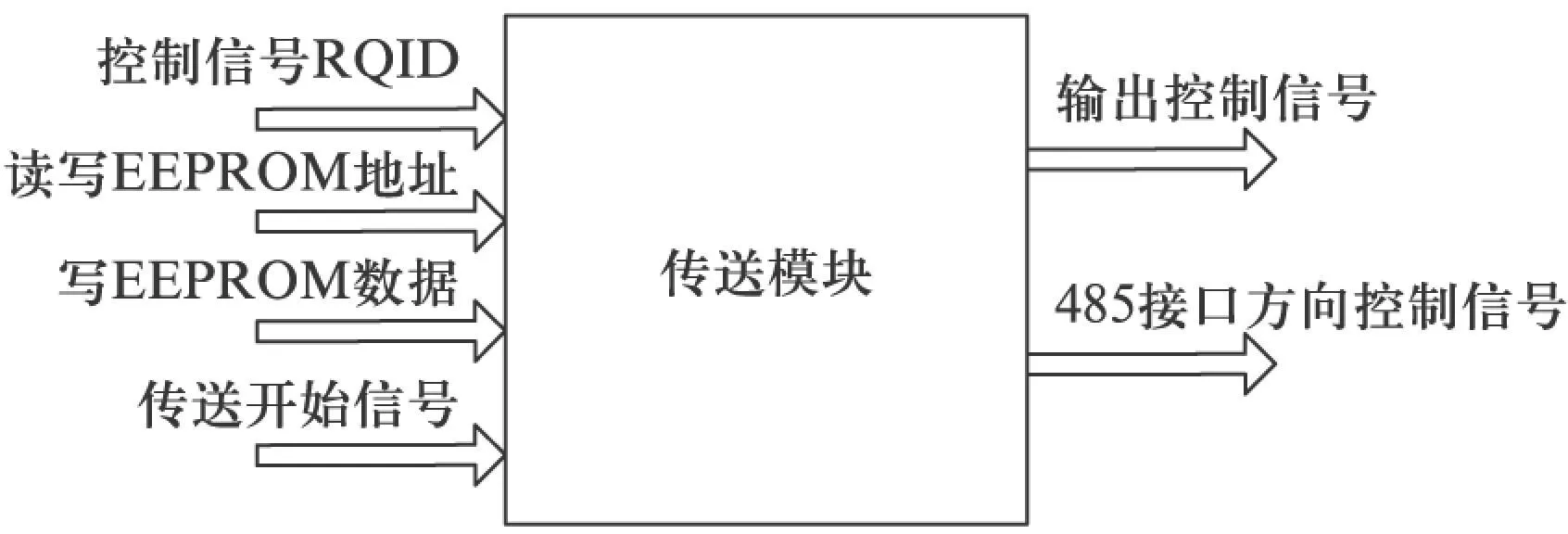

4.2传送模块

传送模块框图如图6所示。控制信号接收模块的控制信号传输给传送模块之后,传送模块负责产生串行输出控制信号和485接口传输方向控制信号。串行输出控制信号分为3种情况: (1) 读取编码器模式,这种模式下只需要传送一个控制帧;(2) 读EEPROM模式,该模式下需要控制帧、地址帧和CRC帧;(3) 写EEPROM模式,需要地址帧和数据帧还有CRC帧。不管什么模式下,这些数据分别被存储在不同的寄存器中,由DSP切换地址来读取或者不读取。

图6 传送模块

4.3接收模块

接收模块框图如图7所示,编码器传回的数据(位置或者速度信息等)由接收模块来接收,并与各个帧成相应的数据帧。若在读取编码器模式下,数据帧的格式应为控制帧(CF)+数据帧(Dn0~Dn7)+CRC帧的格式;若在读写EEPROM的模式下,数据帧的格式应为控制帧(CF)+地址帧(ADF)+数据帧(EDF)+CRC帧的格式[5],在数据接受并且转化完成之后,还需要对数据进行校验,包括停止位校验、起始位校验、CRC校验、奇偶校验,一旦所有的校验位都为0,就代表整个过程没有错误,可把整理好的数据帧传送到下面所描述的输出接口模块。

图7 接收模块

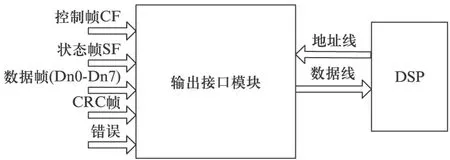

4.4输出接口模块

输出模块框图如图8所示,编码器返回的数据在接收模块中重组之后传输给输出接口模块,然后存储在CPLD不同的地址之中,来供DSP读取。因此通过选用不同的外部接口的地址能方便地选择需要的数据。

图8 输出接口模块

4.5分频模块

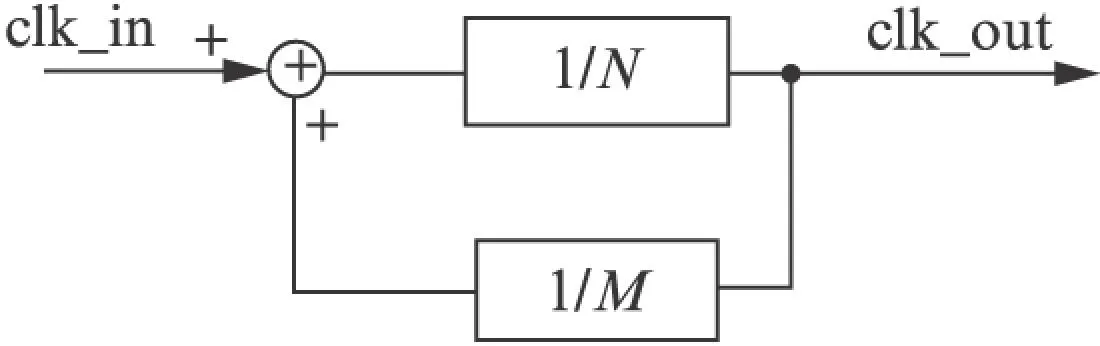

分频器原理如图9所示。由于CPLD工作的频率为75MHz,绝对式编码器则为20MHz,75MHz转化到20MHz需要3.75倍的分频,参考文献[10]提出由D触发器级联的小数分频方法,输出的两种占空比波形的分布比较均匀,故分频模块采用D触发器级联。

图9 分频器原理图

由图9可知,此框图的传递函数为

(1)

分频倍数为3.75倍,由式(1)可计算得到M=N=4,也就是说,前向通道与反馈通道都需要4分频才能达到预期的3.75倍分频。由文献[10]可知,一个D触发器电路为一次2分频,因此前向通道和反馈通道都需要2个D触发器电路。

5试验与测试

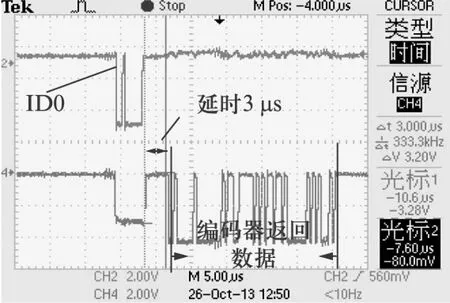

本文使用的编码器为日本多摩川TS5667N2300,由CPLD向编码器发出控制码,得到编码器返回的串行数据码的波形。其试验结果如图10、图11所示。

图10 发送ID0返回数据

图11 发送ID3返回数据

总共进行了两次试验。图10、图11中控制字ID码依次为0和3,ID0控制帧应该是“0010000001”,ID3控制帧应该是“0010110001”。图10中DSP发送控制命令给CPLD之后,CPLD将控制命令译码之后将控制码传输给编码器,其传输波形是“0010000001”,图11中则为“0010110001”。编码器在3μs之后返回数据,再观察返回的数据波形。由编码器协议可知,返回的数据格式为控制帧+状态帧+数据帧+CRC帧的形式。可以看出图10编码器返回的前面10位为“0010000001”,紧接着的状态帧为“0000000001”,也就是说此次通信编码器返回数据无误、有效,紧接着便是数据帧和CRC帧。图11也是一样,只是控制帧不同而已。

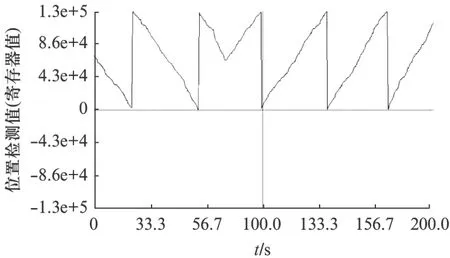

17位串行编码器的精度为17bit,即把一圈的位置分为131072(217)个部分,每个部分算是一个位置,也就是说,每0.00275°(360°/131072)算作一个位置,且都有与之对应的二进制码数字量,精度非常之高。位置检测中DSP所读取的位置信息如图12所示,横坐标为时间,纵坐标为角度寄存器中存储的位置数值。可以看出,角度寄存器中最大的数值(131072-1),当顺时针旋转编码器时,位置信息从(131072-1)(位置信息数字量最大值)减小到0,然后跳变到(131072-1),依次循环,逆时针则是相反。试验所得精度符合17bit串行编码器的理论精度。

图12 位置检测波形

6结语

本文设计了一种伺服系统的高精度位置检测方案,方案通过对CPLD进行编程,从而实现对DSP控制指令的译码与对编码器返回的位置数据的解码。给出了位置检测硬件原理框图。采用模块化的设计思想,搭建试验平台对位置检测进行了试验测试。17bit串行编码器具有高达17bit的精度,从返回一次数据的时间计算、位置波形及位置精度计算都能看出,该方案能很好地实现高响应高精度的位置检测。

【参考文献】

[1]肖涛.伺服系统的高精度位置检测[D].武汉: 华中科技大学,2012.

[2]付海军,李小艳.绝对式编码器的应用[J].微电机,2013(6): 91-93.

[3]程晓莉,谢剑英,王林.绝对式编码器在电机定位中的应用[J].控制工程,2007(5): 548-550.

[4]彭雨.基于FPGA的绝对式光电编码器通信接口研究[D].武汉: 华中科技大学,2008.

[5]霍海龙.基于BISS协议的编码器及其在伺服驱动系统中的应用[J].电气自动化,2011(3): 12-14.

[6]鲁文其,胡育文,金海,等.永磁同步电机重载驱动的曲柄伺服压力机动力系统参数[J].电工技术学报,2014,29(1): 91-97.

[7]鲁文其,胡旭东,史伟民,等,基于扰动补偿算法的拉床主溜板双伺服同步驱动控制策略[J].机械工程学报,2013,49(21): 31-37.

[8]谢智.基于TMS320F28035的伺服系统多功能位置接口模块研究[D].杭州: 浙江大学,2006.

[9]王烈虎.高精度数控伺服驱动检测及接口与位置直接闭环控制研究[J].电气自动化,2011(3): 12-14.

[10]尹辉炳,张涛.基于VHDL的全数字分数分频器设计[J].科学技术与工程,2006(12): 1609-1611.