基于EDAC的低开销星载迫零检测算法

高 山,王大鸣

(信息工程大学 通信与信息系统工程学院,河南 郑州450002)

0 引 言

MIMO 作为LTE通信体制的核心技术之一,能够提高频谱利用率,增大系统容量[1,2]。然而MIMO 检测算法需要大量资源,星上资源却十分有限,并且星载平台都采用TMR (triple modular redundancy)冗余设计,会使资源占用率增加两倍以上。因此必须结合星载平台应用场景的特殊性,对其所承载相关算法的设计在考虑抗SEU 的同时须降低其资源占用率。

目前星载平台算法层面上的抗单粒子翻转设计主要有ABFT[3](algorithmic-based fault tolerance)和RPR[4](reduced-precision redundancy)。ABFT 设 计 在 矩 阵 阶 小 于3时,其芯片资源占用率大大高于TMR 设计,且增加了处理时延。RPR 设计降低了资源占用率,有良好的抗辐射性能,但会降低数据精度。硬件层面上抗SEU (signal event upsets)的方法主要有擦洗、冗余、纠错编码、纠错电路、动态重构等,其中应用最为广泛、有效的是硬件TMR 容错技 术[5,6],该 设 计 可 以 检 测 和 纠 正 错 误,但 资 源 占用率高。

针对基于TMR 架构的ZF检测算法资源开销大、功耗大的问题,本文在二维内存EDAC 抗单粒子翻转方法基础上,提出一种抗SEU 的星载检错纠错 (EDAC)迫零检测算法。该算法通过在矩阵乘积运算中扩展加入两行 (列)“校验和”,实现了自检错、自纠错功能,可以同时检测一位错误和纠正一位错误,以应对星载芯片单个粒子翻转对系统的影响。通过模块化设计和乘法器复用,进一步降低了资源开销。

1 ZF检测算法资源占用率分析

假设MIMO 信道矩阵为H ,接收信号为y,发送信号为x。则MIMO 的系统模型可表示为

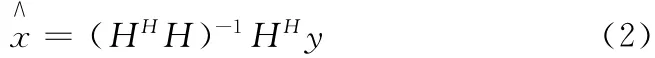

式中:n——信道噪声,则ZF检测可表示为

可以看到ZF检测算法的复杂度为2 N3(N 为MIMO 的天线数量),约使用22个乘法器,占用大量资源[7],并且星载平台采用的TMR 设计会进一步增加资源占用率。分析TMR-ZF检测算法资源占用率高的原因,主要是运算中含有大量矩阵乘法运算,因此本文的以降低矩阵乘法运算资源占用率为切入点,给出一种基于EDAC 的矩阵乘法设计,通过降低MIMO 检测算法中矩阵乘积的资源开销来降低整体算法的资源占用率并提高抗SEU 性能。

2 EDAC星载ZF检测算法设计

EDAC星载检测算法采用类二维内存EDAC 方法进行矩阵乘法运算[8,9],其中二维内存EDAC 方法是通过在数据块的水平方向和垂直方向分别加入k位和l位校验信息,在水平方向进行单纠错-双检错码 (EDAC)编码,在垂直方向进行奇偶编码,可以发现出错地址寄存器和出错数据寄存器所在地址,以及出错原因,其原理如图1所示。

图1 基于内存的EDAC设计

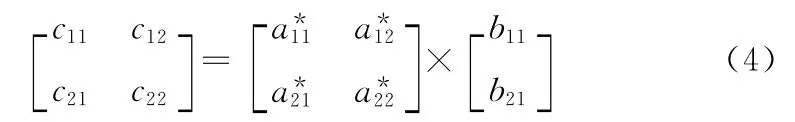

在EDAC星载检测算法矩阵乘法器设计中,矩阵右侧或者下侧加入两行 (两列)含有原矩阵信息的校验行列式,行列式即原矩阵的行或列的 “校验和”,如图2所示。

将式 (2)简化表示为

上式展开为

图2 EDAC矩阵乘法器设计

在矩阵H+中加入两行带有矩阵行列信息的行列式,如式 (3)、式 (4)所示,扩充后矩阵的2 个加权 “校验和” 可 表 示 为 2 个 行 (列) 向 量 [v11v12]和[w11w12],输出矩阵的最后两行 (列)为输入向量的“校验和”的权重因子与x 相乘的结果,表示为[v1v2]和 [w1w2]。其中第1个校验行 (列)可等价于加权因子全为1的行向量乘以矩阵H+,相当于对H+的列向量求和;第2个校验行 (列)等价于加权因子为1和-1的行向量乘以矩阵H+

其中v11=a*11+a*21;v12=a*12+a*22;w11=a*11-a*21;w12=a*12-a*22。

2.1 检 错

为完成矩阵向量的检错和纠错,引入2个标志量m 和n,定义如下

判断矩阵向量是否发生错误,只需要判断m 和n是否为0,以及m+n 是否为0,三者结合可判断出矩阵向量发生错误的数据块位置,以此检测出故障位置,详述如下:

如果m =0并且n=0,则没有发生错误;

如果m =0并且n≠0,则 “校验和”w1发生错误;

如果m ≠0并且n=0,则 “校验和”v1发生错误;

如果m ≠0并且n≠0,则计算m+n,当m+n=0时,c21计算错误;当m+n≠0时,c11计算错误。

2.2 纠 错

在2.1方式发现故障位置的基础上,用错误数据减去m 就可以获得正确数值。以式 (5)为例

假设计算c21时,受单粒子翻转影响,其值被错误的计算为2.1,即c′21=-2 +2.1 =0.1,此时

由式(9)可知,m≠0、n≠0并且m+n=0,判定c21计算错误,则正确的c21应为c′21-m=-2.1+0.1=-2。

由第2节可知,如果m 或n中有且仅有一个为0,则“校验和”的计算过程中发生错误,乘法器核工作正常,输出结果不受影响,此时可以重新计算一下 “校验和”,并对错误的 “校验和”计算模块重构复位;如果m,n 都为0时,不需要做任何处理,可视为没有发生单粒子翻转;如果m 和n同时不为零,则计算m+n:当m+n=0时,c21计算错误;c11正确的计算结果为c11-m;当m+n≠0时,c11计算错误;c21正确的计算结果为c11-m。

3 基于EDAC-ZF的系统模型设计

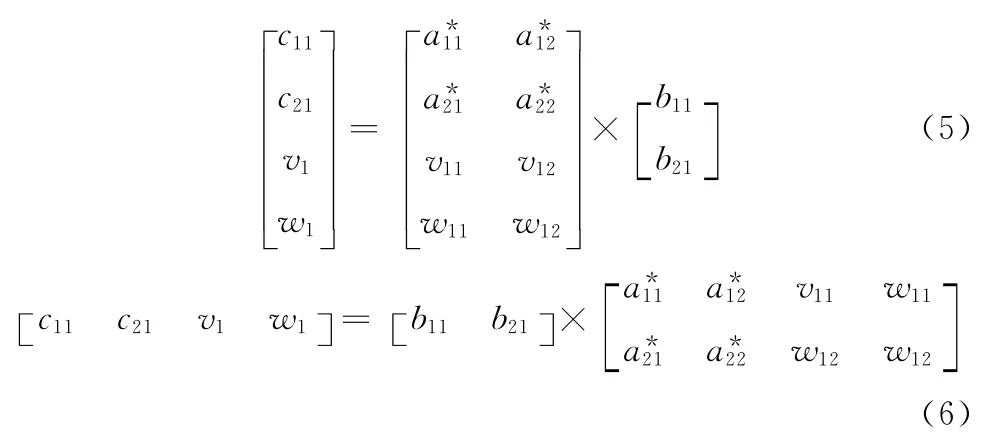

图3是基于三模冗余设计ZF检测算法模型,其中H表示信道矩阵,矩阵x表示输出信号。该设计具有良好的抗SEU 性能,但其资源占用率过高。图4是EDAC-ZF 模型,可以看出ZF检测算法主要包括矩阵求逆运算和矩阵乘法运算。本文将矩阵乘法器和 “校验和”运算过程按EDAC流程进行模块化分组设计,把EDAC-ZF 模型分成EDAC模块、TMR 模块、复用模块,从系统结构角度进一步降低了资源占用率。系统设计如图5所示。

图3 TMR-ZF模型

图4 EDAC-ZF模型

图5 EDAC-ZF系统设计

虚线框表示EDAC 的 “校验和”计算过程,用于检测和纠正由单粒子效应引发的软错误,与三模冗余设计相比,仅使用2/3的乘法器资源。

虚线和实线框部分包括加法、减法、乘法运算模块,其中乘法运算分为4组,分别对应c11,c12,v1,w1的计算过程,每组包含2个乘法器,共8 个乘法器;加法、减法运算 模 块 分 为 两 组, 分 别 对 应 行 向 量 [v1v2]和[w1w2]运算过程。此外,矩阵求逆过程可复用矩阵乘法运算的乘法器核,构成TMR 结构,可进一步降低资源占用率。

灰色框采用TMR 设计,以保证系统整体抗SEU 能力。

4 性能比较

4.1 资源占用比较

为了验证本文所提算法具有资源占用率小的优势,本文针对迫零检测算法和矩阵乘法,在不同数据位宽下3种设计相比无抗SEU 性能算法的资源占用增加率进行仿真实验,其结果如图6、图7所示。从图6、图7可以看出,数据位宽高于15bit时,基于TMR 的设计资源占用增加率最高,且稳定在3.1 倍左右。随着数据位位宽变长,基于RPR的设计资源占用增加率最低,其主要原因是RPR 设计比EDAC少使用(N/2)2面积的乘法器资源,但使用较多的移位和加减运算。在数据位宽低于25时,EDAC 设计资源占用率最低,由于实际通讯中通常采用16bits的数据位宽,因此EDAC设计更适宜卫星通信需求。

图6 矩阵乘法理论资源占用增加率

图7 ZF检测算法理论资源占用增加率

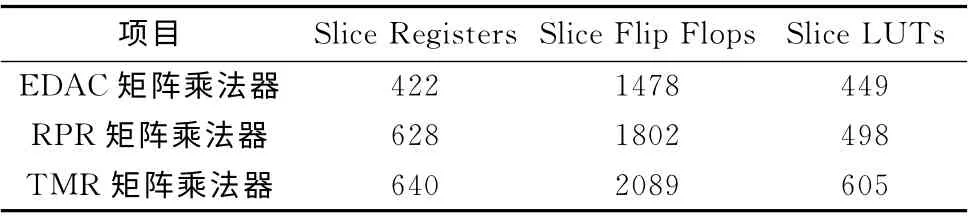

为分析所提的EDAC-ZF检测算法的实际资源占用率,本文基于Xilinx公司的xc5vlx50t-ffg1136c芯片进行了仿真实验,将基于EDAC 设计的ZF 检测算法和矩阵乘法器与TMR 和RPR 设计的资源占用率作比较。仿真条件:收发天线数Nt=Nr=2,调制方式BPSK,数据位宽16,采用Q11定标法。测试结果和资源占用情况见表1、表2。

表1 矩阵乘法器资源占用

表2 迫零检测资源占用和时延

测试结果表明:基于EDAC 设计的ZF 检测算法和矩阵乘法器相比于TMR 和RPR 设计有一定时延,但EDAC和RPR 设计资源占用率优于TMR 设计。其中EDAC 设计比TMR 设计的资源占用率下降约1/3,其主要原因是EDAC设计使用的乘法器个数比TMR 少1/3,并且复用了部分乘法器。EDAC与RPR 设计相比,增加了检错、纠错延时,但降低了芯片资源占用率,并且RPR 设计会降低运算精度。

4.2 误比特率

为分析所提基于EDAC的MIMO 检测算法的误比特性能,本文模拟在星载MIMO 检测算法发生单粒子翻转的条件下,对基于EDAC的ZF和MMSE 检测算法在不同信噪比下的误比特率进行仿真,并与基于RPR 和TMR 设计的MIMO 检测算法进行对比。仿真条件为莱斯信道,收发天线数Nt=Nr=2,信号采用BPSK 调制。仿真结果如图8所示。

图8 MIMO 检测算法误比特性

从图8可以看出,基于EDAC的MIMO 检测算法的误比特性能与基于TMR设计的MIMO 检测算法相比无明显变化。在BER相对较大时,基于RPR 设计MIMO 检测算法的误比特性能明显恶化,并且误比特率下降到一定程度时不随SNR 增大而变化。当BER 较小时,3 种设计的误比特性能相当。其主要原因是,降低精度相当于在MIMO检测额外引入了一定量的 “噪声”,当BER 较大时,降低精度对算法的影响远远大于信道噪声对系统的影响,此时降低精度引入的 “噪声”起决定性作用,使得误比特率不随SNR 增大而变化。当信道环境较差时,信道噪声起主要作用,降低精度引入的 “噪声”对算法的影响很小,使得基于以上3 种设计的MIMO 检测算法误比特性能相当。

4.3 抗SEU 性能测试

抗SEU 性能测试利用Xilinx提供的一个强大的FPGA后端工具FPGA Editor,随机修改电路范围内的LUTs、Block RAM、IO 标准等[10]。模拟故障注入流程如下:

(1)加载原始工程文件;

(2)利用命令控制语句生成模拟故障注入的差异bit文件;

(3)在系统正常工作中,实时动态加载修改后的差异bit文件;

(4)通过JTAG (joint test action group)采 集 结 果 与iSim 模拟的正确结果对比,以判断式 (5)、式 (6)和式(8)中模块在发生单粒子翻转之后是否出错;

(5)如果系统工作正常,重复上述过程 (2)至 (4),并统计测试次数是否达到要求。如果系统功能故障,跳转至过程 (1)。

按以上流程模拟辐射环境下FPGA 发生的单粒子翻转故障,进行5000次故障注入,测试结果见表3。

表3 故障注入测试结果

从表3中可以看出,基于EDAC 的矩阵乘法器和迫零检测算法与TMR 设计相比,降低了发生软错误的概率,软错误减少了约30%,提高了抗SEU 能力,主要原因是EDAC设计的资源占用率下降,受辐射面积减少。与RPR设计相比,软错误数量和系统失效率都有所下降,且RPR设计会降低数据精度。

综合以上的仿真和测试结果可以看出,基于EDAC 的ZF检测算法与TMR 设计相比,仅有较小的时延,但降低了资源占用率,提高了抗SEU 性能,与RPR 设计相比,提升了误比特性能。其综合性能最好,因此更适用于星载平台。

5 结束语

针对现有星载抗单粒子翻转MIMO 检测算法资源占用率高的问题,从其资源占用率最高的矩阵乘法入手,对其实现方式进行改进,提出了一种基于EDAC 的MIMO 检测算法。该算法设计致力于减少资源占用率,提高算法的抗SEU 性能。与基于TMR 及RPR 设计的算法相比,该算法设计不仅降低了单粒子翻转的影响,而且显著减少了资源占用率,提高了系统的可靠性。

[1]Arapoglou P,Burzigotti P,Bertinelli M,et al.To MIMO or not to MIMO in mobile satellite broadcasting systems [J].IEEE Transactions on Wireless Communications,2011,10(9):2807-2811.

[2]Arapoglou P,Liolis K,Bertinelli M,et al.MIMO over satellite:A review [J].Communications Surveys & Tutorials,IEEE,2011,13 (1):27-51.

[3]Jacobs A,Cieslewski G,George AD.Overhead and reliability analysis of algorithm-based fault tolerance in FPGA systems[C]//22nd International Conference on Field Programmable Logic and Applications,2012:300-306.

[4]Sullivan MA,Loomis HH,Ross AA.Employment of reduced precision redundancy for fault tolerant FPGA applications[C]//17th IEEE Symposium on Field Programmable Custom Computing Machines.IEEE,2009:283-286.

[5]Quinn H,Graham P,Morgan K,et al.Flight experience of the Xilinx Virtex-4 [J].IEEE Transactions on Nuclear Science,2013,60 (4):2682-2690.

[6]ZHANG Chao,ZHAO Wei,LIU Zheng.Research of TMRbased fault-tolerance techniques based on FPGA [J].Modern Electronics Technique,2011,34 (5):167-171 (in Chinese).[张超,赵伟,刘峥.基于FPGA 的三模冗余容错技术研究[J].现代电子技术,2011,34 (5):167-171.]

[7]Xilinx.LogiCORE IP multiplier v11.2 [EB/OL]. [2011-03-01].http://www.xilinx.com/support/documentation/ip _documentation/mult_gen_ds255.pdf.

[8]Zarandi HR,Miremadi SG,Argyrides C,et al.Fast SEU detection and correction in LUT configuration bits of SRAM-based FPGAs[C]//IEEE International Parallel and Distributed Processing Symposium,2007:1-6.

[9]Stephani RJ,Vilchis MA,Yeung MM.Construction of an optimized SEC-DED code and logic for soft errors in semiconductor memories[P].U.S.Patent 7,117,420,2006-10-03.

[10]Xilinx.Partial reconfiguration user guide[EB/OL]. [2010-03-03]. http://www.xilinx.com/support/documentation/sw_manuals/xilinx12_1/ug702.pdf.