基于BF533和FPGA的雷达信号模拟器设计实现

史高杨,胡兆峰

(西安电子科技大学电子信息攻防对抗与仿真重点实验室,陕西西安 710071)

随着军事技术的高速发展,现代雷达系统面临着严峻的挑战。为适应新形势,在现代数字信号处理技术和数字计算机高速发展的基础上,计算机仿真技术得到广泛应用,这也促使雷达信号模拟技术快速发展。雷达信号模拟器是现代模拟技术与雷达技术相结合的产物,其在实际雷达系统不具备的条件下产生出所需的雷达回波信号,这在雷达调试、性能评估等方面具有重要用途。且随着雷达信号模拟技术的不断发展,已成为雷达技术的一个重要分支[1]。

当今雷达信号模拟器多采用软硬结合的设计方式,使得系统有更大的灵活性。可采用编程的方法设置所需的模拟雷达信号的各种参数,使模拟器能实现多种信号类型。本文论述的信号模拟器主要针对某雷达对抗设备提出,按照实际要求,产生多通道且相互独立的雷达信号,可提供给雷达对抗设备趋于真实的雷达环境。

1 模拟器设计思想

该雷达信号模拟器的主要设计思想是,对于雷达回波信号,由于数据量大,所以采用高速、高性能的DSP芯片进行部分计算,并实时控制基于FPGA的直接数字频率合成器产生雷达模拟信号[2],且最多可产生4路完全独立的信号。

该模拟器方案计划采用网络和本地两种方式将模拟器的各项参数发送给系统,本地通过一块ARM处理器搭配触摸屏构建人机交互系统,即可接受网络传送的参数也可本地手动设置参数(包括中心:频率、脉宽、脉冲重复周期、调频模式、调频周期、调相编码、子码宽度、天线扫描类型及扫描周期等)。ARM处理器将设置好的参数通过高速USB接口或SPI接口发送至DSP。而DSP接收数据并解析,同时判断每一路信号类型,并计算出实时参数发送给FPGA。

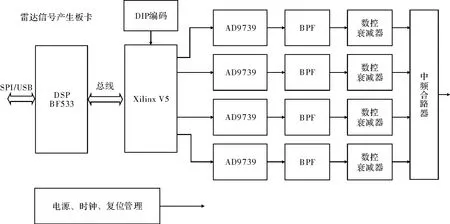

在FPGA内部构建一个直接数字频率合成器,由Matlab预先生成正余弦函数表并导入FPGA的RAM中,以备查找。同时,FPGA将DSP送来的参数也存入RAM,并计算回波信号的实时相位,从而通过相位查找正余弦函数表进行输出。最终通过高速D/A芯片将信号转换为模拟信号,再进行天线扫描调制、滤波、放大输送至射频发送端。信号模拟过程如图1所示。

图1 雷达信号模拟过程框图

2 模拟器的硬件实现

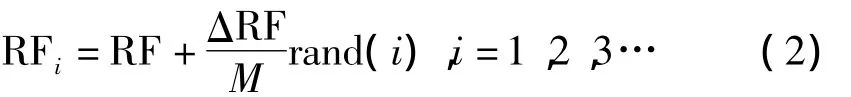

模拟器的硬件实现框图,如图2所示。系统硬件采用ADI公司的BF533作为数字信号处理器。采用Xilinx公司的XC5VLX30芯片作为信号合成模块,并在其内部构建 DDS[3],输出至高速 D/A转换芯片AD9739。天线扫描调制模块由DSP负责脉冲包络调制计算,将计算好的调制码发送给FPGA,再由FPGA控制数控衰减器进行调制。

图2 硬件实现框图

ADSP-BF533是ADI公司主频高达600 MHz的高性能Blackfin处理器,BF533处理器内核包含2个16位乘法器,2个40位的累加器,2个40位的ALU,4个视频ALU和1个40位移位器。外部存储器通过外部总线接口单元(EBIU)进行访问,并可与最多4个异步存储器设备无缝连接。处理器有多个独立的DMA控制器,能以最小的DSP内核开销完成自动的数据传输且拥有1个SPI兼容端口,能使控制器与多个SPI兼容的设备通信。以上特性均满足本方案对数字信号处理器的性能要求,并可高速实现DSP与USB,FPGA以及其他SPI设配的数据交换。

由于DDS内核为全数字结构,其本身又是一个相位控制系统,因此可在DDS设计中方便地加入数字调频、调相及调幅的功能,以产生 ASK、FSK、PSK、MSK等多种信号。本设计采用增加多种功能的DDS改进结构,如图3所示。

改进后的DDS可用于产生常见的任意波形,如图3所示。在相位累加器的输入端增加一个加法器,便可实现频移键控(FSK)。若在相位累加器前增加一个频率累加器,则后相位累加器的相位输出呈平方函数特性,而该相位特性是线性调频信号的相位特征,因此可实现线性调频信号。该频率累加器在FPGA通过积分器实现,若在频率累加器前面加一个ROM/RAM,则可由软件来控制完成非线性调频功能。相位累加器的输出信号是代表相位值的数字信号,因此在累加器的后面增加一个加法器便可轻易地实现相移或相位调制。

图3 改进DDS结构

相位波形转换部分用查找ROM表的方式进行,将计算出的相位值作为地址输入,查找出信号幅值输出。因对于一个正弦波,用任意象限的波形数据就能包含整个周期的信息,所以查找表中只需存储[0,π/2]的波形。而在查找的过程中充分利用三角恒等式的变换,故使用了一种近似的方法。假设一个周期的波形用深度为218的地址查找,则1/4周期的信号用位宽16 bit的地址线即可。

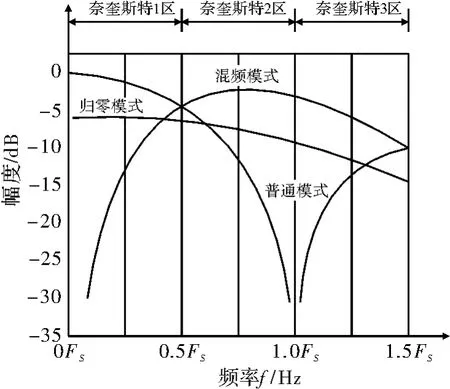

系统中,DAC采用AD公司D/A转换器AD9739。AD9739是一款14位的射频D/A转换器,采样时钟速率最高可达到2.5 GHz,其是目前ADI公司高速D/A产品中转换速率最高的一款芯片。AD9739包含一个串行外设接口(SPI),其被用于状态寄存器的回读和配置。此外,其还有3种工作模式分别为普通模式、归零(RZ)模式和混频模式。这3种模式下的保持采样脉冲频谱图,如图4所示。

图4 3种模式下的保持采样脉冲的频谱图

图4所示,对于普通模式而言,其保持采样脉冲的频谱图为sinc函数,且在Fs处衰减至最低,在与数字样本频谱相乘的过程中,可提取出信号的基频分量,而镜频分量则被有效抑制。但为得到中频频率分量,若使用普通模式,就需要再经过一个乘法器进行混频,进而得到所需的中频信号的分量。对于归零模式而言,其频谱在第1、2、3奈奎斯特区域均相对较为平滑,且在2Fs处衰减至最低,虽频谱相对较为平滑,但其整体而言增益较低,难以有效提取出所需的中频频率分量。而对于混频模式而言,从频谱图可看出,在奈奎斯特2区增益较大,且在0.75Fs处增益达到最大,从而可有效地抑制基频分量而增加镜频分量,并可直接提取出所需的中频频率分量,这相对于普通模式,便可省去混频的环节。由于本模拟器输出的是中频信号,其中心频率为960 MHz,因此文中选用混频模式。

3 模拟器雷达信号类型

从雷达辐射信号波形来看,各种技术体制的雷达选用的信号形式主要包括脉冲调幅信号、线性调频脉冲信号、相位编码脉冲信号等。在雷达信号环境仿真中,需建立雷达信号环境的仿真模型,其中包括雷达脉冲信号模型、天线扫描模型、多信号脉冲排序模型等。本模拟器系统可提供载波频率(RF)模型、脉冲重复间隔(PRI)模型和脉冲幅度(PA)模型[4]。而对于所有的模型均可通过DSP软件计算实现。

3.1 RF模型

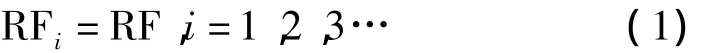

(1)固定载频雷达。对于该雷达,雷达发射脉冲序列的载频保持不变,RF模型为

式中,RF为雷达脉冲载频的中心频率,其为一非时变的确定性常数。

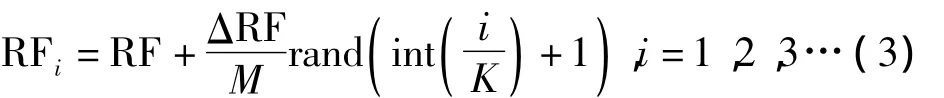

(2)频率捷变雷达。对于该雷达,有两种捷变模式,即脉间捷变频和脉组捷变频模式。脉间捷变频模式采用捷变技术,使雷达每个脉冲的载频在一个较宽的频段上作随机的快速跃变。若频率捷变范围为ΔRF,则脉间捷变频雷达的RF模型为

其中,rand(i)是[0,M -1]之间的均匀分布整型伪随机数;M是捷变频点数。

脉组捷变频模式是指雷达脉冲的载频随机捷变是成组变化的。组内脉冲的载频相同,组间脉冲载频不同,且随机捷变。若频率捷变范围为ΔRF,则脉组捷变频雷达的RF模型为

其中,rand(i)是[0,M -1]之间的均匀分布整型伪随机数;M是捷变频点数;K是分组脉冲数;int(k)是取整函数。

(3)频率分集雷达。对于该雷达,其同时发射一组具有相同脉宽和重频的发射脉冲,这些脉冲的载频各不相同,设频率分集数为M,频率分集的频率集为{RFi,j}Mj=1,则 RF模型为

3.2 PRI模型

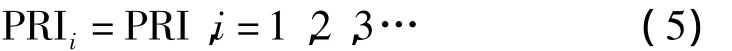

(1)重频固定雷达。对于重频固定雷达,雷达脉冲的脉冲重复间隔(PRI)保持不变,PRI模型为

其中,PRI为一非时变的确定性常数。

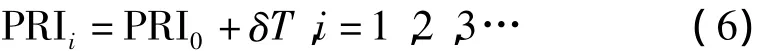

(2)重频抖动雷达。对于该雷达,其PRI值一般是在一定范围内随机变化的。这种变化是随机的,但也可按一定舰律变化。其PRI模型为

其中,PRI0为雷达信号PRI的中心值或平均值,δT是抖动量,其是在范围[-ΔPRI,+ΔPRI]内均匀分布的随机序列。ΔPRI与PRI的比值称为最大抖动量

式中,γ用以表现抖动的相对大小,其典型值为±1% ~±10%。

(3)重频参差雷达。对于该雷达,重频参差雷达是一种具有多个重复频率的雷达。其参差方式一般有2参差、3参差等,最多则可能有16参差。但最常用2参差和3参差。对于具有M个PRI的雷达,PRI模型为

其中,M为参差周期数,每经过M个脉冲,各参差PRI值循环变化一次。参差PRI脉冲列的总重复周期等于所有参差周期之和。

3.3 PA模型

由于仿真的信号环境与侦察系统内部无关,脉冲幅度可用到达侦察系统处的辐射源功率密度表示,这里取功率密度的对数作为脉冲幅度。设雷达信号功率为Pt,天线增益为Gt,侦察机与雷达之间的距离为R,电波大气传播损耗为L,则脉冲功率可表示为

式中,F(θ)为归一化的天线方向图函数。对处于跟踪状态下的雷达,F(θ)=1;而对处于搜索状态下的雷达,F(θ)受雷达波束形状和扫描方式的影响。在具体计算时,使用的脉冲幅度与上式的脉冲功率还需进行转换,将其转换成电压值使用。

4 模拟器的软件实现

在雷达模拟器的设计中,软件设计工作包括通过串行SPI接口[5]编程配置时钟和D/A芯片;DSP通过总线与USB和FPGA进行通信;DSP内部进行数据处理;FPGA利用Verilog[6]硬件描述语言,完成DDS的逻辑译码等工作。

DSP程序主要通过ADI公司提供的开发软件Visual DSP++进行编程,生成可烧写到Flash中的ldr文件。FPGA的编程用Xilinx公司的软件开发包ISE,实现信号合成。系统软件流程图,如图5所示。

中断是DSP与FPGA之间通信的时序控制信号。在每个脉冲周期内,FPGA完成接收DSP通过总线[7]发送的数据,立即给DSP发送中断信号,且通过总线发送一组二进制标志位,低4位有效。FPGA根据时序判断下一组信号的通道号,并将相应位置置位。DSP通过判断标志位来选择发送的雷达参数。

5 结束语

图5 系统软件流程图

文中采用DSP与FPGA相结合的方式模拟雷达信号,并通过软件设置雷达参数。图6和图7为示波器上观测到的实际输出信号。图6为标准正弦输出信号,图7为独立的四通道在不同调制模式下的雷达脉冲。

图6 标准正弦输出

图7 不同调制模式下的雷达脉冲

如图7所示,第1通道为固定频率、固定PRI的脉冲信号;第2通道为频率捷变脉冲信号,可看到相邻脉冲之间频率不同,且变化无规律;第3通道为频率组变,每三个脉冲为一组,组间频率随机变化;第4通道PRI参差调制,每3个脉冲为一周期,组内PRI各不相同。

可看出本雷达信号模拟器能合成出较为理想的各个模式的雷达回波信号。在混频模式下可输出800~1.6 GHz的中频信号,且可通过软件控制4个通道的开关和各自的信号类型,故具有较大的通用性和灵活性。

[1]丁鹭飞,陈建春.雷达原理[M].4版.北京:电子工业出版社,2009.

[2]任丽香,龙腾.一种通用雷达信号模拟器的设计与实现[J].现代雷达,1998,12(6):52 -58.

[3]赵国庆.雷达对抗原理[M].西安:西安电子科技大学出版社,1999.

[4]王传新.FPGA设计基础[M].北京:高等教育出版社,2007.

[5]陈峰.Blackfin系列DSP原理与系统设计[M].北京:电子工业出版社,2004.

[6]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[7]ADI.ADSP -BF533 BlackfinⓇ Processor Hardware Reference[DB/OL].(2011-09-27)[2014 -05 -12]http://www.analog.com/static/imported - files/processor_manuals/ADSP - BF533_hwr_rev3.6.pdf.