硅通孔(TSV)转接板微组装技术研究进展*

刘晓阳,刘海燕,于大全,吴小龙,陈文录

(1. 江南计算技术研究所,江苏 无锡 214083;2. 华进半导体封装先导技术研发中心有限公司,江苏 无锡 214135;3. 中国科学院微电子研究所,北京 100029)

1 引言

随着电子产品向小型化、高性能、高可靠等方向发展,系统集成度也日益提高。在这种情况下,靠进一步缩小集成电路的特征尺寸和互连线的线宽来提高性能的方式受到材料物理特性和设备工艺的限制,传统的摩尔定律已经很难继续发展下去。以TSV为核心的2.5D/3D集成技术已经被广泛认为是未来高密度封装领域的主导技术,是突破摩尔定律的有效途径[1~3]。与传统的2D封装相比,基于TSV转接板的2.5D封装使多个芯片在转接板上直接实现互连,大大缩短了走线长度,降低了信号延迟与损耗,其相对带宽可达传统封装的8~50倍。硅基转接板可以制作更小线宽的互连线,布线密度大大提高,使其满足高性能芯片的需求。硅基转接板与芯片均采用Si做基底材料,二者间的CTE失配较小,芯片所承受的热应力大幅降低,可靠性得以提高。芯片和基板间较短的互连线路可以改善系统电性能[4~5]。因此,多个功能芯片通过TSV转接板形成互连的封装形式越来越受到世界各大半导体公司及科研院所的关注。

在TSV转接板的封装结构中,多个功能芯片放置在转接板上,通过转接板实现芯片之间的互连。TSV转接板的引入,2.5D封装结构与传统的芯片和基板直接互连的2D封装结构的巨大差别,导致其微组装工艺与传统的微组装工艺存在很大差别,并面临新的技术挑战。本文结合TSV转接板的典型封装结构及微组装工艺流程,综述了转接板微组装的研究现状及在微组装工艺流程/工艺参数、多个芯片的精确对准、转接板翘曲、底部填充工艺、微组装相关材料选择等方面面临的关键问题、挑战和研究进展。

2 TSV转接板结构与集成

2.1 TSV转接板典型结构

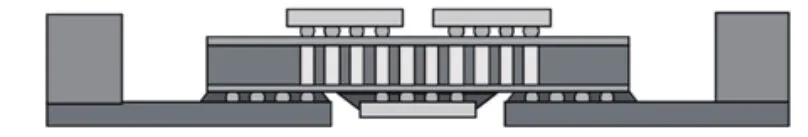

TSV转接板的典型结构示意图如图1所示,转接板衬底材料为硅或者玻璃,在基底上可以集成一些无源组件,如电阻、电容及电感等。TSV是转接板的核心结构,其侧壁沉积了绝缘层/扩散阻挡层/种子层多层金属,TSV孔由电镀的金属铜或钨填满。转接板正面和背面的再分布层(RDL),提供TSV及衬底上已有电路或器件的电学重分布,可为TSV提供更多的连接自由度。转接板正面的窄节距微凸点和背面的C4凸点,分别实现转接板与芯片和基板的直接电学连接。其中转接板与芯片互连的高密度微凸点直径在20 μm以下,节距不到50 μm,以实现转接板与芯片的高密度互连。可以说RDL结合微凸点,提供了TSV与堆叠芯片的电学接口。

TSV技术是2.5D转接板实现3D集成的核心技术,目前TSV深宽比可达到10∶1。为降低封装尺寸和TSV制造难度,需要对转接板晶圆衬底进行减薄处理。目前通常将转接板减薄到100 μm以下,远低于功能芯片的厚度。此外为实现与多个功能芯片的互连,转接板尺寸需大于与之集成的多个芯片尺寸之和,常见的转接板边长在20 mm以上[6,7]。由此可见,超大尺寸、超薄厚度是TSV转接板的外形结构特点,而转接板上的高密度微凸点尺寸、节距也在随着工艺的进步而不断缩小,并为其微组装工艺带来了巨大挑战。

图1 转接板典型结构示意图

2.2 TSV转接板集成

在转接板封装结构中,多个功能芯片并排放置或堆叠放置在转接板上,通过微凸点与转接板上的互连层连接,再通过TSV连接到封装基板上,完成单个器件的功能,可广泛应用于处理器-存储器系统、图像传感器、RF系统和传感器等[8]。如图2所示,在AMD的一款GPU芯片封装结构中,通过转接板将一个GPU芯片与两个RAM芯片集成在一起,大大提高了带宽及运算速度。该芯片应用于索尼公司2013年生产的PS4中,实现了更出色的游戏画面及更丰富的功能。

图2 基于转接板技术完成的GPU芯片封装

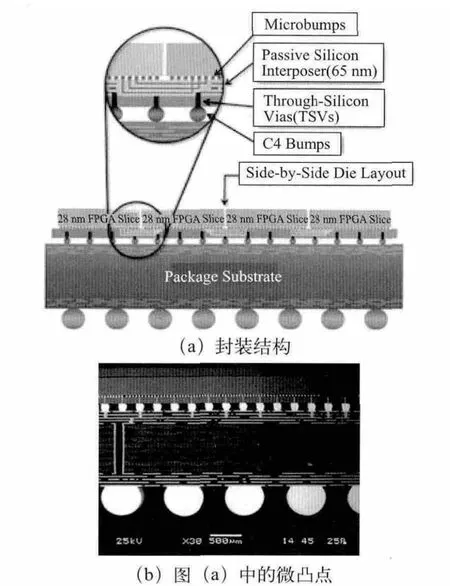

美国的Xilinx公司推出的2.5D封装FPGA产品中,多个FPGA芯片通过转接板形成互连,转接板再通过C4焊点与基板相连,如图3所示[9]。在该器件的封装结构中,4个FPGA芯片尺寸均为7 mm×12 mm,放置在25 mm×31 mm×0.1 mm的转接板上,再通过C4焊点与35 mm×35 mm的有机基板相连。如图3(b)所示,该封装结构共包括材料及尺寸不同的3层焊点:芯片与转接板之间为节距45 μm的铜柱微凸点,转接板与基板之间为节距180 μm的C4焊点,而基板通过节距为1 mm的BGA焊点与PCB板相连。由此可见,在基于TSV转接板的2.5D封装结构中,由于大尺寸、超薄厚度转接板的引入,需研发全新的微组装流程。同时芯片尺寸的增大、低k介质材料的使用、超细节距与超高数量微凸点的存在,使TSV转接板的微组装工艺和芯片与基板直接微组装的工艺相比存在很大差别,给转接板的微组装工艺带来了巨大挑战。

图3 Xilinx研发的2.5D FPGA芯片封装结构

3 TSV转接板微组装要求与工艺流程

3.1 TSV转接板微组装要求

TSV转接板的封装结构中包括多个功能芯片、转接板、基板、尺寸/节距不同的多层级焊点、底部填充胶等关键部件,通过芯片对位、凸点键合、清洗、底部填充等工艺完成其微组装。多个堆叠芯片与大尺寸转接板的精细线路互连,对芯片的对准精度要求严格,以实现不同芯片及芯片模块间的电信号沟通。转接板封装结构中存在尺寸、材料及制备工艺不同的多层级焊点,在微组装过程中需经过多次回流,开发不同的回流工艺。尤其对于芯片与转接板之间的微凸点,其微观形貌对回流/键合工艺极其敏感,并可极大影响微组装后的焊点可靠性。因此微组装过程中对恰当的回流工艺研发提出了更高要求。此外底部填充胶中空洞的存在可加速热循环过程中焊点疲劳裂纹的扩展,降低焊点的热机械性能。因此无空洞的底部填充对于微组装工艺至关重要。TSV转接板封装结构中存在多个芯片的互连,封装密度大,高性能芯片的功耗大。为确保产品的高可靠性,转接板微组装必须构建有效的热量耗散路径,实现良好的芯片散热性能。

3.2 TSV转接板微组装工艺流程

Ganesh. H等通过研究发现,TSV转接板微组装流程的选择,很大程度上取决于包括底填充材料、焊剂、基板等封装材料的选择,以及芯片尺寸、转接板设计和转接板制作工艺等[9,10]。 常见的转接板微组装流程可总结为“自上而下”和“自底向上”两种。自上而下的微组装,即先将芯片与转接板互连,再将其与基板完成互连。在这种微组装方式中,转接板背面的C4凸点缺乏保护而非常容易损伤。而在自底向上的微组装流程中,首先将转接板与基板完成互连,然后再完成与芯片的微组装。这种微组装方式因转接板与基板的热膨胀系数差异,易造成转接板翘曲变形。中科院微电子所采用新的微组装工艺流程完成了转接板与测试芯片的微组装,即先将转接板倒置,用专用夹具卡好转接板后与芯片完成互连;再将互连好的芯片/转接板翻转并与基板完成互连[11]。与普通的自底向上的微组装流程相比,该方法可有效保护转接板背面的C4凸点,如图4所示。

4 TSV转接板微组装技术挑战

4.1 大尺寸芯片/转接板翘曲控制

在转接板封装结构中,转接板与多个并排放置的芯片形成互连,由此可知需要转接板尺寸远大于传统的硅芯片尺寸,一般边长可达20 mm以上。同时,转接板在厚度上非常薄,只有不足100 μm[9]。如此超大尺寸、超薄厚度的硅基转接板极易发生翘曲。研究表明,转接板的结构设计与制作工艺对其翘曲有很大影响。TSV转接板制作过程中,由于TSV铜柱的热膨胀系数与硅存在差异,导致转接板晶圆在退火过程中发生翘曲,转接板背面研磨等工艺,加剧其翘曲变形;F.X. Che等详细研究了TSV电镀后面铜(Cu overburden)的厚度、TSV结构、退火时间、CMP工艺等对TSV晶圆翘曲的影响,发现TSV晶圆随面铜厚度的增加、退火时间的延长、退火温度的降低而增加[12]。此外,转接板表面的多层布线也对其翘曲变形有一定影响。由此可见,转接板在微组装之前,已经有了一定的翘曲变形。

图4 新型的微组装工艺流程

微组装过程中多个因素可导致转接板翘曲加剧。首先是微组装流程的影响。当进行自底向上的组装流程时,先将转接板与有机基板进行互连。而硅基转接板与有机基板热膨胀系数差别巨大,导致转接板在加热过程中膨胀加剧。其次是微凸点键合温度的影响。芯片与转接板之间的焊点通常为电镀有少量纯锡或锡基二元焊料的铜柱凸点,该凸点回流或热压键合温度一般高于250℃。如此高的键合温度易造成转接板和大尺寸芯片发生翘曲,加剧加热过程中转接板的翘曲程度[13]。K.Murayama等研究表明,边长为26 mm的转接板在回流过程中产生的翘曲可达429 μm[14]。在转接板与芯片间的微凸点结构中,铜柱凸点顶部只有极薄的一层焊料,通常只有几微米厚,以防止在回流过程中造成超密度微凸点的短路。转接板在垂直方向上的翘曲变形导致该层微凸点不在一个平面上。当翘曲达到一定程度,转接板/芯片边缘的部分焊点在回流过程中可发生虚焊失效。如图5所示,转接板边缘部位多个焊点出现了虚焊现象,严重影响键合质量及互连可靠性。如何改进微凸点材料、结构,优化回流工艺,减小转接板翘曲,避免焊点高度差造成的焊接失效是转接板微组装过程中急需解决的问题。

图5 微凸点的焊接失效

4.2 细节距微凸点互连

在高密度三维集成中,微凸点是一项关键技术,为堆叠芯片与转接板的集成提供电气互连[15]。随着封装技术的发展和带宽的不断提高,在芯片上需要引出越来越多的引入/引出端。I/O数目的增加,促进了凸点技术向着超高密度方向不断发展。当IC技术发展到32 nm,出现了60 μm节距的小尺寸、细节距的微凸点。当芯片达到22 nm节点,凸点降至50 μm节距以下。在Xilinx的FPGA封装结构中,转接板与芯片之间分布有几千个节距为45 μm的微凸点。而目前在国际顶尖的半导体企业/研究所,可制作出直径10 μm、节距20 μm以下的微凸点,单颗芯片上的凸点数量有上万个甚至达到106个[16~18]。

微凸点的结构和制备工艺与传统的C4焊点相比存在很大差别。为实现高密度互连,这些小尺寸、窄节距的微凸点通常由电镀的铜柱和顶部焊料帽组成,凸点高度只有不足10 μm,而焊料帽所占比例较小,其高度通常仅2~4 μm。凸点结构中少量的焊料在回流中所造成的坍塌影响小,并可以防止焊料过量导致的桥接短路。因此它能在保证凸点高度的同时减小节距,从而增加凸点密度以提高I/O互连密度。但是如上文所述,如此少量的焊料对TSV转接板的翘曲控制要求严格,否则极易在微组装过程中发生虚焊现象。此外,焊料盖帽在回流过程中与铜柱发生反应,大部分甚至全部耗尽生成了CuSn金属间化合物[19]。CuSn金属间化合物的杨氏模量和硬度远高于锡基焊料,为典型的脆性材料。由于CuSn化合物与铜的热膨胀系数存在很大差别,在热循环过程中极易在两者界面产生较大应力和微小裂纹。一旦微小裂纹产生后,由于化合物脆性的材料本质可导致裂纹在界面迅速扩展,最终导致整个凸点的开裂失效[20,21]。如何调节凸点回流工艺以控制化合物的快速生长,防止微凸点的开裂失效,是TSV转接板微组装工艺面临的又一技术挑战。

4.3 底填工艺技术

底部填充胶用来填充由焊点连接的芯片与转接板、转接板与基板之间的空隙,来缓解芯片、焊点、转接板、基板之间的热膨胀系数不匹配造成的热应力,降低焊点因热应力导致断裂失效的风险,其工艺的成败在很大程度上影响到封装的整体可靠性[22]。在底填过程中,填充胶分布在芯片边缘,然后在毛细管作用力下流过焊点间的空隙。2.5D封装结构中大尺寸芯片和转接板的使用,大大增加了底填胶的流动面积和底填充工艺时间。超高数量、超细节距的微凸点,使填充胶流动速度减慢。此外,凸点图案的不均匀分布,以及微凸点高度降低导致芯片与转接板间的间隙减小,严重影响了底部填充胶的流动性,使填充胶流动前端形状不规则。以上几种因素造成的底填工艺时间延长、底填胶流动速度减慢及流动前端形状不规则,导致底填胶在渗透流动过程中极易在微凸点周围形成空洞[23],严重影响倒装芯片封装的可靠性。

此外,由于转接板与芯片间微凸点过小的节距和高度,导致凸点在回流过程中使用的助焊剂很难由清洗剂进入到芯片与转接板的间隙内进行彻底清洗,从而造成焊点周围助焊剂的桥接,如图6所示。这些残留的助焊剂在后续的底部填充工艺中会阻碍填充胶的流动,造成填充不良的缺陷[24]。

图6 助焊剂在微凸点上的桥接现象

底部填充工艺是3D封装中的一个关键问题,严重影响到封装质量及后期的可靠性。由此,研究人员致力于研发针对高密度3D封装的新型填充胶和底部填充工艺,其中无流动底部填充胶是最近发展起来的一种底填胶材料,这种填充胶最初应用于倒装焊结构中,在3D封装中被认为是下一代底填胶,以取代标准的毛细作用填充胶[25]。无流动底填胶在晶圆凸点制作完成后,通过旋涂的方式置于晶圆上,部分固化后芯片与转接板间的微凸点通过回流或热压的方法完成键合。在凸点键合前底填胶必须软化,并拥有良好的流动性以填充微凸点之间的间隙;而在凸点键合后,底填胶中的有机物发生交联反应,底填胶固化来为凸点提供机械支撑。这种底填工艺的难点是交联反应不能发生得太快,以免在微凸点键合过程中产生空洞。此外,填充胶中的颗粒物在底填工艺中的聚集、陷入也是容易造成填充不良的一个原因[26]。使用无流动底填胶可能出现的缺陷如图7所示[27]。因此,如何根据微凸点的结构和图案设计开发合适的填充胶,设定恰当的底填、固化时间和温度是TSV转接板底部填充工艺的关键技术挑战。

4.4 芯片与转接板的精确对准

在2.5D/3D封装结构中,堆叠的芯片间及芯片与转接板间的对准精度至关重要,直接影响了芯片信号的传输性能。精确地对准可有效减小传输信号损失及通道串扰[28]。但与此同时,在2.5D/3D封装结构中由于硅基芯片与有机基板热膨胀系数不同,在微组装过程中易出现因芯片与基板的变形量不同而造成水平方向上的偏移。在传统的二维封装结构中,因芯片、基板尺寸不大,错位问题并不突出;随着2.5D/3D封装技术的发展和芯片、转接板与基板尺寸的增大,水平偏移量也明显增大。此外,芯片与转接板间的超细凸点节距和超大凸点数也给对准技术带来严峻挑战,当凸点节距和凸点数目超过一定极限时,极有可能出现凸点无法识别的情况。由此可见,在2.5D封装结构中,芯片、转接板、基板尺寸的增大,凸点尺寸的减小及密度的大幅提高,使芯片与转接板间的精确对准成为微组装工艺的一个技术挑战。

图7 无流动底填胶工艺可能出现的缺陷

5 TSV转接板微组装研究进展

2011年,美国Xilinx公司与台积电合作,利用TSV硅基转接板技术推出了2.5D封装的FPGA产品Virtex-7 2000T。这是国际上首次利用转接板技术实现了功能芯片的3D封装并成功应用于电子产品。该封装结构中转接板上排列了4个28 nm工艺的FPGA芯片,采用了“自上向下”的微组装流程。首先将切成单颗的FPGA芯片与转接板互连,转接板与芯片之间用底填料来进行微凸点保护。再将互连后的转接板通过标准的C4工艺互连到封装基板上。芯片背面放置散热片进行散热并改进封装体的平整度[9]。该公司详细研究了回流工艺、底填充材料对转接板翘曲的影响。随后,世界各大顶尖的半导体公司和研究所开发出了不同TSV转接板的3D封装结构并完成微组装工艺。2013年,台湾工业技术研究院成功完成了转接板与芯片的双面互连[29]。该封装结构如图8所示,其中转接板边长18 mm,厚100 μm,TSV直径10 μm。正面有3层再布线层,背面有2层再布线层。在转接板的中间部分,正面安装有2个功能芯片,背面安装有1个芯片。转接板四周设计有测试结构,用于TSV性能及封装共面性测试。转接板微组装过程中,首先安装转接板背面的芯片,完成芯片的回流和底填充工艺。然后将转接板安装在有机基板上并进行回流、底填充和固化。再安装转接板正面的2个芯片,并完成回流、底填充和固化。最后在有机基板背面植球并进行回流,完成转接板的微组装。X-ray结果显示转接板上的3个芯片安装均精确对准,封装结构的剖面SEM图像和电测结果显示微组装效果良好。

图8 TSV转接板与芯片的双面封装结构

2014年,台湾矽品精密工业同样采用“自上而下”的微组装方式完成了转接板和2个功能芯片的微组装,但其具体的微组装工艺与Xilinx有所不同。为防止转接板在回流过程中发生翘曲,该公司首先将转接板芯片临时键合到一承载片上,然后将两个功能芯片放置在转接板上,完成铜柱凸点的回流、底填充和固化。接着进行转接板与临时承载片的分离,通过标准的C4焊点回流工艺与有机基板互连,并完成底填充[30]。微组装后对该封装结构在25~260 ℃范围内进行热加载,其翘曲变形稳定在50 μm左右,良好的翘曲控制确保了封装结构的可靠性。随后在改进C4凸点结构和设计后,所有微组装样品均通过了JEDEC标准可靠性测试,包括吸湿测试、高温存储、加速寿命试验和热循环测试,表明转接板的微组装工艺非常成功。

台湾积体电路制造公司于2013年成功完成了逻辑芯片与转接板晶圆的微组装,代表了先进的转接板微组装水平[31]。首先将减薄、切割后的芯片放置在转接板晶圆上,通过微凸点键合完成两者的互连。随后将载有芯片的转接板晶圆减薄到100 μm,露出背面TSV并完成C4凸点工艺。然后将转接板晶圆切割成尺寸为26 mm×24 mm的转接板基片,每个转接板上载有两个40 nm芯片和一个28 nm芯片。最后将转接板微安装到40 mm×40 mm的有机基板上,完成整个封装结构的微组装。在微凸点中设计了菊花链测试结构和开尔文测试结构,结合有限元分析方法及DOE实验设计对微组装的可靠性进行了器件级和板级的一系列测试,并指导微组装工艺的改进。在有些工艺流程中发现了翘曲变形、铜凸点与铝垫剥离等失效模式。

在国内,华进半导体封装先导技术研发中心针对一款高性能CPU芯片进行了TSV转接板的设计与制作,并完成了芯片与转接板的微组装。该封装结构中芯片尺寸为18 mm×16 mm×0.75 mm,TSV转接板尺寸为22 mm×20 mm×0.12 mm,12层BT基板尺寸为47.5 mm×47.5 mm×1.19 mm。TSV孔直径20 μm,深宽比为6∶1。该微组装工艺中首先将转接板与有机基板互连,完成凸点的热压键合;再将微组装后的转接板/基板结构与芯片完成互连,最后进行助焊剂的清洗、两层焊点的底部填充和固化。转接板微组装后的结构及X-ray检测结果如图9所示。研发人员针对该封装结构进行了飞针测试和电测试。飞针测试在转接板与基板微组装后进行,测试结果显示所有链路均连通,表明转接板上的信号通道电学连通,转接板和基板的互连结果良好。转接板测试区包含多个电测试结构,包括直流和高频测试结构、RDL层/TSV的共面波导传输线结构与微带线结构、TSV的菊花链和开尔文测试结构。图10给出了含TSV的GS测试结构S11和S21测试结果。电测试结果验证了TSV和RDL的制作工艺可靠性,展示出了TSV高速传输的能力,并验证了微组装工艺的可靠性[32]。

图9 CPU芯片与转接板微组装后的结构及X-ray检测结果

图10 转接板微组装结构的部分电测结果

6 结束语

本文说明了TSV转接板结构与应用,阐明了TSV转接板微组装流程与要求,详细论述了高深宽比转接板的微组装工艺面临的一系列技术挑战,最后介绍了转接板微组装技术目前的进展情况。主要结论总结如下:

(1)TSV转接板与多个功能芯片在垂直方向上的互连,使电子元器件的封装从二维尺寸拓展到三维,极大提高了封装密度,减少了布线长度、减小了信号延迟并降低了功耗。目前主要应用于FPGA、GPU等芯片的高端封装领域。(2)TSV转接板的微组装流程选择,很大程度上取决于包括底填充材料、焊剂、基板等封装材料,以及芯片尺寸、转接板设计和转接板制作工艺等。常见的转接板微组装流程可总结为“自上而下”和“自底向上”两种。(3)微组装的主要技术挑战来自于多个芯片的堆叠利用,高密度微凸点与大尺寸薄转接板键合工艺以及新型凸点材料、底填胶、低k介质等多种新型封装材料的使用,大尺寸芯片/转接板翘曲控制、细节距微凸点互连、底填工艺技术、芯片与转接板的精确对准。(4)目前转接板技术进展顺利,产业界已经能够小批量生产,如何减低成本、提高良率是进一步规模化量产的关键。

[1] G Parès, C Karoui, A Zaid, etc. Full Integration of a 3D Demonstrator with TS V First Interposer, Ultra Thin Die Stacking and Wafer Level Packaging[C]. Proceedings of the 2013 Electronic Components and Technology Conference,2013.305-316.

[2] C Ferrandon, A Jouve, S Joblot, etc. Innovative Wafer-Level Encapsulation & Underfill Material for Silicon Interposer Application[C]. Proceedings of the 2013 Electronic Components and Technology Conference, 2013.761-767.

[3] J Kim, J Cho. TSV Modeling and Noise Coupling in 3D IC[C]. Electronics System Integration Technology Conference, 2010.208-213.

[4] Y H Zhu, S L Ma, Q H Cui, etc. Design and Fabrication of a TSV Interposer for SRAM Integration[C]. Proceeding of the 2011 International Conference on Electronic Packaging Technology and High Density Packaging,2011.825-831.

[5] R Zhang, J C C Lo, S W RLee, etc. Design and Fabrication of a Silicon Interposer With TSVs in Cavities for Three-Dimensional IC Packaging[J]. Device and Materials Reliability, 2012, 12 (2)∶ 189-193.

[6] Z Li, H Shi, J Xie, etc. Development of an Optimized Power Delivery System for 3D IC Integrationwith TSV Silicon Interposer[C]. Proceedings of the 2012 Electronic Components and Technology Conference, 2012.678-682.

[7] J U Knickerbocker, P S Andry, E Colgan, etc. 2.5D and 3D Tech nology Challenges an d Test Vehicle Demonstrations[C]. Proceedings of the 2012 Electronic Components and Technology Conference, 2012.1068-1076.

[8] K Zoschke, J Wolf, C Lopper, etc. TSV based Silicon Interposer Technology for Wafer Level Fabrication of 3D SiP Modules[C]. Proceedings of the 2011 Electronic Components and Technology Conference, 2011.836-843.

[9] R Chaware, K Nagarajan, S Ramalingam. Assembly and Reliability Challenges in 3D Integration of 28 nm FPGA Die on a Large High Density 65 nm Passive Interposer[C].Proceedings of the 2012 Electronic Components and Technology Conference, 2012. 279-283.

[10] G Hariharan, R Chaware, L Yip. Assembly Process Qualification and Reliability Evaluations for Heterogeneous 2.5D FPGA with HiCTECeramic[C]. Proceedings of the 2013 Electronic Components and Technology Conference,2013. 904-908.

[11] Y Lu, W Yin, B Zhang, etc. A New 2.5D TSV Package Assembly Approach[C]. Proceedings of the 2013 Electronic Components and Technology Conference, 2013.1965-1969.

[12] F X Che, H Y Li, X W Zhang, etc. Wafer Level Warpage Modeling Methodology and Characterization of TSV Wafers[C]. Proceedings of the 2011 Electronic Components and Technology Conference, 2011.1196-1203.

[13] Y W Huang, Y M Lin, C J Zhan. Assembly of 3D Chip Stack with 30μm-Pitch Micro Interconnects Using Novel Arrayed-Particles Anisotropic Conductive Film[C].Proceedings of the 2013 Electronic Components and Technology Conference, 2013.71-76.

[14] K Murayama, M Aizawa, K Hara, etc. Warpage Control of Silicon Interposer for 2.5D Package Application[C].Proceedings of the 2013 Electronic Components and Technology Conference, 2013.879-884.

[15] Effect of Intermetallic Formation on Electromigration Reliability of TSV-Microbump Joints in 3D Interconnect[C]. ECTC,2012.

[16] K C Huang, J Y Chen, H C Tsai, etc. Electroplating of Sn-2.5Ag solders as 20 μm pitch micro-bumps[C].Microsystems Packaging Assembly and Circuits Technology Conference, 2011.1-4.

[17] J DeVos, A Jourdain, M A Erismis, etc. High Density 20µm Pitch CuSnMicrobump Process for High-End 3D Applications[C]. Proceedings of the 2011 Electronic Components and Technology Conference, 2011.27-31.

[18] C K Lee, C J Zhan, J H Lau, etc. Wafer Bumping,Assembly, and Reliability Assessment of µbumps with 5µm Pads on 10µm Pitch for 3D IC Integration[C]. Proceedings of the 2012 Electronic Components and Technology Conference, 2012.636-640.

[19] H Y Son, S K Noh, H H Jung,etc. Reliability Studies on Micro-Bumps for 3-D TSV Integration[C]. Proceedings of the 2013 Electronic Components and Technology Conference, 2013.29-34.

[20] Y W Wang, S H Chae, R Dunne, etc. Effect of Intermetallic Formation on Electromigration Reliability of TSV-Microbump Joints in 3D Interconnect[C]. Proceedings of the 2012 Electronic Components and Technology Conference, 2012.319-325.

[21] C R Kao, H Y Chuang, W M Chen,etc. Soldering Reactions under Space Confinement for 3D IC Applications[C]. Proceedings of the 2012 Electronic Components and Technology Conference, 2012.724-728.

[22] N Islam, A Syed, T K Hwang, etc. Issues in Fatigue Life Prediction Model for Underfilled Flip Chip Bump[C].Proceedings of the 2011 Electronic Components and Technology Conference, 2011.767-774.

[23] I Sousa, L Bélanger, C Dufort, etc. A Manufacturing Approach to Reducing Underfill Voiding on Large Die(>18 mm) Flip Chip Organic Laminate Packaging[C].Proceedings of the 2011 Electronic Components and Technology Conference, 2011.1023-1029.

[24] Y Y Ong, T C Chai, D Q Yu, etc. Assembly and Reliability of Micro-bumped chips with Through-silicon Vias(TSV) Interposer[C]. Electronics Packaging Technology Conference, 2009.452-458.

[25] K J Rebibis, A LaManna, C Gerets, etc. Underfill Material Screening and Process Characterization for 3D Stacking[C].Electronic System Integration Technologies Conference,2012. 13.4.

[26] A Taluy, A Jouve, S Joblot. Wafer Level Underfill Entrapment in Solder Joint during Thermocompression∶ Simulation and Experimental Validation[C]. Proceedings of the 2013 Electronic Components and Technology Conference, 2013. 768-772.

[27] S Kim, S Kruger, B Sapp, etc. Methodology to evaluate pre-applied underfill materials with concurrent flux capability for ultra-fine pitch solder-based interconnects[C].Proceedings of the 2013 Electronic Components and Technology Conference, 2013. 683-687.

[28] H D Thacker, I Shubin, Y Luo, etc. “Dual-Purpose”Remateable Conductive Ball-in-Pit Interconnects for Chip Powering and Passive Alignment in Proximity Communication Enabled Multi-Chip Packages[C].Proceedings of the 2012 Electronic Components and Technology Conference, 2012. 36-42.

[29] P J Tzeng, J H Lau, C J Zhan, etc. Process Integration of 3D Si Interposer with Double-Sided Active Chip Attachments[C]. Proceedings of the 2013 Electronic Components and Technology Conference, 2013. 86-93.

[30] S L Peng, C Y Huang, M H Yang, etc. Integration Study of Die Strength and Various Bumping Volume and Reliability Performance on 2.5D Silicon Interposer Assembly[C]. Proceedings of the 2014 Electronic Components and Technology Conference, 2014. 1-7.

[31] L Lin, T C Yeh, J L Wu, etc. Reliability Characterization of Chip -on-Wafer-on-Substrate (CoWoS) 3D IC Integration Technology[C]. Proceedings of the 2013 Electronic Components and Technology Conference, 2013. 366-371.

[32] X L Ren, C Pang, Z Qin, etc. Design, Analysis and Test of High-Frequency Interconnections in 2.5D Package with Silicon Interposer[C]. International Conference on Electronic Packaging Technology & High Density Packaging, 2014.