基于多通道技术的数字收发单元设计

秦 颖,谢书珊

(南京电子技术研究所, 南京210039)

0 引言

数字阵列雷达是近年来随着数字技术发展出现的一种新体制相控阵雷达,其特点是每个收发通道都由数字方式完成。该体制雷达具有灵活的波形、波束变化能力,并应用先进处理方法优化对目标的跟踪质量,提高了时间、能量、资源的利用效率,赋予雷达更好的反隐身性能[1]。

随着数模混合集成技术的飞速发展,模数转化器(ADC)采样率和直接数字频率合成(DDS)输出频率均不断提高,数模信号的转换越来越靠近天线,数字信号处理已完全实现软件化,这些均意味着数字阵雷达将逐渐向全数字化迈进。同时,数字阵雷达具有通道数量多、设备量大、调试复杂等特点,其系统的集成度、经济性、可靠性也是设计过程中需要考虑的问题。

1 数字收发单元设计原理及关键技术

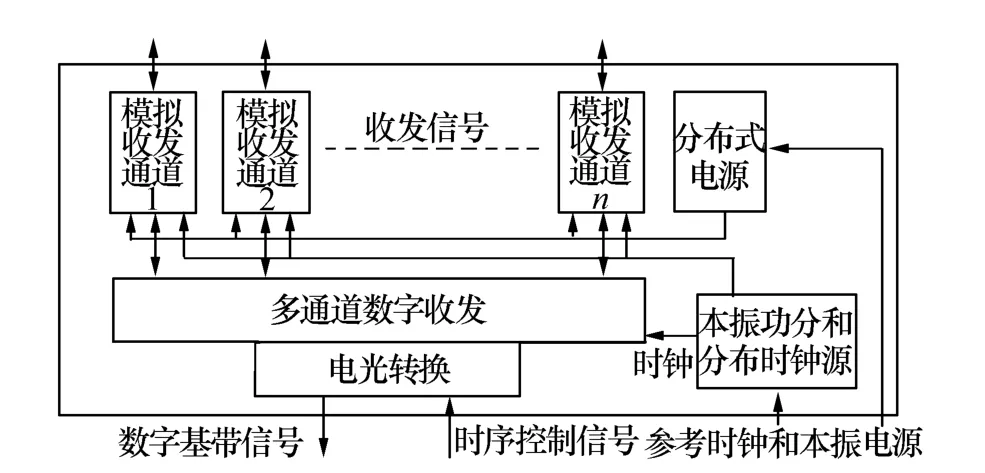

本文介绍了基于多通道技术的数字收发单元设计原理及关键技术,其功能框图见图1。

图1 数字收发单元原理框图

数字收发单元位于数字阵雷达的天线阵面上,是整部雷达的关键部件。发射时,数字收发单元接收频率源产生的本振信号和时钟信号,并分配给每个通道;系统根据雷控指令计算出每个组件中各通道对应的控制码,通道中的DDS根据控制码产生雷达工作的波形信号,再通过选频、滤波、混频、放大等模拟处理后,产生所需频率的激励信号。接收时,雷达回波信号由模拟电路处理为中频信号,经数字中频采样产生并行数字信号,重组、打包后由光纤送到后端的数字波束形成(DBF)继续进行信号数据处理[2]。

2 基于多路集成ADC的数字接收技术

数字中频采样是基于高分辨率的ADC芯片完成从模拟信号到基带信号的一种数字正交下变频技术,同时通过软件编程灵活地实现各种数字下变频器、数字滤波、信道均衡等功能,通过加载新的软件模块即可实现模式切换。这种以软件为核心的处理方式极大地提高了系统灵活性,也有效降低了硬件成本。

理想的中频采样是要利用高速ADC芯片和高性能可编程处理器,使采样频率尽量接近激励信号频率,在尽量宽的带宽上完成模/数(A/D)变换并送入现场可编程门阵列(FPGA)进行处理。由于A/D变换后的处理均通过软件实现,从而给系统带来了巨大的灵活性,这是以往模拟电路处理方式所无法比拟的。因此,数字中频采样具有可编程、可重配置、开放性和稳定性好等诸多优点,但现阶段工程实践中会受到模拟信号的输入频率、带宽,以及实时的数字信号处理能力的限制。因此,实际工程设计时通常在数字中频采样前先进行少量模拟变频、滤波等处理[3],本设计也将采用此处理方式。

以往的设计中,每路模拟接收通道都对应一个单独的ADC器件,每个ADC的时钟及其输出信号都需要谨慎处理,这给通道数量庞大的数字阵雷达带来巨大的工作量。近年来,针对高性能、多功能、低成本、小尺寸的应用,各芯片厂商都推出了多款多通道集成的ADC芯片,本文采用的是ADI公司出品的双通道集成的AD9268。该芯片可同步采集2路模拟信号,转换精度16位,最高采样率105 MS/s。

根据带通采样定理,ADC采样率只取决于信号的载波频率和带宽。对于数字阵雷达来说,多通道的同步性能和一致性能非常关键,因此,ADC采样时钟频率应低于信号载波频率。针对本文信号载波频率130 MHz和带宽5 MHz,综合考虑多个数字收发单元的同步要求和可实现方式,系统的时钟选择为100 MHz。

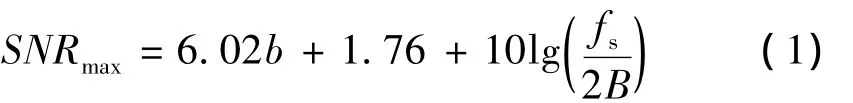

理论上,中频采样模块(ADC+数字下变频(DDC))可以得到的信噪比(SNR)按下式计算

式中:fs为采样频率;b为A/D转换位数;B为输入模拟信号带宽。SNRmax一般由实验测试结果进行标定。输入信号的带宽由 B1变化为 B2时,所能取得的SNRmax也随之变化。

器件资料中,该芯片的动态指标在输入中频999 MHz、采样时钟100 MHz时,SNR=64.7 dB。5 MHz信号带宽时,还能得到10 dB的处理得益(10lg(fs/2B)=10lg(100/2×5)=10 dB),中频数字正交处理(ADC+DDC)的输出动态最大可达74.7 dB,满足系统所要求的动态范围。

中频模拟信号在中放放大后通过匹配滤波器去除带外杂波信号,再经单端-差分处理后送入ADC,被时钟采样后转换为数字信号,送入FPGA进行DDC处理,如图2所示。首先,用全局时钟锁存16位AD数据;然后,与数控振荡器(NCO)产生的数控I/Q正交本振信号混频,经积分梳状滤波器(CIC)完成抗混叠(去镜像)和抽取降速;再针对不同的数据率,采用对应的有限脉冲响应(FIR)低通滤波器进行匹配抽取和数据位截取,输出16位的并行数据;最后,通过数据缓存、重组转换为高速串行信号,由光纤送到后端的DBF继续进行信号数据处理。

图2 A/D采样的处理流程图

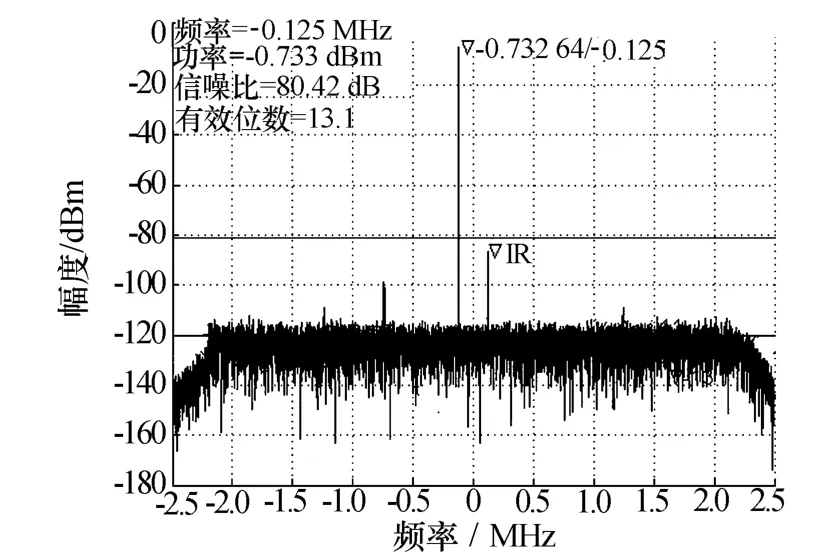

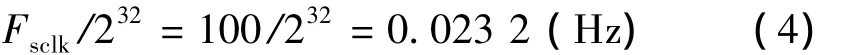

我们对偏离载频0.125 MHz的点频信号对ADC和整个DDC通道进行了数据录取和分析,图3显示了DDC基带信号快速傅里叶变换(FFT)分析的结果。由图可见,FFT分析出的ADC有效位数13.1位,满足系统需求,无杂散动态范围(SFDR)、谐波抑制度、镜像抑制度等指标也很理想。

图3 DDC处理后的基带数据FFT分析

由于ADC器件的非线性特性,实际噪声功率通常会比理论的量化噪声功率高,尤其在单元电磁兼容环境不理想时,会影响收发通道的噪声系数[4]。同时,高性能的ADC是非常敏感的器件,其自身也会被环境中的杂散信号影响。因此,如何保证信号的完整性,对模拟、数字电源隔离和滤波时数字地与模拟地应该如何划分,对参考时钟的处理等都是数模集成系统设计中不可忽视的问题。

3 多通道信号产生技术

DDS是目前广泛应用于电子领域的全数字结构新型信号产生技术。与模拟频率合成技术相比,DDS具有灵活性高、分辨率高及频率转换时间超高速等突出优点,在雷达应用中能更快捷、更灵活地控制发射波形转换和波束扫描,更简单方便地实现各通道间的幅相一致性[5]。随着数字芯片技术的发展,多路集成DDS技术日趋成熟,应用单芯片产生多路输出信号,可极大简化电路设计和印制电路板布局布线,降低组件的复杂度、体积和成本。

针对实例系统中采样时钟100 MHz、中频130 MHz、带宽5 MHz的多路调频、调相信号,本方案选用的DDS芯片型号为AD9959。它是一款各通道独立受控,能产生4路不同输出信号的多通道集成DDS芯片,最高工作频率可达500 MHz。

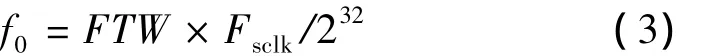

DDS输出频率为

式中:FTW为频率控制字,且0≤FTW≤231;Fsclk为时钟频率。

DDS输出频率分辨率为

由此可见,仅用1片AD9959芯片,就能在小型化数字收发组件中同时产生4路独立可控的中频输出信号,系统结构框图如图4所示。雷达工作中,FPGA根据雷控指令计算出各通道所需的波形码、频率字、相位字、幅度字等,控制AD9959产生多路雷达中频信号。图5和图6即为其中一个通道的输出信号在频域的测试结果。

图4 信号产生系统结构框图

图5 LFM信号频谱图

图6 LFM信号脉内频谱图

AD9959的寄存器采用串口方式进行配置,具体有1线操作、2线操作和4线操作的配置方式,如图7所示。采用1线操作方式时,数据线仅有一根,能有效避免数据线间相互干扰,此系统中采用该方式配置芯片内部寄存器。对AD9959的控制流程如下:在各通道初始化后,先配置通用寄存器激活想要配置的DDS通道,再根据通道寄存器列表的地址对各寄存器进行配置。进行多路DDS操作时,同一个地址和值可同时写入共用的寄存器地址内,控制4路DDS输出相同信号。也可以通过设置通道使能位分别向每个通道写入不同的数据,独立控制不同通道DDS输出[6]。

图7 多路信号产生软件处理流程图

DDS技术的发展为频率合成系统带来了极大的便利,但是器件固有的非线性使得产生输出信号的同时也会产生大量的杂散。因此,必须分析并解决DDS对系统噪声和杂散的影响。

1)DDS芯片内部集成了时钟倍频器,可以将较低频率的参考时钟倍频到高频的工作时钟,但是信号倍频M次后相位噪声就会恶化20lgM。因此,应该尽量放弃使用倍频器,而直接采用高频谱纯度的参考时钟作为DDS的系统时钟;

2)在合成信号的频率较高时,为了实现良好的SFDR指标,DDS输出的差分信号应当采用等终端匹配的方式连接;

3)DDS输出频率分辨率取决于时钟频率和相位累加器位数。因此,一般相位累加器位数N会尽可能做大,但实际波形存储器的容量却有限,用来寻址的位数通常小于N,寻址时相位累加器的低B位就被截去,此时产生的相位舍位误差就会带来大量杂散。如果使B=0,则可以避免出现此类杂散,从而提高输出信号质量。所以,在DDS输出点频信号时,应尽量使频点设计在能被时钟整除的频率。

4 多通道同步技术

在数字相控阵雷达中,多通道之间的同步十分关键,它是目前所研究的难点和热点之一。对数字阵雷达系统而言,同步分为收发单元之间的同步和单元内通道间的同步。数字收发单元中的各功能模块通常采用同一基准时钟触发,从而保证各通道在相位和时序上的一致性,这些通道间的同步就属于单元内同步;而若干个独立的数字收发单元间的同步则属于单元间同步。因此,如何调整系统时钟与控制逻辑之间的相对触发关系是雷达设计中必须解决的问题。

对于本方案100 MS/s的时钟系统,要保证上行DDS和下行ADC的多通道同步,同步精度需达到ns级,则必须严格控制各路采样时钟之间的延迟差异。在电路、系统、软件设计上,我们多方面综合考虑了同步性,主要措施有:

(1)电路设计。单元内部各通道对触发脉冲的同步响应直接影响上行信号相位控制的稳定性、下行信号采样时刻的一致性,对时钟(FPGA时钟、DDS系统时钟、ADC采样时钟)和定时脉冲的硬件通路必须控制等长、减小延迟,并尽量减少相位随环境温度的器件(比如模拟滤波器等);

(2)系统设计。多通道信号产生、信号采样的同步性最基本的条件是收发单元同时响应触发脉冲,数字阵雷达各组件的定时脉冲是同一个信号,而时钟是同源、同频、相参的,所以系统必须保证时钟、定时脉冲到各单元的相位延迟尽可能相同,也就是尽量等距离传输;

(3)软件设计。在硬件上是很难做到多路高速时钟完全同步的,而FPGA的软件化、数字化处理,使得我们可以灵活地控制FPGA内部的时钟相位,从而改变了DDS、DDC的控制码与同步脉冲之间的时序关系,完善系统的同步设计。

5 结束语

本文基于多通道ADC、DDS和多通道同步技术,通过集成、高效的设计方案,完成数字收发单元的原理分析和电路集约化设计,对设计中的要点、难点及主要参数进行了简要阐述,为数字收发单元中的关键技术突破提供了可靠的工程实践支撑。

数字阵雷达是当前雷达技术的前沿,而多通道技术的发展是其最大的推动力之一。近年来,随着高速数字器件的发展,射频直接采样和DDS产生射频信号技术日趋成熟,通道中模拟处理部分逐渐消失。再加上射频集成芯片和系统级芯片的出现,数字收发单元逐渐向芯片化、小型化、低成本、高可靠性方向发展,数字阵雷达也正向着全数字化的方向迈进。

[1]陈文英,陈 玲.海用雷达技术及其进展[J].舰船电子对抗,2008,31(4):25-28,31.Chen Wenying,Chen Ling.Marine radar technology and its progress[J].Shipboard Electronic Countermeasure,2008,31(4):25-28,31.

[2]苏力争,钟剑锋,张建增,等.S波段八通道数字T/R组件研究与设计[J].现代雷达,2013,35(9):66-68,72.Su Lizheng,Zhong Jianfeng,Zhang Jianzeng,et al.Study and design of eight-channel digital T/R module at S band[J].Modern Radar,2013,35(9):66-68,72.

[3]白 晶,陈 翔.米波段数字接收机的设计[J].现代雷达,2005,27(8):71-73.Bai Jing,Chen Xiang.Design for metre wave band digital receiver[J].Modern Radar,2005,27(8):71-73.

[4]张志强,阮黎婷,倪 涛,等.ADC模数转换器有效位计算[J].电子科技,2010,23(3):84-85,110.Zhang Zhiqiang,Ruan Liting,Ni Tao,et al.Calculation of effective numbers of bits for the analog-to-digital converter[J].Electronic Science and Technology,2010,23(3):84-85,110.

[5]张德平,王 超,袁乃昌.基于DDS阵列的发射数字波束形成系统设计[J].现代防御技术,2011,39(1):126-128.Zhang Deping,Wang Chao,Yuan Naichang.Design of transmit digital beam-forming system based on DDS array[J].Modern Defence Technology,2011,39(1):126-128.

[6]陈 菡,谭剑美,吴 兵.应用于数字阵列的多通道波形产生系统设计[J].现代电子技术,2012,35(9):19-21,24.Chen Han,Tan Jianmei,Wu Bing.Design of multi-channel waveform generation system applied in DAR[J].Modern E-lectronic Technique,2012,35(9):19-21,24.