低压高可靠性CAN协议芯片

王淑芬,邵 健,桂江华

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

低压高可靠性CAN协议芯片

王淑芬,邵健,桂江华

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

随着现场总线技术的不断发展,CAN总线在实际中的应用越来越广泛,这对CAN通信的可靠性提出了更高的要求。另外,用户的低压应用越来越普遍。针对这两个方面的要求设计了一款低压高可靠CAN协议芯片,通过芯片中的错误管理逻辑提高了通信的可靠性。

局域网络控制器;低压;可靠性;专用集成电路

1 引言

CAN(Controller Area Network)总线属于现场总线范畴,是一种串行通信协议。它能有效地支持具有很高安全等级的分布实时控制,具有通信速率高、可靠性强、连接方便、性价比高等诸多特点。CAN总线在上世纪九十年代初期成为欧洲的研究热点,近几年随着研究的深入,CAN通信协议得到了进一步的扩展和加强,并形成了国际化标准。本文介绍了CAN通信的协议,分析了CAN控制器在ASIC中的应用以及通信中高可靠性的保证,最后阐述了低压CAN芯片的实现。

2 CAN总线通信协议

2.1CAN总线OSI参考模型

CAN总线协议是建立在国际标准组织的开放OSI 7层互连参考模型基础之上的,其模型分为3层,分别为逻辑链路控制子层、媒体访问控制子层和物理层。逻辑链路控制子层为远程数据请求以及数据传输提供服务,也为恢复管理和过载通知提供手段,并且确定由实际要使用的逻辑链路层接收哪个报文;媒体访问控制子层的作用主要是传送规则,也就是控制帧结构、执行仲裁、错误检测、出错标定和故障界定,总线上什么时候开始发送新报文及什么时候开始接收报文,均在这一子层确定;物理层的作用是在不同结点之间根据所有的电气属性进行位的实际传输。

2.2报文传输

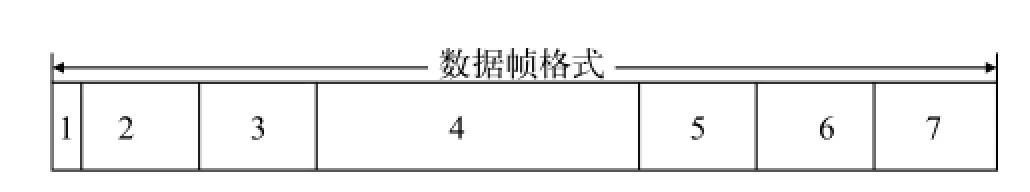

CAN总线有4种帧类型,分为数据帧、远程帧、错误帧和过载帧,帧的格式如图1所示,数据帧由7个不同的位场组成,1为帧起始,2为仲裁场,3为控制场,4为数据场,5为CRC校验场,6为应答场,7是帧的结尾。其中数据场的长度可以为0。

图1 CAN通信数据帧格式

报文以图1中的固定格式在总线上发送,在总线空闲的时候任何连接总线的CAN节点都可以进行发送。如果有两个或者两个以上的节点同时进行报文发送,那么就会产生总线访问冲突,这个冲突可以通过标识符的逐位仲裁来解决。在仲裁期间,每一个节点都对总线进行监测,如果发送和接收的电平相同,则该节点可以继续发送报文。比如发送的是一“显性”电平而监测到的是一“隐性”电平, 则该节点失去仲裁,需要立即退出发送状态。仲裁的机制使得整个CAN网络可以稳定有序地工作。

在CAN系统中,不需要对任何节点的软硬件做任何改变就可以直接添加新的CAN节点。CAN系统中报文传输以多种方式工作,网络上任意节点都可以在任意时刻向所有节点发送报文,不分主从关系。由于系统中引入了报文滤波概念,CAN节点可以实现点对点、一点对多点以及广播方式发送或者接收数据。

2.3同步机制

同步分为硬同步和重新同步两种不同的形式,遵循以下规则:

(1)在一个位时间里只允许一个同步。

(2)仅当采集点之前探测到的值与紧跟沿之后的总线值不相符合时,才把沿用作于同步。

(3)总线空闲期间,有一“隐性”转变到“显性”的沿,无论如何都要执行硬同步。

(4)如果仅仅是将“隐性”转化为“显性”的沿用作于重新同步使用,则其他符合规则1和规则2的所有从“隐性”转化为“显性”的沿可以用作为重新同步。有一例外情况,即当发送以“显性”位的节点不执行重新同步而导致一“隐性”转化为“显性”沿,此沿具有正的相位误差,不能作为重新同步使用。

3 高可靠CAN通信的实现与仿真

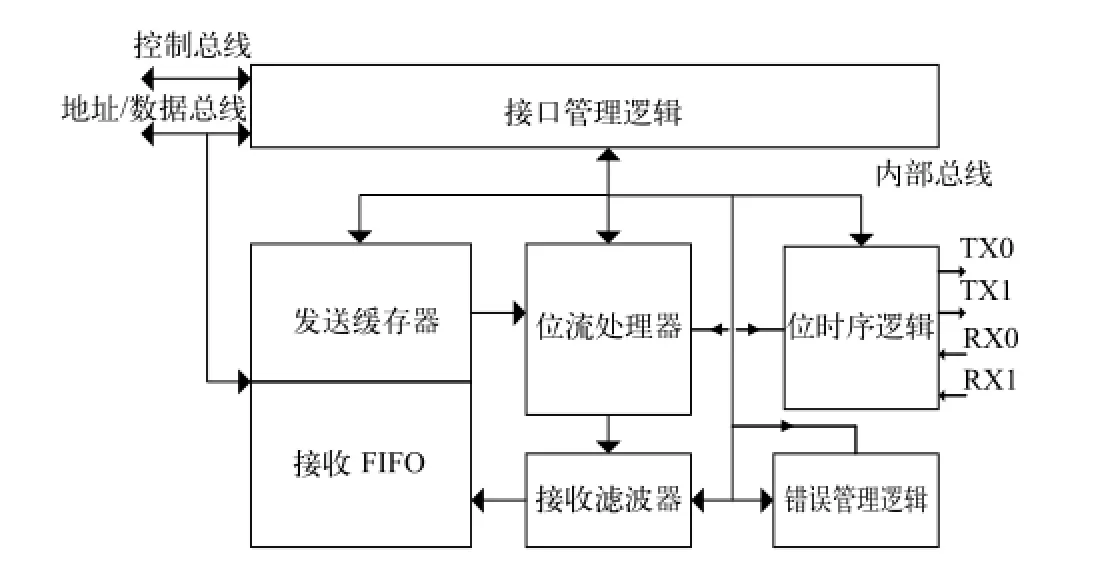

本设计的CAN控制器由Verilog编写,经过综合、布局布线之后生成最后的ASIC电路,电路的模块结构图如图2所示,主要由接口管理模块、发送接收缓冲模块、位流处理模块、接收滤波模块和错误管理模块组成。

本设计的高可靠性主要是通过错误管理逻辑模块来实现的,电路处理错误的整个过程是完全自动的,无论什么时候发生CAN总线错误,它都会强制产生相应的总线出错中断。同时,当前位的位置被存入寄存器,在这个数据被读出之前,它都保持在这个寄存器之中,根据寄存器中的内容区分4种错误类型:格式出错、填充出错、位出错和其他错误。另外寄存器还有额外的信息表明这个错误是在发送还是接收的时候发生的。用户也可以根据这个寄存器里的值知道系统中发生了什么错误。

图2 CAN控制器模块结构图

电路内部有错误计数器,根据一定规则计数器会进行计数,根据计数器的数值,错误状态分为3种:错误激活、错误认可和总线离线,电路总能在其中的某种状态工作。当计数器的值在0~127之间,电路处于错误激活状态,此时产生错误激活标志(6个显性位)。当计数器的值在128~255之间,电路处于错误认可状态,此时产生错误认可标志(6个隐性位)。如果计数器数值大于255,则到达总线离线状态,此时电路自动置位复位请求位。

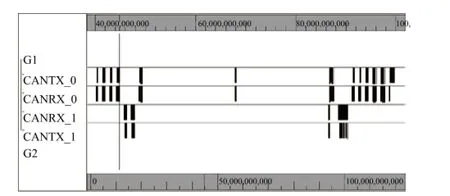

本设计已经通过仿真并且综合成网表应用于项目之中,时序仿真如图3所示。CAN总线的通信速率为500 kbit/s。通过CAN总线接口可完成和外部各个模块的通信。该电路支持版本号的查询、CAN FIFO数据的读取和发送,具有完备的超时重传机制。接收到正确ACK应答信号后,CAN发送端不再发送数据帧;没有接收到应答信号,CAN发送端间隔10 ms通过1通道再次发送,无应答后通过2通道再次发送,之后结束通信。该电路具有看门狗复位电路,保证电路出现异常时能够复位。电路工作异常3 s后电路清0。FIFO通信机制同异步口FIFO通信。由此可见,电路的通道0和通道1收发功能都正常,符合本设计的高可靠性要求。

图3 CAN通信时序仿真图

4 低压CAN芯片的物理实现

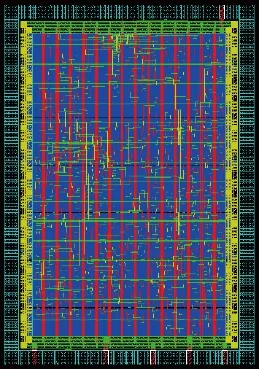

根据电路的性能及市场需求,该芯片采用SMIC 0.35 μm 1P4M工艺流片,工作电压为3.3 V。物理实现的工作包括:布局规划、电源网络设计、标准单元摆放、时钟树综合及优化、布线及可制造性设计、物理验证和流片数据的准备。该芯片面积约4500 μm× 6500 μm,电源网络采用power ring与power stripe构成网状结构,以满足芯片的IR drop和EM,布局如图4所示。

图4 芯片布局规划图

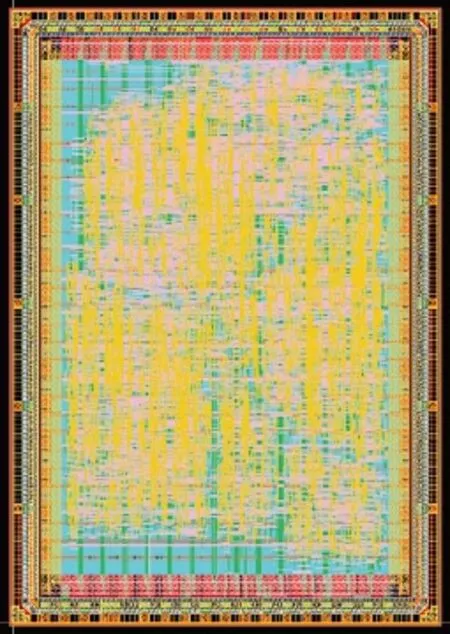

由于管壳腔体和电源管脚的限制,只有3组电源地可供使用,考虑到整体芯片的IR drop和供电能力以及ESD要求,最终使用标准单元库PVDD3和PVSS3供电,将内核与端口的电源地连接在一起,并用5组PVDD3和PVSS3作为filler来完成ESD的泄放回路,最终达到2 000 V的要求,电源与地的IR drop小于 5%。芯片的整体版图如图5所示。

图5 芯片版图概貌图

5 结论

本文针对目前对CAN通信低功耗和高可靠性的要求,设计了一款符合要求的CAN芯片,通过仿真验证了芯片通信的可靠性,版图设计时采用3.3 V工艺实现,流片后的芯片通过J750测试机测试,功能正确,交直流参数正常,可以应用到实际工程中去。

[1] 韩成浩,高晓红. CAN总线技术及其应用[J]. 制造业自动化,2010,2: 146-149.

[2] 姜幼卿,左国华,陈勤学,等. 基于CAN总线的温室自动控制系统的通信设计[J]. 仪表技术与传感器,2005(4): 60-62.

[3] 任俊香. SoC芯片版图的设计与验证[J]. 科学与创新,2015,19: 36-39.

[4] Etschberger K. Controller area network: basics,protocols,chips and applications[J]. 2001.

CAN Protocol Chip with Low Voltage and High Reliability

WANG Shufen , SHAO Jian , GUI Jianghua

(China Electronic Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

With the development of field bus, the use of CAN bus become more and more widely in daily life. So the reliability of CAN communication needs higher requirements. On the other hand, low-voltage is more and more serious. In this paper, a low voltage and high reliable CAN chip is designed for these application. The reliability of communication is improved by the error management.

CAN; low-voltage; reliability; ASIC

TN402

A

1681-1070(2015)12-0027-03

王淑芬(1987—),女,安徽安庆人,工程师,主要研究方向为大规模数字集成电路设计。

2015-10-26