A/D信号的处理与解析

谢立利,陈 洋

(无锡中微爱芯电子有限公司,江苏 无锡 214072)

A/D信号的处理与解析

谢立利,陈洋

(无锡中微爱芯电子有限公司,江苏 无锡 214072)

音频A/D转换芯片的输出增益和失真度是无法直接测试的,需要对输出的数字信号进行解析还原成模拟信号方可以进行测试。有些A/D产品输出的数字信号可以直接进行解析还原成模拟信号,而有些则需要先对输出的数字信号进行处理。以某A/D转换芯片为例,首先利用了六反向施密特触发器74HC14和8位串入并出移位寄存器74HC164对输出信号时序进行转换,然后采用stm32f103对时序转换后的数字信号进行解析,最后将解析后的数据传送至上位机,最终实现了对该A/D转换芯片输出增益及失真度测试的目的。

A/D; 测试; 时序; 解析; 增益; 失真度

1 引言

随着电子技术的不断发展,集成芯片不只是单纯的模拟或数字逻辑,越来越多的芯片使用了数模混合的设计,A/D就是比较常见的一种。文中以某A/D芯片为例,介绍了输出数字信号的分析与处理至解析的过程,实现了对输出幅度及失真度测试的目的,对于相关A/D芯片的测试具有一定的参考和借鉴意义。

2 数字信号的分析

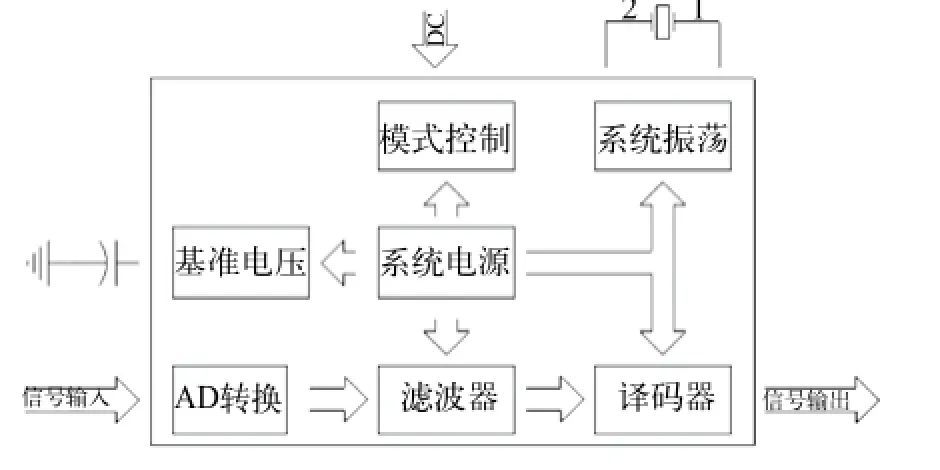

A/D芯片功能框图如图1所示。

输入信号经AD转换后经滤波器输入译码器后输出,其中输出引脚包括SDOUT、SCLK及LRCK引脚。

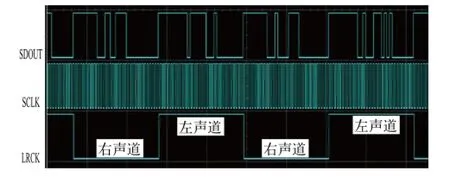

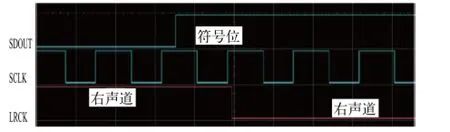

数字信号输出时序如图2所示。

SDOUT为输出的数字信号,SCLK为时钟信号,频率为3 MHz,LRCK为输入通道选择信号,用于判断输出为左声道或右声道输出。从LRCK上升沿或下降沿开始,32个时钟周期的信号表示一个模拟量,低8位为无效信号,最高位的数据为标识位,用来表示模拟量的正负值,若为“0”则表示该模拟量为正值,可直接运算,若为“1”则表示该模拟量为负值,需将输出数字信号取补码后进行运算。该A/D输出的运算公式为out=(SDOUT/223)× REF,其中out为输出的模拟量,SDOUT为数字量,REF为被测器件的基准电压,由于最高位数据为标识位,所以实际的有效数字信号只有23位。

图1 功能框图

图2 数字信号时序

3 数字信号的处理

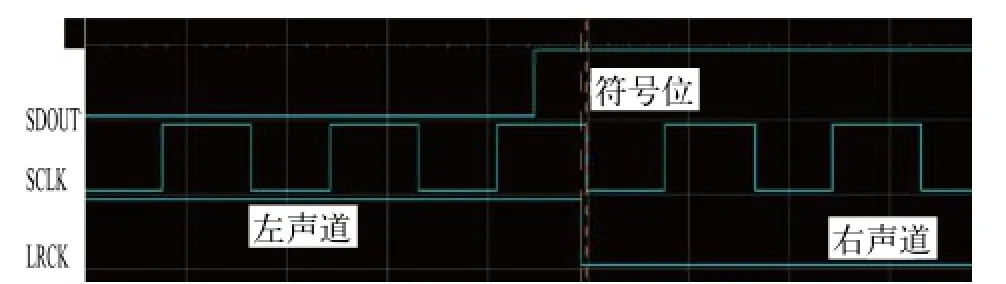

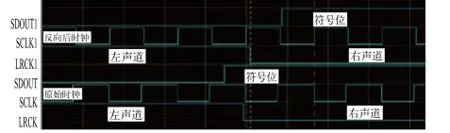

以右声道为例。将波形放大,如图3。

图3 右声道时序

如图3所示,当LRCK为低时,符号位在时钟的下降沿被锁存,但是LRCK的下降沿与第一个时钟下降沿的时间很短,约为10 ns,stm32无法达到该处理速度,所以无法直接解析,要满足解析条件必须使LRCK的下降沿与第一个时钟下降沿的时间足够长,尽量达到一个周期时间的50%以上,对于该问题可以采用一个移位寄存器,将LRCK信号向后移位,由于使用的移位寄存器是74HC164为上升沿触发,如果直接使用该时钟信号对LRCK信号进行移位,那么LRCK将会在时钟信号的第一个上升沿后出现下降沿,如图4。

图4 LRCK移位时序

这显然是不行的,必须使移位寄存器在下降沿触发,对于这个问题,可以在74HC164前面使用一个反相器,使时钟信号反向。根据上面的波形推断,如果将LRCK移位,那么在采样的时候就会将SDOUT数据向后错一位,并且符号位丢失,所以必须也将SDOUT数据进行移位,SDOUT数据可直接根据时钟信号移位,无需将时钟信号反向,否则时序将出现错误,根据以上对输出信号的处理结果如图5。

图5 处理后时序

图5中LRCK、SCLK、SDOUT为原始信号,LRCK1、SCLK1、SDOUT1为经过处理的信号,不难看出。LRCK1、SCLK、SDOUT1这3组信号完全满足了解析的要求。

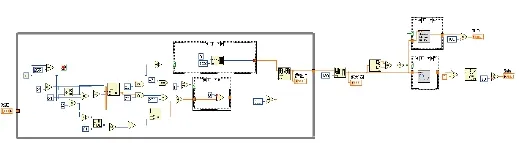

4 数字信号的解析

输出的数字信号需进行解析方可还原成模拟信号,这里采用的解析芯片是stm32f013,利用stm32f103的SPI工作模式对数字信号进行采集。在软件方面使SPI工作在从模式,设置上将NSS端口设置为硬件触发,并将锁存信号设置为下降沿锁存,一次采集16位数据,硬件方面将LRCK1与NSS引脚相连,将SCLK与SCK引脚相连,SDOUT1与MOSI引脚相连,在程序设计上需要一个触发脚,用于判断采样通道,该触发脚与LRCK1及NSS相接,若为左声道,需将LRCK1信号经过反相器后再与NSS引脚及触发脚相接。读取数据程序如下:

for(int z=0;z<257;z++) //采集257个点的数据,其中将第一个点的数据舍去

{

while((GPIOG->IDR & GPIO_BRR_BR0)==0); //等待低电平结束

while((GPIOG->IDR & GPIO_BRR_BR0)==1);//等待LRCK时钟下降沿结束

w h i l e(S P I_I 2 S_G e t F l a g S t a t u s(S P I 2,SPI_I2S_FLAG_RXNE) == RESET);//采集数据

Data[z]=SPI_I2S_ReceiveData(SPI2);//将采集数据放至数组

}

由于一个点的数据为16位,而USB设置为一次只可以传送64个8位的数据,所以必须将一个16位数据拆分为2个8位数据后进行传送。

拆分及传送数据程序如下:

Void Data_log(unsigned int j)

{

unsigned char Write[64];

for(inti=0;i<32;i++)//分段处理

{

if(Data[(j*32)+i+1]&0x800000) //判断符号位

{

Data_logo[(j*32)+i+1]=~Data_logo[(j*32)+i+1];//为1取反

Data_logo[(j*32)+i+1]=Data_logo[(j*32)+i+1]&0xffff00;//数据校正

Write[i*2]=0x80;//符号位传至数组准备发送

}

else

{

Write[i*2]=0x00; //符号位传至数组准备发送

}

Data_logo[(j*32)+i+1]=Data_logo[(j*32)+i+1]&0x007ffff f;//数字量至模拟量转换

AD_Data[i]=Data_logo[(j*32)+i+1]/33554;//134216;//数字量至模拟量转换

Spill=0;

if(AD_Data[i]>255)//数据溢出位

{

Spill=AD_Data[i]/256;//提取溢出位

Write[i*2]|=Spill;//将数据溢出位传至数组准备发送。

}

Write[i*2+1]=AD_Data[i]-Spill*256;//溢出位与数字位处理并将模拟量传至数组准备发送

}

USB_SendData(Write,sizeof(Write));//通过USB通信将数据发送至上位机

}

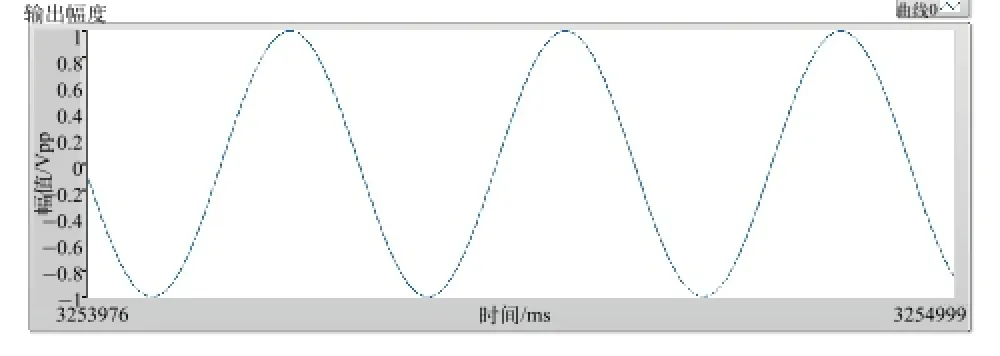

转换后的数据传送给上位机进行运算还原出模拟波形。如图6所示,由于在解析芯片中已经将数字量转换成为模拟量,所以在上位机中只需将接收到的数据直接还原成连续的模拟信号即可,本例中共采集了128个点的模拟数据。采集时输入信号幅度为2.2 Vpp,频率为1 kHz,解析输出信号的幅度为2 Vpp值,失真度<0.5%,如图7所示。由于A/D芯片内部存在固有衰减,所以输出信号幅度比输入信号幅度偏低。

图6 上位机还原程序

图7 输出显示

5 结论

通过以上对A/D输出信号解析过程的介绍,实现了将数字信号还原为模拟信号,达到了对输出信号的幅度与失真度进行测试的目的。

另外,如果A/D芯片输出的高电平电压与stm32工作电压不一致,需采用电平转换芯片将输出高电平电压转换成与stm32工作电压一致,否则可能对解析结果造成影响,严重时会使stm32损坏。并且在解析时对地线也有一定的要求,需保证有良好的接地。

[1] 章佳荣,王璨,赵国宇. 精通LabVIEW虚拟仪器程序设[2] 喻金钱,喻斌. STM32F系列ARM Cortex-M3核微控制开发与应用[M]. 北京:清华大学出版社,2011.4.

计与案例实现[M]. 北京:人民邮电出版社,2013.4.

[3] 刘强,等. 深入浅出USB系统开发:基于 ARM Cortex-M3[M]. 北京:北京航空航天大学出版社,2012.8.

[4] 张顺兴,等. 数字电路与系统设计[M]. 南京:东南大学出版社,2004.8.

A/D Signal Process and Analysis

XIE Lili, CHEN Yang

(Wuxi i-CORE Electronics Co., Ltd, Wuxi 214072, China)

The output Gain and Total Harmonic Distortion (THD) of Audio A/D converter chip cannot be tested directly. The appropriate way requires analysis and reduction of digital output signal into analog signal which can be tested. Some output digital signal from some product can be transformed into digital signal directly,some others needs digital signal processing for transformation. This article introduces a process to treat the digital output signal into analog signal, with the timing sequence transformation using 14 Hex Inverting Schmitt triggerand 74HC164 8-bit Serial-in/Parallel-out Shift Register on top of sampling, analysis and reduction using stm32, which will be transmitted to host computer.

A/D; test; timing sequence; analysis; gain; THD

TN402

A

1681-1070(2015)12-0020-03

谢立利(1981—),男,黑龙江哈尔滨人,2007年毕业于华德应用技术学院应用电子技术系,本科,主要从事数模混合集成电路应用与测试工作。

2015-8-12