全包封功率器件中大芯片表面分层的分析

石海忠,缪小勇,何晓光

(南通富士通微电子股份有限公司,江苏 南通 226006)

组装、组装与测试

全包封功率器件中大芯片表面分层的分析

石海忠,缪小勇,何晓光

(南通富士通微电子股份有限公司,江苏 南通 226006)

全包封功率器件相对于半包封功率器件更容易达到安规要求,其需求出现了逐渐增加的趋势,但是全包封器件的分层问题一直困扰着业界。通过分层现状的调查,分析了分层存在的界面和产生原因,通过优化试验找到了解决分层最有效的措施是中大芯片表面缓冲层,从而使全包封功率器件的可靠性达到更高要求。

分层;全包封;芯片

1 引言

半包封功率器件的应用已经有很长时间了,而全包封功率器件的兴起是在近5年时间内。由于其安全性、抗干扰方面的优势而逐渐得到大家的青睐,但是因为其全包封内部结构的复杂性和不平衡性,很容易在中大芯片等表面产生分层,从而影响了产品的可靠性、散热等。为此需要对市场上应用产品的分层现状进行调查、分析,以找到有效的解决方案,从而使全包封功率器件达到更高的可靠性,满足海外客户的高可靠要求。

2 分层现状

为了充分了解全包封功率器件的分层情况,特地从终端市场上购买了一些典型样品,其中芯片尺寸选择从小到大,分别为2.1 mm×1.9 mm(约4 mm2)、3.9 mm×3.3 mm(约12 mm2)、4.6 mm×4.5 mm(约21 mm2),器件包封的材料主要使用高导热的环氧树脂,添加适量的硬化剂、充填剂、阻燃剂等。在温度循环(TC,Temperature Cycle)试验前只发现大芯片样品在载片台表面有一些分层,参见图1大芯片TC500前分层。而中小芯片的样品都没有发现界面分层。根据JEDEC标准JESD22-A104-C中温度循环条件(-65℃~+150℃ 0.5 h/循环)使用ESPEC TSA-71H温度循环箱对这些样品进行500个温度循环的试验,发现大芯片样品的芯片表面和载片台表面都有较多分层,见图2大芯片TC500后分层。中芯片的芯片表面和载片台表面或多或少也出现了分层,见图3中芯片TC500后分层。而小芯片表面在温度循环后都没有出现分层,只有载片台表面有分层。由于大多数功率器件的载片台不焊接键合丝,芯片和载片台之间通过高粘结力的焊料焊接,载片台分层对器件的可靠性影响较小。而芯片表面的分层直接对芯片表面的焊点有剥离作用,影响芯片表面的热量传递,对功率器件的可靠性影响较大,需要充分分析产生分层的原因,找到合适的解决措施。

图1 大芯片TC500前分层

图2 大芯片TC500后分层

图3 中芯片TC500后分层

3 分层原因分析

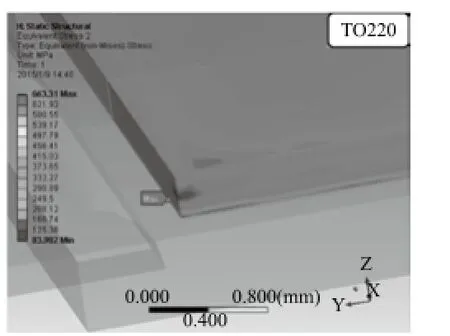

器件内部界面产生分层的原因比较多,如树脂的吸水性、粘结性、老化、内部应力、恶劣环境、机械冲击力、内部结构的不合理、界面的粗糙性等。而针对市场上全包封功率器件的内部分层,从图4全包封功率器件的剖面示意图来看,载片台和芯片在塑封体内部位置明显处于下方,再加上图4 中塑封体由厚薄两部分构成,这种内部结构的不平衡容易在温度循环中产生较大的内应力。针对图4的代表性功率器件建立如图5所示的全包封器件物理模型,通过应力仿真发现,芯片表面最大应力达到663 MPa,分布在芯片的边角位置,见图6芯片局部等效应力仿真图。说明芯片边角处温度梯度最大,造成应力和剪切应力增大,应力和剪切应力最大值出现在芯片边角处时,太大的应力将导致界面的分层。所以芯片表面的应力缓解或增大芯片表面的结合力将是解决问题的关键。

图4 全包封功率器件剖面示意图

图5 全包封功率器件物理模型

图6 芯片局部等效应力仿真图

4 分层改善试验

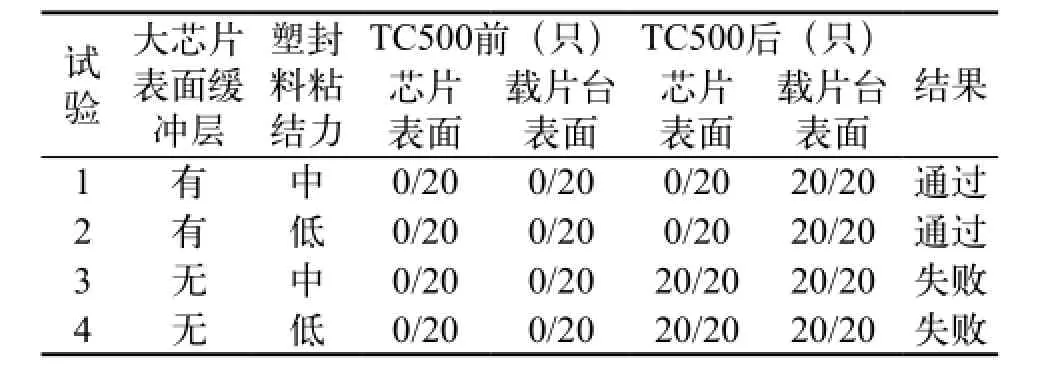

根据之前对终端市场应用的全包封功率器件样品的分层调查和分析发现,芯片越大,在温度循环后分层越严重,从应力仿真的结果也证实了芯片表面的应力最大。所以从应力缓解方面考虑选择大芯片表面有缓冲层,同时选择大芯片表面没有缓冲层作对比。从增大芯片表面的结合力考虑,选择两种不同粘结力的塑封料进行对比。同时考虑到焊料分层较少出现,框架内引线的分层可以采用露铜来解决,所以试验过程主要针对大芯片和载片台表面分层来改善。试验中芯片尺寸选择4.5 mm×4.5 mm(约21 mm2),试验方案和结果见表1。

表1 分层改善试验方案及结果

图7 试验2在TC500后分层图

5 试验结果分析

从表1中可以发现,芯片表面的缓冲层对改善大芯片表面的分层作用非常明显,即使塑封料粘结力偏低一些,大芯片表面分层表现比较好,见图7。而芯片表面没有缓冲层,即使塑封料粘结力偏高一些,仍然抵挡不住内部应力的破坏,芯片表面还是出现了分层。说明芯片表面的缓冲层对改善全包封功率器件的大芯片表面分层非常有效。

从表1还发现,两种塑封料的粘结力对载片台分层没有明显效果,对于应用在工业和消费类领域的功率器件,载片台分层的负面影响比较小。若应用在汽车或军用领域,还需要对载片台表面的镀层、塑封料粘结力等再进行优化试验,以达到高可靠性的目的。

6 结束语

由于全包封功率器件存在大芯片表面的分层问题,影响其可靠性和应用范围。本文通过全包封功率器件分层现状的调查,分析了分层存在的界面和发生原因,通过试验优化发现芯片表面的缓冲层对大芯片表面的分层改善非常明显,而塑封料的粘结性相对于芯片表面的缓冲层来说,其改善效果不太明显。大芯片表面分层的改善可以有效提升全包封功率器件的可靠性、散热性,其应用领域将更加广泛。若需要应用到汽车或军用领域,还需要对载片台表面分层进行有效改善。

[1] 吴建忠,陆志芳. 塑封集成电路分层研究[J]. 电子与封装,2009,9(3):36-40.

[2] 梅跃. 电子封装中湿热载荷共同作用下高聚物材料力学行为研究[D]. 广州:华南理工大学,2013.

[3] 李明奂,王文杰,张宏杰. TO系列塑料封装离层探讨[J].电子与封装,2012,12(8):10-12.

The Analysis of Large Die Surface Delamination on Full Packaged Power Device

SHI Haizhong, MIAO Xiaoyong, HE Xiaoguang

(Nantong Fujitsu Microelectronics Co.,Ltd, Nantong 226006,China)

Full pacakaged power devices relative half packaged power devices easier to achieve safety requirements, which demand has increased gradually, but the delamination of full packaged power devices have been plaguing us. The thesis investigated the current situation of delamination and analyzed the presence interface and causes, so that the large die surface of the buffer layer was found by optimized experiment that are the most effective solution to solve the delamination, thus the reliability of full packaged power devices will achieve higher requirements.

delamination; full package; die

TN305.94

A

1681-1070(2015)12-0001-02

石海忠(1969—),男,江苏南通人,高级工程师,中科院大学集成电路工程硕士,主要从事功率器件的新品开发及封装工艺开发和应用工作。

产品、应用与市场

2015-9-8