噪声调频干扰技术研究及FPGA实现

李永松,吕 昊,刘玉娇

(西安电子科技大学 电子工程学院,陕西 西安 710071)

噪声调频干扰技术研究及FPGA实现

李永松,吕 昊,刘玉娇

(西安电子科技大学 电子工程学院,陕西 西安 710071)

针对线性调频信号,分析了噪声调频信号的波形、频谱及其对脉冲压缩雷达的干扰效果。在此基础上,介绍了噪声调频信号的FPGA实现方法,并对产生的噪声调频信号进行了时频分析,直观地展现了噪声调频信号的时频特性,为相关雷达干扰机硬件实现提供了参考。

噪声调频干扰;脉冲压缩;DDS;FPGA

现代军事技术的一个重要特点,就是各种武器装备越来越广泛地采用和依赖于无线电子技术。雷达对抗的目的就是通过对雷达的侦察和干扰,获取敌方武器装备、兵力部署、作战指挥等方面的重要情报。

噪声调频干扰具有较宽的干扰带宽和较大的噪声功率,是目前对雷达、通信进行阻塞式干扰中最常用的干扰形式。本文研究噪声调频干扰信号,利用计算机产生其时域波形、频谱。

1 噪声调频干扰原理

噪声调频干扰[1]是一种幅度恒定瞬时频率围绕载频随机变化的一种干扰信号,噪声调频干扰表达式为

(1)

其中,调制噪声u(t)为零均值、广义平稳随机过程;φ为[0,2π]均匀分布,且与u(t)相互独立的随机变量;Uj为噪声调频信号的幅度;ωj为噪声调频信号的中心频率;KFM为调频斜率。

在雷达接收机端,根据产生的噪声调频信号带宽与接收机中放带宽的关系,只有频率在中放带宽内时,接收机才会有输出。若不考虑调谐回路的暂态响应,噪声调频信号通过接收机中放后,将出现一系列幅度相等而宽度和间隔随机变化的矩形脉冲列。而实际谐振回路是有暂态响应的,电路的暂态响应可用脉冲波形的建立时间来衡量。建立时间近似等于中放带宽的倒数。当噪声调频干扰的干扰带宽远大于中放的带宽时,建立时间将远大于中放输出端随机脉冲的宽度和间隔。这样一来随机脉冲将被展宽,许多脉冲将重叠,形成一个幅度随机起伏的连续振荡。中放输出端的噪声调频干扰的脉冲宽度是随机的,这些脉冲叠加后就形成了类似于接收机内部噪声的干扰[2]。 设信号中心频率100 MHz,时宽τ=10 μs,带宽B=30 MHz,调频斜率KFM=5e6,线性调频信号时域波形与功率谱仿真结果如图1和图2所示。噪声调频信号时域波形与功率谱仿真结果如图3和图4所示。

图1 线性调频信号时域波形

图2 线性调频信号功率谱

图3 噪声调频信号时域波形

图4 噪声调频信号功率谱

2 对脉冲压缩雷达的干扰效果

脉冲压缩技术[3]是雷达信号处理的一种基本技术,其过程为通过发射端发射宽脉冲调频信号,提高发射信号平均功率,扩大作用距离,需要对信号内部进行调制,而在接收端进行压缩处理,从而生成窄的时间脉冲,提高距离分辨力。大时宽带宽积信号是通过一个脉冲压缩滤波器来实现脉冲压缩过程的,雷达从发射端发射宽脉冲信号,其载频按一定规律变化,在接收端通过脉冲压缩滤波器对回波进行脉冲压缩,而滤波器的延迟频率特性与发射信号载频的变化规律相反,即发射信号的相频特性与脉冲压缩滤波器是“相位共轭匹配”的,其是输出信噪比最大准则下的最佳线性滤波器。

噪声调频信号频率围绕载频随机变化,如式(2)所示

B/τ=Δf/Δt

(2)

可看出,频率变化经脉冲压缩后会产生时域的时延,所以噪声调频信号经雷达脉冲压缩处理后得到的效果为以初始时间为中心,以τ×Δf/B为变量的随机时间脉冲。

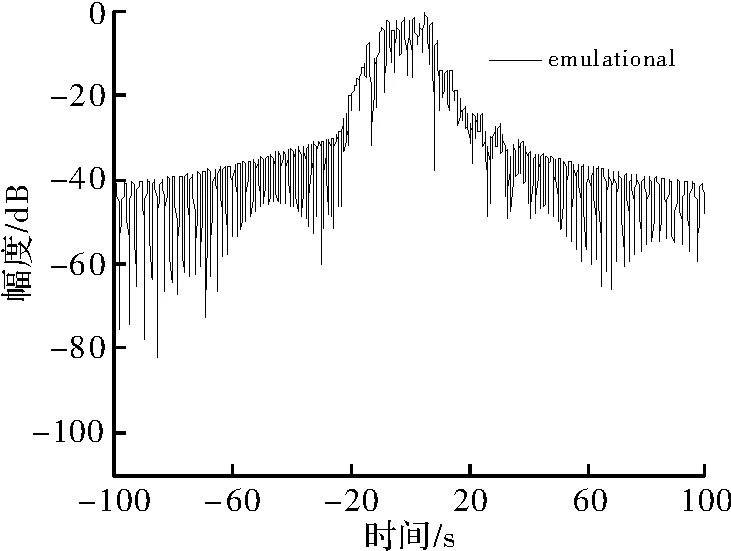

设信号中心频率为100MHz,时宽τ=10μs,带宽B=30MHz,调频斜率KFM=5e6,噪声调频信号对脉冲压缩雷达干扰效果仿真如图5和图6所示。

图5 未经噪声调频干扰脉冲压缩结果

图6 经噪声调频干扰脉冲压缩结果

从上述仿真结果可看出,噪声调频干扰对脉冲压缩雷达可产生较好的压制干扰效果。

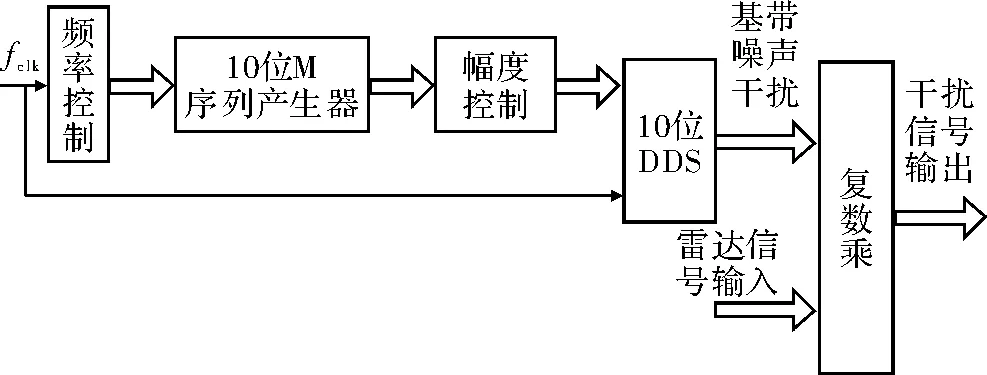

3 噪声调频干扰FPGA实现

产生噪声调频信号的主要流程为:先产生基带的噪声调频信号ejθ(t),将产生的基带噪声调频信号ejθ(t)与雷达信号ejθ复乘得到最终的干扰信号ej[θ+θ(t)]=ejθ·ejθ(t)。其中,基带噪声调频信号主要由DDS技术产生。

DDS(Direct Digital Synthesize)是一种新兴的频率合成技术[4-6]。与传统的直接或间接频率合成技术相比,DDS频率分辨率高、输出相对频带宽、频率捷变速度快、频率捷变时相位连续、频率的合成全部在数字域完成,且便于进行相位、幅度和频率的数字调制,适应数字化信号处理时代的要求。

简化的DDS基本构成框图[7-8]如图7所示,包括参考频率源f0;相位步进寄存器;N位相位累加器;ROM正弦查找表;D/A变换器和滤波器。实际通常将前3部分集成在一块单片电路上。

图7 DDS原理框图

(1)相位步进寄存器。对每个工作脉冲输入的数据K给予暂时存储。

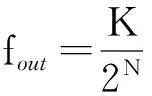

(2)N位相位累加器。相位累加器的功能就是在时钟的作用下不断对频率控制字进行累加,其通常由全加器和相位寄存器组成[9]。其作用是根据从步进寄存器输入的控制字K,以参考频率源输出的时钟频率fclk为采样率,在2π周期内对相位进行采样。若步长为K,采样点数为2N/K,则输出频率fout为

(3)

从而可精确地改变频率,产生待合成的数字信号。

累加器用于执行输入信号的累加过程,其信号范围为0~累加器的满偏值。设累加器的位数为N,则相位累加器的满偏值为2N,将累加器的0状态定义为0相位,累加器的满偏值定义为2π。在累加器进行模为2N运算操作时,即可认为是正弦信号的相位完成了一个周期循环。累加器的溢出频率即为DDS输出信号的频率fout。

(3)ROM正弦查找表。在DDS中,每个相位值必须映射到正弦波上的一点。通过只读存储器中存储的一周期的正弦波及使用相位字作为该ROM的地址来完成这种映射。其将从相位累加器输出的离散N位数值变换成该相位所对应的正弦波幅值。

(4)D/A变换器。D/A变换器把DDS产生的正弦波转换为模拟波形。但输出波形通常均不像正弦波,而是阶梯波,其原因是DAC输出频谱包括采样时钟整数倍的基频镜像。滤波器滤掉有DAC采样处理产生的高阶镜像频率,得到所需的连续频率的正弦波。

图8 FPGA实现噪声调频信号流程框图

通过频率控制模块可控制M序列时钟,即噪声带宽。并通过幅度控制模块可控制M序列大小,即基带调频信号带宽。FPGA噪声调频信号仿真结果,如图9所示。

图9 Modelsim噪声调频信号产生FPGA仿真结果

其中,dinI、dinQ为输入雷达信号数据,doutI、doutQ为输出噪声调频干扰信号数据。将FPGA仿真数据导入Matlab进行时频分析结果如图10所示。

图10 噪声调频信号仿真数据时频分析结果

从图中可以看出,输出噪声的调频信号时间与频率关系呈现无规律的噪声变化。

4 结束语

噪声调频干扰能对雷达产生有效地压制性干扰,配合数字储频技术(DRFM),可产生与雷达信号相参的噪声调频干扰信号,即使经雷达脉冲积累也可达到较好的干扰效果。通过控制产生的噪声调频信号带宽可形成窄带、宽带等不同的噪声调频干扰波形,并可对雷达形成不同的干扰效果。

[1] 赵国庆.雷达对抗原理[M].西安:西安电子科技大学出版社,2005.

[2] 李一兵,赵烨,叶方.末制导雷达抗噪声调频干扰技术的研究[J].弹箭与制导学报,2005(S7):373-376.

[3] 任培宏.脉冲压缩信号的特点、产生及压缩方法[J].电讯技术,1999,39(1):95-97,100.

[4] 刘阳,王雪松,李永祯.噪声调频信号对宽带线性调频雷达的干扰机理[J].现代雷达,2008,30(10):52-56.

[5] 史林,彭燕,杨万海.脉冲压缩雷达干扰仿真分析[J].现代雷达,2003,25(8):37-40.

[6] 杨绍全,张正明.对线性调频脉压雷达的干扰[J].西安电子科技大学学报:自然科学版,1991(3):24-30.

[7] 刘朝军,许人灿,陈曾平.DDS输出信号频谱结构的系统分析[J].国防科技大学学报,2005,27(6):53-56.

[8] 邓岳平,肖铁军.基于 FPGA 的并行DDS信号发生器的设计与实现[J].计算机工程与设计,2011,32(7):2319-2323.

[9] 罗军辉.Matlab7.0在数字信号处理中的应用[M].北京:机械工业出版社,2005.

Research on Noise FM Jamming and its Realization on FPGA

LI Yongsong,LÜ Hao,LIU Yujiao

(School of Electronic Engineering,Xidian University,Xi’an 710071,China)

This paper analyzes the waveform and spectrum of the linear noise FM signal and its effect on the pulse compression radar.Based on the theory above,this paper introduces the realization of noise FM signal on FPGA,analyzes the time-frequency characteristics of the noise FM signal produced on FPGA,and displays the characteristics directly.It can be used as a reference for related radar jammer hardware implementation.

noise FM jamming;pulse compression;DDS;FPGA

2014- 10- 10

李永松(1990—),男,硕士研究生。研究方向:雷达信号处理干扰与抗干扰。E-mail:yongsong_li@126.com

10.16180/j.cnki.issn1007-7820.2015.04.037

TN911.4

A

1007-7820(2015)04-139-04