多晶硅栅对LDMOS-SCR器件ESD防护性能的影响

黄 龙,梁海莲,顾晓峰,董树荣,毕秀文,魏志芬

(1.江南大学 轻工过程先进控制教育部重点实验室,江苏 无锡214122;2.浙江大学 微电子与光电子研究所,浙江 杭州310027;3.西安西电电力系统有限公司,陕西 西安710077)

随着功率集成技术在汽车电子、电源管理及各种高压驱动电路中的广泛应用,高压集成电路产品日益便携化和小型化,而它们的静电放电(electrostatic discharge,ESD)防护已成为影响产品可靠性的主要难题之一[1~2].瞬态高压ESD 脉冲产生的高电场与大电流易导致防护器件发热、金属连线烧毁、硅片融化,甚至被保护电路局部击穿[3-4],因此,高压ESD 防护器件需具备较强的ESD 鲁棒性和耐压能力.横向扩散金属氧化物半导体(laterally diffusion metal-oxide-semiconductor,LDMOS)作为高压大功率器件,常用作片外功率集成电路中的输出管,也可用作ESD 的自防护器件,但需消耗较大的硅片面积.不少研究者提出了内嵌可控硅(silicon controlled rectifier,SCR)的LDMOS(laterally diffusion metal-oxide-semiconductor devices with embedded SCR,LDMOS-SCR)或SCR 的 叠 层 技术[5-7],用于片上功率集成电路的ESD 防护,可以明显改善防护器件的耐压能力和鲁棒性.对于上述叠层技术中的2种ESD 防护器件,目前的研究大多侧重于如何提高维持电压和ESD 鲁棒性;而针对LDMOS-SCR与SCR 器件结构之间的差异,研究多晶硅栅对LDMOS-SCR 器件ESD 防护性能影响的报道尚不多.

鉴此,本文在0.35μm Bipolar-CMOS-DMOS(BCD)工艺下制备了面积相同的LDMOS-SCR 与SCR 2种器件,利用传输线脉冲(transmission line pulse,TLP)测试与Sentaurus器件仿真技术,分析并比较了两者的ESD 防护性能及内部工作机制,证明了多晶硅栅在降低触发电压、增强ESD 鲁棒性方面具有明显效果.

1 器件结构

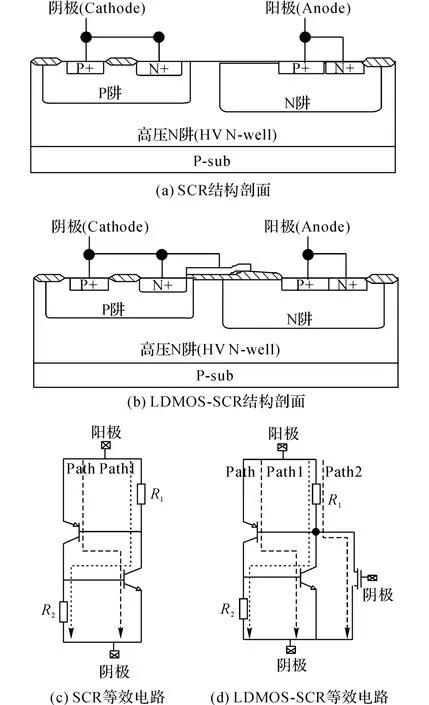

制备的SCR 和LDMOS-SCR 器件的结构剖面如图1(a)、(b)所示.除多晶硅栅的特征结构差异外,两者的版图层次与关键尺寸相同.在ESD 应力作用下,SCR 的等效电路如图1(c)所示,其中R1、R2分别为N 阱与P 阱区域的等效电阻.ESD 电压脉冲使高压N 阱和P 阱形成的反向PN 结雪崩击穿,当雪崩倍增产生的载流子流经R2产生的压降达到0.7V 时,寄生的NPN 管开启;接着,在寄生NPN 和PNP构成的正反馈网络作用下,R1上的压降迅速升至0.7V,使PNP开启,形成的ESD 电流泄放路径如图1(c)中标示的Path所示.

当ESD 应力作用于LDMOS-SCR 时,其工作原理与SCR 相似,区别在于LDMOS-SCR 的多晶硅栅与阴极相连,栅偏置电压为0,此时器件在静态工作时处于关断状态.在ESD 应力作用下LDMOSSCR等效电路如图1(d)所示.LDMOS-SCR开启后的ESD 电流仍主要通过寄生SCR 泄放,泄放路径如图1(d)中标示的Path所示.为考察多晶硅栅对LDMOS-SCR器件ESD 防护性能的影响,下面结合TLP测试和Sentaurus仿真结果分析在ESD 脉冲作用下,SCR 和LDMOS-SCR 临界开启的触发机制、开启后ESD 鲁棒性及其物理机制的变化.

图1 SCR 和LDMOS-SCR器件的结构剖面及等效电路Fig.1 Cross sections and equivalent circuits of SCR and LDMOS-SCR devices

2 结果与讨论

2.1 TLP测试

利用Barth 4002 型TLP 测 试 系 统 对 制 备 的SCR 和LDMOS-SCR 器 件 进 行 测 试.ESD 脉 冲 测试信号的上升时间为10ns,宽度为100ns,步长为1V.每施加一次TLP测试脉冲,同时对器件进行漏电流测试,即在器件两端加一高于工作电压10%的直流电压(本工作中为30V),测试器件的漏电流.2种器件的测试结果如图2所示,其中实心符号代表电流-电压(I-V)特性,空心符号代表对应的漏电流(IL).可以发现,随着器件两端ESD 脉冲电压逐步增大,2种器件依次从未触发开启状态(从A 点到B点)进入到回滞状态(从B 点到C 点)及维持状态(从C 点到D 点);对应的漏电流则从开始时维持在10-11A 量级跃增至10-3A 量级,发生了二次击穿,即ESD 保护器件失效.

图2 SCR 和LDMOS-SCR器件的TLP测试I-V 曲线Fig.2 TLP I-Vcurves of SCR and LDMOS-SCR devices

2.2 多晶硅栅对触发电压的影响

在ESD 保护开启之前(对应图2 的A 点到B点),SCR 器件中的反偏PN 结在ESD 脉冲电压作用下发生雪崩击穿,当少子漂移电流和雪崩倍增产生的载流子电流在电阻上造成的压降达到0.7 V前,反向漏电流形成的电流路径如图1(c)中的Path1所示.然而,对于LDMOS-SCR 器件,在ESD保护开启之前,反向漏电流除具有一条与SCR 开启前相似的路径Path1之外,还因存在多晶硅栅及其覆盖的栅氧,在动态ESD 脉冲作用下易产生界面态陷阱,将导致栅压漂移,从而形成第2条弱反型沟道的触发电流路径Path2,如图1(d)所示.

为分析器件开启前内部电流的形成过程,利用TCAD 工具软件Sentaurus 分别对SCR 和LDMOS-SCR 施加不同强度的ESD 电流脉冲,进行电学特性仿真.在器件阳极施加ESD 电流脉冲,可保证器件的物理模型具有良好的电学收敛性,同时又能较真实地模拟器件在ESD 应力下的电学特性.

在SCR 上施加低强度ESD 电流脉冲(10-7A)时,其内部电子电流密度(J)分布如图3(a)所示,虚线框内的空间耗尽层中没有电流.相同强度的ESD电流脉冲作用于LDMOS-SCR,当作用10ns后,栅压变为0.203V,形成弱反型导电沟道,器件内部的电子电流密度分布如图3(b)所示.可以看出,空间耗尽层中已有较小的电流,表明图1(d)中的电流路径Path2比Path1先开启.

图3 低强度ESD电流脉冲下SCR 和LDMOS-SCR中的电子电流密度分布Fig.3 Electron current density distributions in SCR and LDMOS-SCR under low-level ESD current pulse

当施加的ESD 电流脉冲增至中等强度(10-5A)时,SCR 和LDMOS-SCR 内的电子电流密度分布如图4所示.由图4(a)可知,SCR 的空间耗尽层中已有电流分布,表明路径Path1 开启,SCR 器件被触发.对比图4(a)和(b)可知,LDMOS-SCR 器件内部Path1和Path2 2 条路径均开启,所以电流比SCR 器件大.

图4 中等强度ESD电流脉冲下SCR 和LDMOS-SCR中的电子电流密度分布Fig.4 Electron current density distributions in SCR and LDMOS-SCR under medium-level ESD current pulse

当施加的ESD 电流脉冲继续增大至较高强度(10-4A)时,SCR 和LDMOS-SCR内的电子电流密度分布如图5 所示.此时,电流分布在整个器件内部,表明2种器件内部的寄生SCR 开启,电流主要通过图1(c)、(d)中的路径Path泄放.

比较SCR 与LDMOS-SCR 内部的电流密度分布和电流泄放路径可知,LDMOS-SCR 更易触发.上述分析与TLP测试结果是一致的.由图2可知,LDMOS-SCR 的触发电压仅为34 V,比SCR 下降了约12.5%,表明多晶硅栅可有效降低触发电压.

图5 高强度ESD电流脉冲下SCR 和LDMOS-SCR中的电子电流密度分布Fig.5 Electron current density distributions in SCR and LDMOS-SCR under high-level ESD current pulse

2.3 多晶硅栅对ESD鲁棒性的影响

ESD 鲁棒性受防护器件内部的电流分布影响较大.与ESD 表面电流泄放方式相比,ESD 体电流泄放方式的失效电流较大,ESD 鲁棒性强[8-9].为比较2 种器件的ESD 鲁棒性,分别在SCR 和LDMOS-SCR 的阳极施加相同的ESD 电流脉冲,使它们均进入回滞导通状态(对应图2的B 点到C 点),ESD 电流从阳极流入阴极.为形象地表示器件内部电流的分布状态,在阳极的铝金属与N 型硅接触面的水平线段上,等间距地显示由Sentaurus仿真得到的5条电流分布线,如图6所示.由图6(a)可发现,SCR 中电流线主要集中分布在器件表面区域,形成ESD 表面泄放电流,而分布于表面的电流易造成局部过热,产生电流浪涌效应,引起器件过早失效.图6(b)则表明,LDMOS-SCR 中的电流线分布更趋于器件体内,这是因为多晶硅栅及其覆盖的栅氧减弱了LDMOS-SCR 器件横向电场的表面集中分布情况,促使电场趋于纵向分布,从而形成ESD体泄放电流,因此能更好地抑制电流浪涌效应,提高器件的ESD 鲁棒性.

图6 SCR 和LDMOS-SCR中的电流线分布Fig.6 Current line distributions in SCR and LDMOS-SCR

在SCR 和LDMOS-SCR的阳极分别施加相同的高强度ESD 电流脉冲时,两者晶格温度(T)分布的仿真结果如图7 所示.可以看出,SCR 的表面附近存在一个高温热点,最高温度可达1 000K 左右;而LDMOS-SCR 的温度分布相对比较均匀,最高温度仅约450 K.与LDMOS-SCR 相比,SCR 表面高温热点的形成一方面是由于SCR 在深度回滞后的大电流作用下,电流线主要集中分布在SCR 表面,易造成金属连线融化;另一方面,如图8所示,SCR中电场集中分布在器件表面由P 阱和高压N 阱形成的PN 结附近,最大可达1.3×106V/cm,成为PN 结反向击穿最脆弱的部分,故晶格温度最高.然而,对于LDMOS-SCR,因其多晶硅栅能抑制电场趋于表面分布,所以该器件体内晶格温度较低.可见,LDMOS-SCR 中的多晶硅栅具有减缓晶格温度快速上升的作用,进一步证明了多晶硅栅有助于提高器件的ESD 鲁棒性.

图7 SCR 和LDMOS-SCR中的晶格温度分布Fig.7 Lattice temperature distributions in SCR and LDMOS-SCR

图8 SCR 和LDMOS-SCR中Y=9μm 处的电场分布Fig.8 Electric field distributions in SCR and LDMOSSCR at Y=9μm

实验上常用TLP 测试得到的失效电流大小来衡量ESD 鲁棒性的强弱.由图2给出的样品电流与漏电流的关系可看出,当SCR 的样品电流为4.05 A 时,其漏电流突然跃增到毫安量级,因此SCR 的失效电流为4.05A.对于LDMOS-SCR,其失效电流为5.14A,比SCR 提高了约27.0%,验证了具有多晶硅栅的器件ESD 鲁棒性更强.

3 结 语

基于BCD 工艺 制 备 了SCR 和LDMOS-SCR 2种器件,利用TLP 测试研究了它们的ESD 防护特性.结果表明,具有多晶硅栅的LDMOS-SCR 触发电压低,失效电流高,ESD 鲁棒性强.利用器件仿真比较了SCR 和LDMOS-SCR 内部电流密度分布、电流泄放路径和泄放方式、晶格温度分布的差异,阐释了多晶硅栅改善ESD 防护性能的物理机理,为高压ESD 防护器件设计版图层次的选择提供了有益的参考.

(

):

[1]HUANG C Y,CHIU F C,CHEN Q K,et al.An SCRIncorporated BJT device for robust ESD protection with high latch up immunity in high-voltage technology[J].IEEE Transactions on Device and Materials Reliability,2012,12(1):113-123.

[2]SHRIVASTAVA M,GOSSNER H.A review on the ESD robustness of drain extended MOS devices[J].IEEE Transctions on Device and Materials Reliability,2012,12(4):615-624.

[3]李梅芝,陈星弼.栅压对LDMOS在瞬态大电流下工作的温度影响[J].半导体学报,2008,28(8):1256-1260.LI Mei-zhi,CHEN Xing-bi.Influence of gate voltage on temperature of LDMOS under ultra-high transient currents[J].Chinese Journal of Semiconductors,2008,28(8):1256-1260.

[4]朱科翰,董树荣,韩雁,等.不同栅压下NMOS器件的静电防护性能[J].浙江大学学报:工学版,2010,44(1):142-144.ZHU Ke-han,DONG Shu-rong,HAN Yan,et al.ESD protection of NMOS device at different gate bias[J].Journal of Zhejiang University:Engineering Science,2010,44(1):142-144.

[5]LIU Z W,Liou J J,DONG S R,et al.Silicon-controlled rectifier stacking structure for high-voltage ESD protection applications[J].IEEE Electron Devices Letters,2010,31(8):845-847.

[6]KER M D,LIN K H.The impact of low-holding-voltage issue in high-voltage CMOS technology and the design of latch up-free power-rail ESD clamp circuit for LCD driver Ics[J].IEEE Journal of Solid-State Circuits,2005,40(8):1751-1759.

[7]MA F,ZHANG B,HAN Y,et al.High holding voltage SCR-LDMOS stacking structure with ring-resistance-triggered technique[J].IEEE Electron Device Letters,2013,34(9):1178-1180.

[8]CHANG W J,KER M D.The impact of drift implant and layout parameters on ESD robustness for on-chip ESD protection devices in 40-V CMOS technology[J].IEEE Transactions on Device and Materials Reliability,2007,7(2):324-332.

[9]JIANG L L,FAN H,HE C,et al.A reduced surface current LDMOS with stronger ESD robustness[C]∥2012IEEE 11th International Conference on Solid-State and Integrated Circuit Technology.Xi’an:IEEE,2012:1-3.