FPGA高速并行m序列的设计

李 荷,赵贤明,郝志松

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

FPGA高速并行m序列的设计

李 荷,赵贤明,郝志松

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

针对在FPGA内部产生高速m序列时,处理时钟频率远低于数据生成速率的问题,采用延迟法、等效法和代换法3种方式,设计了并行m序列产生的并行结构,并在FPGA上进行了实现。经过测试,生成的并行m序列完全符合标准格式要求。这种并行结构在高速通信系统中的加解扰、误码测试和编译码测试等环节取得了较好的应用效果。

PN序列;并行结构;高速通信

0 引言

随着硬件规模的增加、功能的丰富和接口速率的加快,使FPGA在信号处理实现的过程中发挥的作用越来越大。特别对于雷达信号处理或高速数据传输领域的高速信号处理系统,要求处理的实时性强、处理速度快,所以更多地使用FPGA实现[6-8]。

信号处理的速度和吞吐率都非常快的高速信号处理系统中,处理速度一般达到300 MHz以上,吞吐率达到Gbps量级甚至10 Gbps量级。此时FPGA的处理速度已经超过了FPGA本身能够稳定工作的最高频率,因此需要采用并行处理方法对信号处理算法进行改进,降低FPGA的工作频率。但是这种改变一般是以牺牲硬件资源为代价的。

在FPGA内产生高速伪随机序列是数据传输领域里经常需要的功能[4]。但是当处理时钟频率低于伪随机序列输出速率要求时,必须并行产生伪随机序列。

要求实现输出速率为1.2 Gbps的伪随机m序列,但在FPGA中,稳定工作的处理主频只有150 MHz,因此进行了m序列产生算法或实现结构的改进。改进后的m序列生成算法不同于以往并行算法,使硬件资源成倍增加,而是在硬件资源增加不大的情况下,实现了1.2 Gbps的并行m序列的输出。

这种并行实现算法也可应用到加解扰等环节,为如何在满足速率要求的情况下,尽量节省硬件资源提供了参考方案。

1 m序列产生方法

m序列具有类似随机噪声的某些统计特性,同时又能够重复产生。其中m序列是常见的一种随机序列,最长线性反馈移位寄存器序列的简称[1,2]。对于n阶线性反馈移位寄存器,最长周期为2n-1。m序列具有“1”“0”数目均衡性、移位相加序列不变、游程均匀等特性。

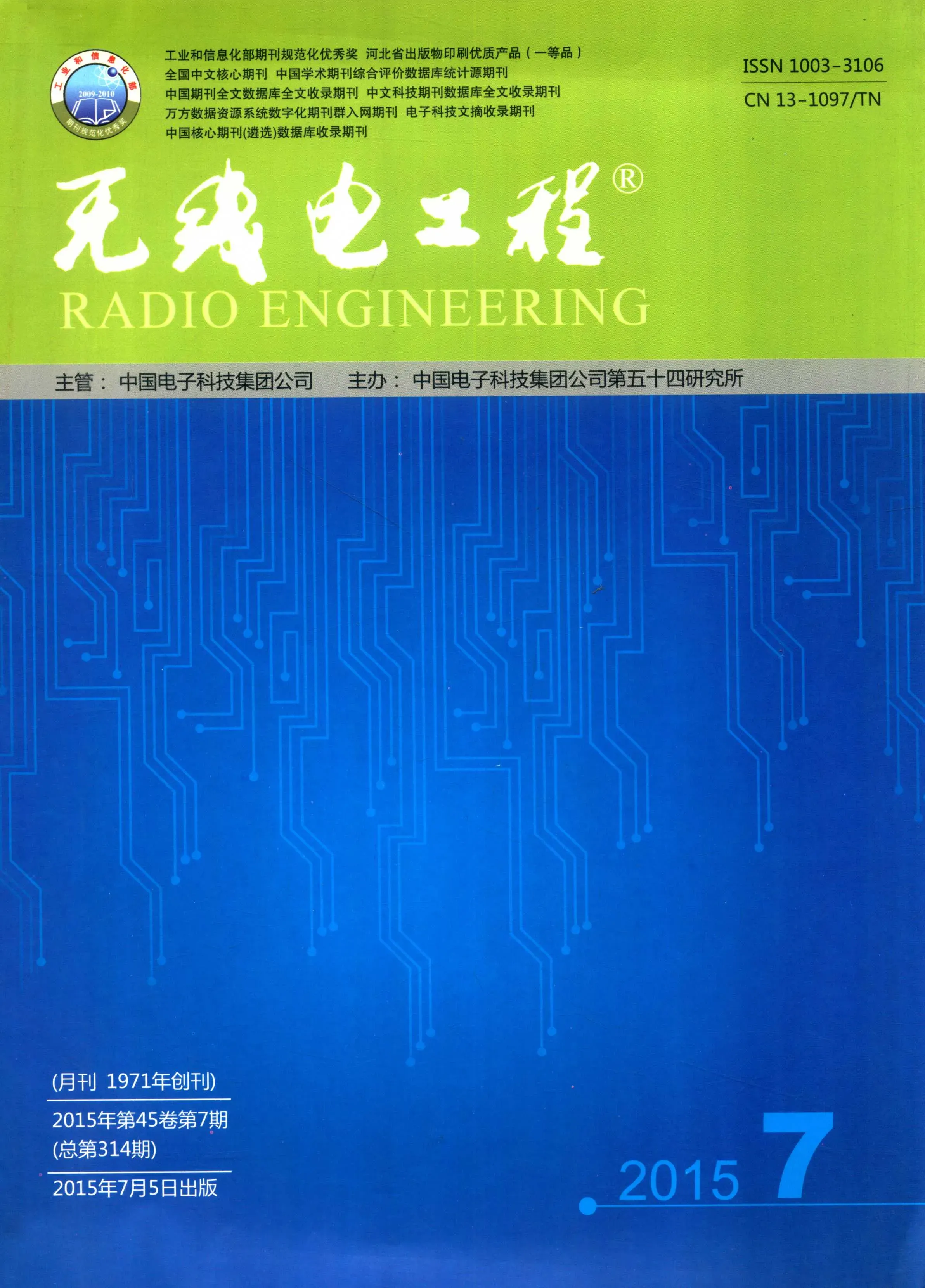

关于m序列的产生,一般先确定需要产生的阶数,再去查本原多项式,根据本原多项式确定移位寄存器结构。如确定产生一个8阶的伪随机序列,查到8阶的本原多项式为x7+x3+1,根据多项式生成了PN7的m序列的移位寄存器结构,如图1所示。

图1 PN7移位寄存器结构

2 m序列的几种并行实现方法

对于1.2 Gbps的伪随机序列,在工作时钟为150 MHz的FPGA内,需要采用8路并行的方式实现。

判断8路并行实现的结果是否正确,可以检查8路并行后的输出结果与把单路序列8分路后的结构是否一致。

2.1 延迟法

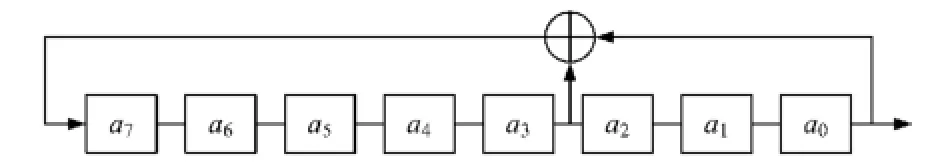

延迟法是利用一个PN7移位寄存器产生m序列后,进行8分路,再对各路进行不同时钟拍数的延时。

伪随机序列具有隔位输出,序列不变的性质[3],即把序列的所有奇数位置或偶数位置的数删除,还是原序列,只是初始相位发生变化。实现结构如图2所示。

图2 延迟法寄存器实现结构

2.2 等效法

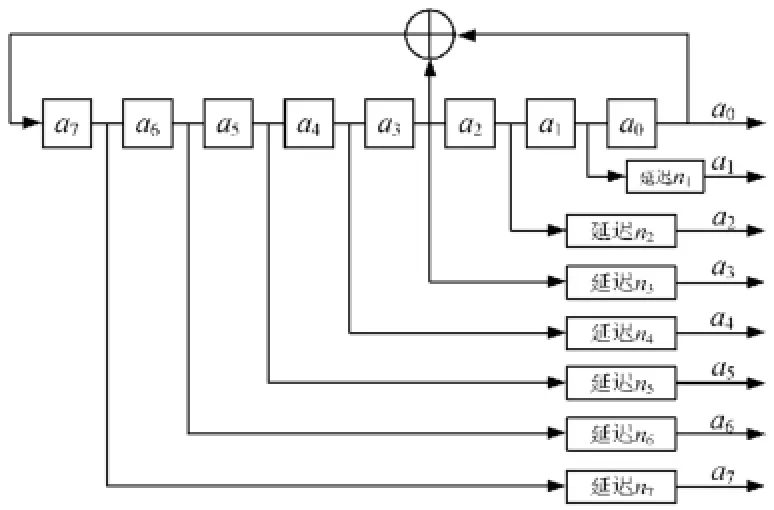

等效法是利用多组移位寄存器并行产生[5]。把8路并行后的伪随机序列看成8路初始相位不一样的独立的序列,分别用8组移位寄存器实现。等效法寄存器实现结构如图3所示。

图3 等效法寄存器实现结构

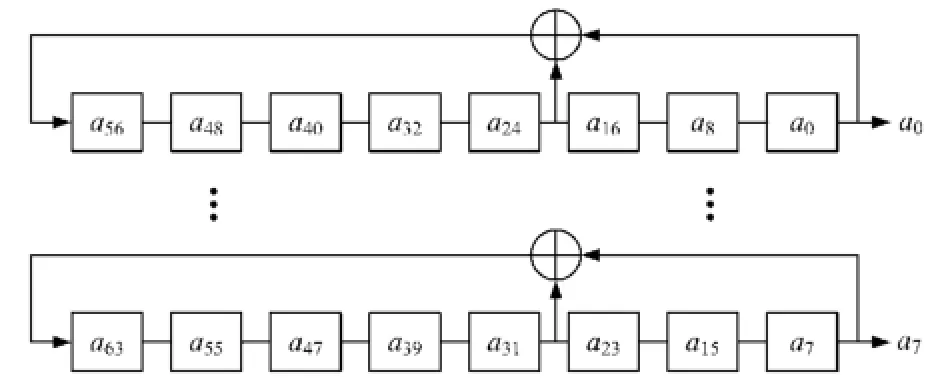

2.3 代换法

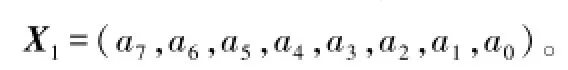

m序列8路并行后,在T0的时刻输出1组8 bit的数据,设这组数据为数组X1:

在T1时刻输出下一组8 bit数据,设这组数据为数组X2:

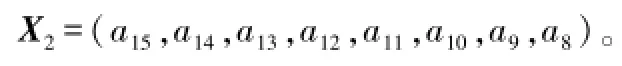

根据序列的生成多项式,可以得出X2和X1的对应关系为:

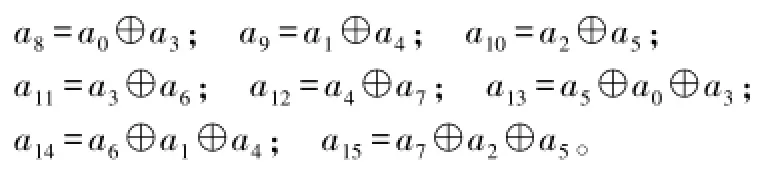

由于在每一时钟节拍,序列的生成多项式不会发生变化,因此上面的对应关系不失一般性。即在时刻Tn,输出数组为:

在时刻Tn+1,输出数组为:

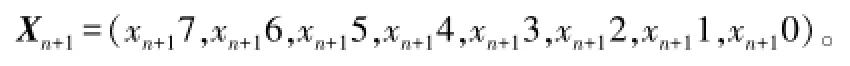

Xn+1和Xn有如下对应关系:

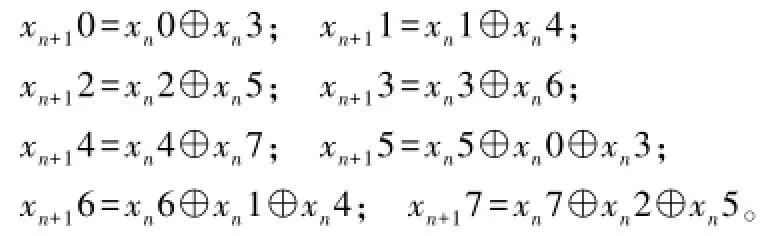

根据以上对应关系,可以得出移位寄存器结构如图4所示。

图4 代换法的实现结构

3 3种产生方法的比较

3种伪随机序列的产生方法在FPGA的信号处理平台上实现,并行后的总速率均可达到1.2 Gbps的使用要求。

因为D触发器的资源在FPGA内部属于紧缺的硬件资源,异或运算使用查找表实现,相对宽松,所以在进行消耗硬件资源对比时,只考虑D触发器的占用情况。在速率满足使用条件的前提下,延迟法使用D触发器445个,等效法使用D触发器64个;代换法使用D触发器8个,硬件资源仅为等效法的1/8,为延迟法的1/55。

在硬件模块的移植方面,由于等效法使用了8个结构完全一样的移位寄存器,在确定初相、数据顺序和分合路模糊等方面存在一定的困难;而使用代换法设计的序列产生模块移植起来容易得多。因此选择代换法作为优先考虑的实现算法。

4 m序列的测试

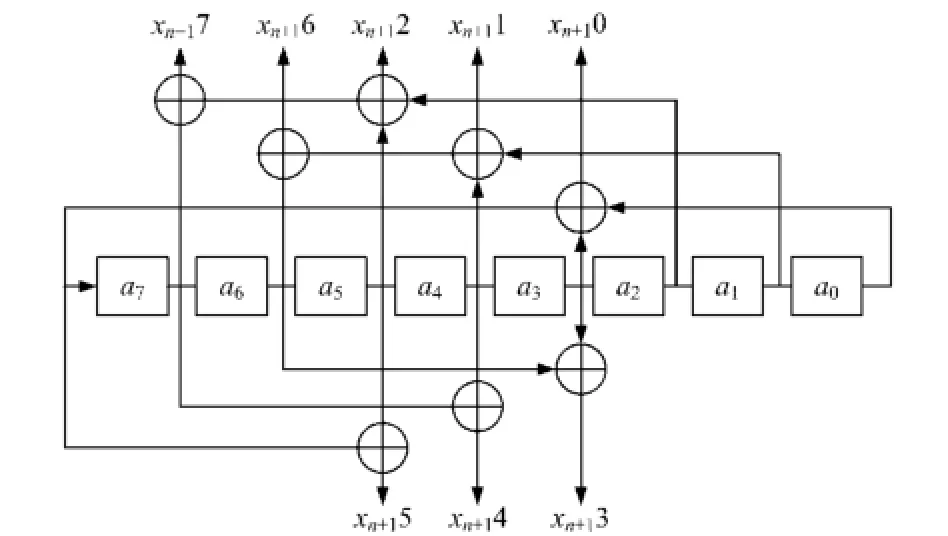

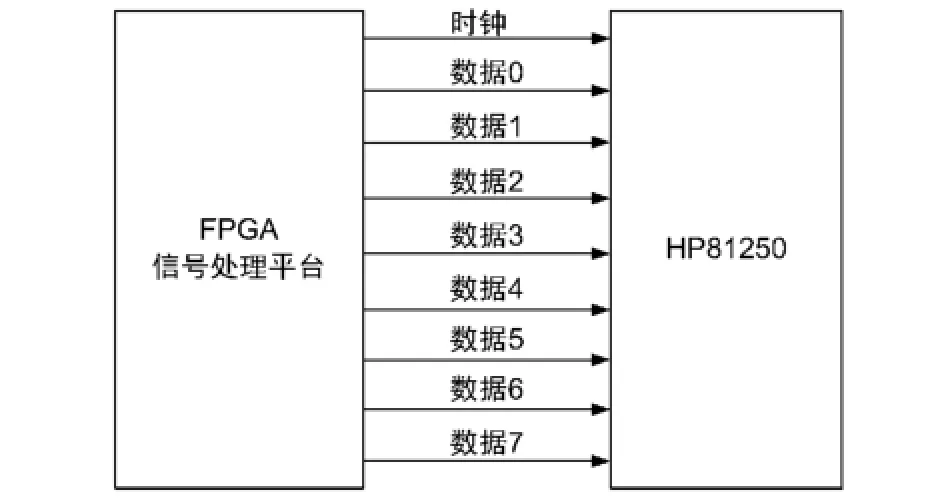

伪随机序列的测试采用安捷伦公司的并行误码测试仪HP81250进行。测试连接关系如图5所示。

图5 多组移位寄存器实现结构

FPGA信号处理平台是高速并行伪随机序列信号产生和传输的硬件载体。采用代换法产生并行信号后,处理平台通过8路并行的LVDS信号,把伪随机序列输入到并行误码测试仪HP81250中;同时也输出1路同步时钟信号到误码测试仪。误码测试仪首先把时钟同步到时钟信号上,然后对输入的伪随机信号进行同步,同步后对8路信号进行总的误码率统计。

时钟速率为150 MHz,误码测试仪内伪随机序列生成多项式为x7+x3+1,经过1小时的误码统计,总误码率为零。证明FPGA硬件平台输出的并行伪随机序列和误码测试仪内的标志序列一致。

5 结束语

通过对m序列的分析和理论推导,创新地设计了2种伪随机序列的并行实现算法,可以使序列输出速率远高于FPGA内部的处理时钟。测试结果表明,推导和实现的结果完全正确。

通过比较2种实现方法在处理速度、硬件资源和可移植性等方面的差异,推荐了代换法作为高速m序列的首选设计方案。

本文算法可以应用于通信系统的加解扰、误差测试、编译码测试等功能模块,在大幅提高这类模块的数据吞吐率的同时,尽量节省不必要的硬件资源浪费。本文算法的直接使用节省了设计人员的推导和试验时间。

[1]樊昌信,曹丽娜.通信原理(第6版)[M].北京:国防工业出版社,2008:379-393.

[2]陶亚雄.现代通信原理与技术[M].北京:电子工业出版社,2012:245-262.

[3]郝志松.星间太赫兹通信发射系统初步方案设计[J].无线电通信技术,2012,38(3):34-35.

[4]王赛宇.卫星带宽功率双重受限情况下的高效传输方案[J].无线电通信术,2013,39(5)43-46.

[5]郝志松.极化干扰对星地遥感数据传输影响分析[J].无线电通信技术,2012,42(4):62-64.

[6]陈 澄,张茂青,崔秀美.基于FPGA的可编程M序列发生器的设计[J].工业控制计算机,2013,26(6):15-16.

[7]孙玉花.伪随机序列的性质及其应用研究[D].西安电子科技大学博士学位论文.西安:西安电子科技大学,2013:14-16.

[8]陈志贵.一种实现M序列码的电路设计[J].数字通信,2013,40(4):53-55.

Design of FPGA High-speed Paralleling m Sequence

LI He,ZHAO Xian-ming,HAO Zhi-song

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

To resolve the problem of processing clock frequency far below data generation rate in generating high-speed m sequence in FPGA,this paper adopts three methods of delay method,equivalent method and substitution method to design the parallel structure for generating paralleling m sequence and implements it on FPGA.The test results show that the generated paralleling m sequences fully meet the standard format requirements.This parallel structure achieves better application effects in the tests of scrambling and descrambling,BER,and coding and decoding in high-speed communication system.

PN sequence;parallel structure;high-speed communication

TN76

A

1003-3106(2015)07-0024-03

10.3969/j.issn.1003-3106.2015.07.07

李 荷,赵贤明,郝志松.FPGA高速并行m序列的设计[J].无线电工程,2015,45(7):24-26.

李 荷女,(1979—),工程师。主要研究方向:卫星通信总体技术。

2015-04-16

郝志松男,(1978—),高级工程师。主要研究方向:卫星数据传输技术。