4G视频传输模块的硬件设计与信号完整性分析

黄学达,付仕明

(1.重庆邮电大学 重邮信科通信技术有限公司,重庆 400065;2.重庆第二师范学院 数学与信息工程学院,重庆 400065)

4G视频传输模块的硬件设计与信号完整性分析

黄学达1,付仕明2

(1.重庆邮电大学 重邮信科通信技术有限公司,重庆 400065;2.重庆第二师范学院 数学与信息工程学院,重庆 400065)

提出了一种基于TMS320DM6467T平台的嵌入式4G视频传输模块的硬件方案,该方案充分利用4G网络的高带宽,可以实现视频信号的快速传输。对方案的硬件设计进行了深入的探讨,分析了各个功能模块。介绍信号完整性分析的重要性,提出4G视频传输模块的信号完整性设计方案。应用HSPICE软件和IBIS模型对硬件电路板进行仿真分析,有效地解决了系统的LPDDR2接口电路中出现的反射、串扰等信号完整性(SI)方面的问题,提高了信号眼图质量,充分保证了电路板设计的质量和信号传输速度,满足视频信号传输的要求。

第四代移动通信;视频传输;LPDDR2;信号完整性

随着移动通信的飞速发展,中国三大电信运营商在2013年12月获得4G牌照,在之前建设了LTE 4G试验网的基础上,大力推荐LTE的网络建设,4G 移动通信网络的下行数据传输速率最大150 Mbit/s,上行数据传输速率最大50 Mbit/s。在视频监控行业中,逐渐开始采用4G网络进行视频传输,依托4G移动通信网络,极大地方便了监控的视频信号事实传输。中国移动主要运营TDD-LTE网络,中国电信和中国联通主要运营FDD-LTE网络,采用4G网络进行视频传输模块不但支持三大运营商的两种制式的LTE网络,同时支持WCDMA,TD-SCDMA和GSM,即可满足4G网络覆盖比较好的城市及周边,也可用于仅覆盖了GSM的偏远地区。

4G视频传输模块采用LPDDR2内存,从PCB设计角度来讲,要做到严格的时序匹配,以满足信号完整性,需要考虑PCB的叠层、信号走线阻抗、互联拓扑、时延匹配、串扰、电源完整性和时序。因此必须对4G视频传输模块的PCB叠层结构、布线约束等进行正确设计,并在PCB投板前进行仿真,根据仿真结果指导PCB的设计和生产,以达到信号完整性的要求。

本文主要讨论4G视频监控模块的LPDDR2 硬件设计和信号完整性分析。

1 4G视频传输模块介绍

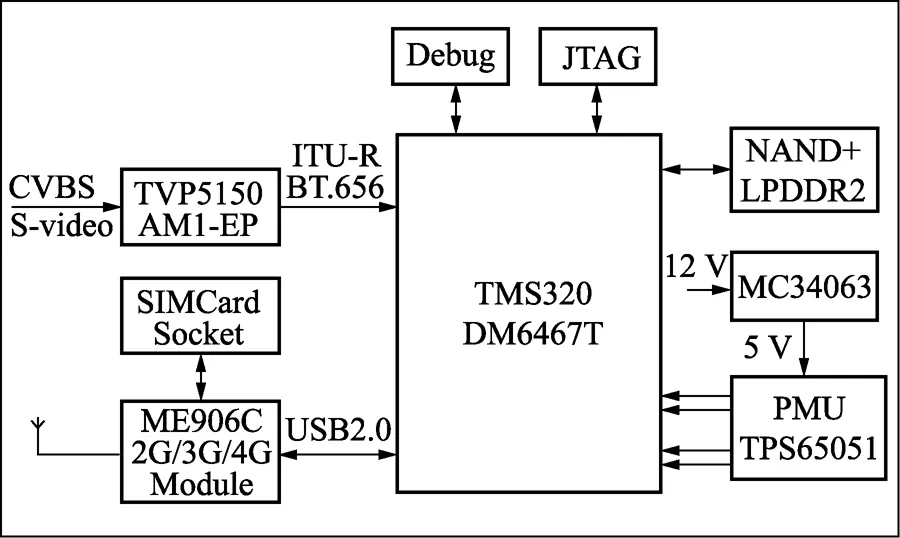

如图1所示,4G视频传输模块采用TI公司的多媒体专用System-on-Chip(SoC)芯片TMS320DM6467T;采用TI公司的视频解码芯片TVP5150AM1-EP,支持双路CVBS模拟视频输入或者1路S-VIDEO视频输入;存储器单元采用HYNIX公司的4Gbyte NAND FLASH+2Gbyte LPDDR2的MCP,集成度高,占用面积小,功耗低;电源管理采用ON的BUCK DCDC MC34063,TI的6通道PMU TPS65051提供系统需要的 3.6 V, 3.3 V,1.8 V等电源;4G通信模块采用华为公司成熟稳定的ME906C[1]。

使用该方案设计的4G视频传输模块相比现有的视频传输模块的优势主要有:集成度高,开发周期短,性能稳定;支持4G LTE网络,无线传输速率高;支持LTE-TDD、LTE-FDD、WCDMA、TD-SCDMA、GSM五模十四频,可以满足中国移动、中国电信、中国联通、日本软银、美国AT&T等国内外运营商的网络覆盖。

图1 4G视频传输模块硬件框图

1.1 多媒体处理器

采用TI公司达芬奇技术的数字多媒体专用SoC处理器TMS320DM6467T,由500 MHz的ARM926EJ-S与1 GHz的C64x+DSP组成,ARM主要负责整个系统的控制,控制TVB5150AM1-EP完成模拟视频的采集、解码并送入DSP,控制4G通信模块完成数据的接收和发送;DSP完成视频信号的编码、压缩等图像处理工作,高达8 000 MI/s的指令数;2个可编程高清视频图像协处理器(HDVICP)适用MPEG2,MPEG4 SP/ASP,VC1,H.264等视频压缩编解码算法;2个150 MHz视频端子接口(VPIF),支持双路8 bit SD(BT.656)与单路16 bit HD(BT.1120)视频采集和显示通道;一个视频数据转换器(VDCE),完成YUV422格式的视频转换成YUV420格式,便于进行视频信号的压缩编码处理[2]。

1.2 视频采集单元

采用TI公司的高性能增强型视频解码芯片TVP5150AM1-EP,支持2路CVBS或1路S-video接口,内部集成9 bit高精度ADC转换器,将接收到的NTSC,PAL,SECAM模拟视频信号转换为ITU-R BT.656送入TMS320DM6467T进行压编码处理,外接14.318 18 MHz的晶体振荡器,为系统提供时钟源,多媒体处理器通过I2C接口实现对TVP5150AM1-EP的控制[3]。

1.3 存储器单元

存储器采用HYNIX的4 Gbyte(×16) NAND +2 Gbyte(×32) LPDDR2的MCP,型号是H9TA4GH2GDMCPR,162-ball FBGA封装,集成度高,占用面积小,功耗低。其中LPDDR2的Layout必须严格按照相关规范设计,并进行仿真等信号完整性分析,确保设计生产出的电路板能满足CPU高速信号传输的需求[4]。

1.4 电源管理单元

采用ON的高效率BUCK DCDC MC34063实现DC 12 V转成DC 5 V,将DC 5 V作为TI公司的TPS65051的输入,输出系统需要的3.3 V,1.8 V,1.2 V等电源需求,TPS65051集成2路BUCK DCDC,4路LDO, 各路输出电源电压采用精密电阻分压方式实现,无需软件编程,控制灵活,另外就是TPS65051输出的RESET信号还作为TMS320DM6467T的系统上电复位信号,确保了系统顺利上电,软件加载成功[5]。

其中,摄像头数量多、监控区域范围大、系统架构复杂、业务面宽等是软件平台面临的主要技术问题,可归纳为如下几点:

1.5 4G通信模块

4G通信模块采用华为公司的ME906C LTE M.2接口模块,模块尺寸大小为42 mm×30 mm×2.3 mm,采用3.3 V直流供电,支持频段为LTE TDD的Band38,Band39,Band40,Band41,LTE FDD的Band1,Band3,WCDMA的Band1,Band2,Band5,TD-SCDMA的Band34,Band39,GSM/GPRS/EDGE的900 MHz/1 800 MHz/1 900 MHz,主要满足中国移动的五模要求,也适用中国联通的2G/3G/4G网络和中国电信的4G网络。另外支持GPS/GLONASS,便于在野外使用时的卫星定位。该模块下行/上行速率最大都在LTE FDD模式,支持 100 Mbit/s, 上行50 Mbit/s,20 Mbit/s带宽的Cat3模式[6]。

2 信号完整性分析

4G视频传输模块的信号完整性分析主要是考虑高速信号的阻抗设计,信号回路设计以及LPDDR2的走线长度规则[7-9]。

2.1 PCB阻抗分析

由于4G通信模块采用集成的模块,只需要考虑好2G/3G/4G的天线设计,电源供电等方面,重点是考虑TMS320DM6467T的LPDDR2走线,以及LPDDR2的信号完整性分析。LPDDR2的传输线阻抗必须是恒定连续的,单端信号走线按照50 Ω设计,比如ADDR,CMD,CNTRL等,而对于差分信号,按照差分100 Ω进行设计,比如CLOCK和DQS信号。

PCB的阻抗与走线宽度、铜箔厚度、间距、PCB介质厚度、介电常数等因素有关,在进行Layout前,根据规划的LPDDR2各信号线的走线层数,采用Polar公司的SI9000工具进行阻抗设计,初步得出PCB的表层阻焊油厚度、各层铜箔厚度、介质厚度等信息,交PCB板厂进行确认。

2.2 信号回路分析

数字电路信号回流一般是借助于地和电源平面来完成,高速信号和低速信号的回流路径是不同的,低速信号(小于或等于10 MHz)回流是选择阻抗最短路径,一般也就是到信号源最短的路径进行。而在高速信号下,信号的返回路径不再按照阻抗最短路径去回流,而是按照阻抗最小的面积去回流。

低速信号的回流路径是沿着最短路径返回信号源端,高速信号的回流是沿着传输线进行的,因为沿着传输线返回,则信号环路包含的面积最小。在4G视频传输模块主板的PCB中,高速信号的回流路径可能是与信号同层,也可能是相邻层。

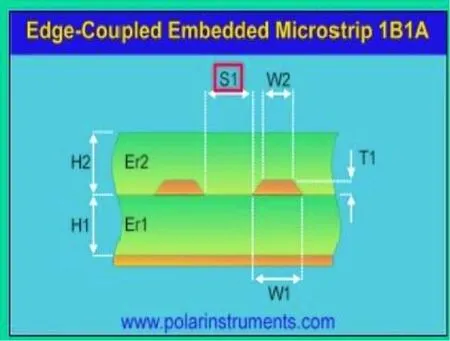

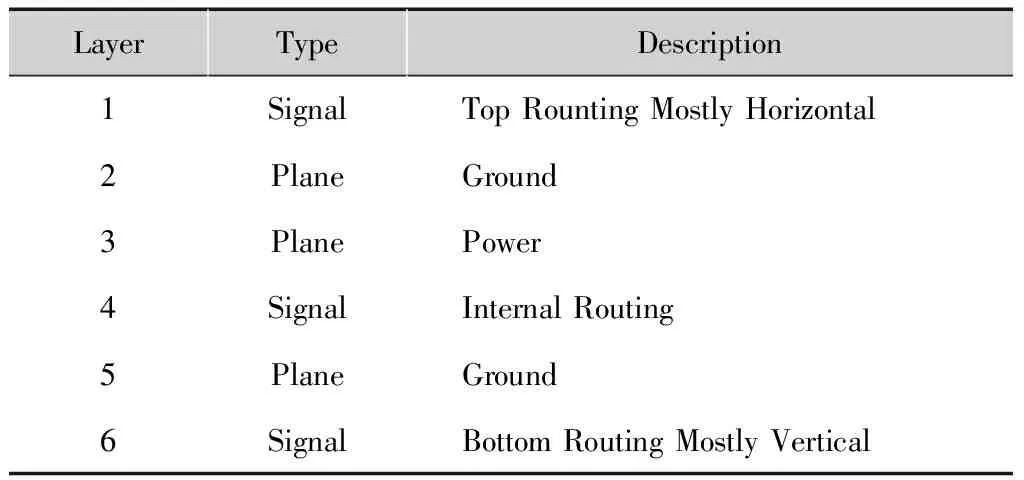

如图2所示,S1为同一平面上两条平行信号线的距离,H1,H2为信号线到参考平面的距离。当S1>H1的时候,信号线与参考平面的包含面积最小,所以高速信号回流路径在参考平面上4G视频传输模块PCB设计时,提供回流路径的参考平面对应信号为地。当S1 图2 2条平行的PCB走线(截图) 2.3 LPDDR2走线规则 由于主芯片TMS320DM6467T是0.8 mm pitch的FBGA装,MCP是0.6 mm pitch的BGA封装,采用6层板。1阶孔设计,最小线宽和线距都是4 mil(1 mil=0.002 54 cm)。PCB叠层设计见表1。 表1 PCB叠层示意图 LayerTypeDescription1Signal TopRountingMostlyHorizontal2Plane Ground3Plane Power4Signal InternalRouting5Plane Ground6Signal BottomRoutingMostlyVertical 按照TMS320DM6467T DDR2走线要求,LPDDR2与TMS320DM6467T的DDR2 Controller之间的器件布局不能超过1 750 mil,否则会导致DDR2信号仿真眼图恶化,降低信号的传输质量,DDR2信号走线区域禁止有其他信号线,并且与其他信号线之间最好有GND或者GND平面隔离。DDR2的CLOCK信号线可以串接最大10 Ω的端接电阻,地址、控制以及数据信号可以串接22 Ω的端接电阻,可以减小EMI的风险,满足信号完整性和消除信号过冲[10]。 为了获得比较高的数据传输速率,DDR2信号走线必须严格满足以下要求: 1)DDR2的差分时钟信号线之间中心距最大不超过2倍线宽; 2)DDR2的差分时钟信号与地址、控制、数据信号之间中心距为最小4倍线宽; 3)DDR2的DQS信号走线中心与其他信号走线中心之间距离为最小4倍线宽; 4)DDR2的差分时钟与地址、控制信号之间的长度误差不超过±50 mil; 5)DDR2的DQS与DQ信号之间的长度误差不超过 ±50 mil; 6)DDR2的32 bit DQ分为4 byte,各字节内部走线长度不超过±50 mil。 采用Synopsys的HSPICE软件(Windows版)进行仿真计算,使用Synopsys的CustomExplorer软件查看仿真结果,使用文本编辑器UltraEdit进行HSPICE脚本编写。 3.1 仿真模型介绍 板级传输线包括package内部走线和PCB走线两部分,输入信号经过pad-铜线-finger-基板走线-ball-PCB走线,到外部的LPDDR2芯片,完成板级传输,如图3所示。 图3 板级传输线示意图 激励源采用TI公司提供的“stimulus_lpddr2_3_1.sp”,内部DIE的IBIS模型由TI公司提供“mif6647x_1p2v.ibs”,waibu LPDDR2芯片的IBIS模型采用HYNIX提供的“u80m_wt.ibs”,package参数由TI提供,为RLC参数,PCB模型采用W-element模型,HSPICE根据PCB叠层结果计算出RLC参数[11]。 3.2 仿真结果分析 4G视频传输模块的仿真中,主要分析电源部分对信号的影响以及信号走线的眼图。表2和表3分别为理想电源和真实电源情况下仿真结果。 表2 理想电源仿真结果 DRIVEModel信号延迟时间/psByte0Byte1Byte2Byte3CA5X(48Ω)fast670691641∗719676slow631∗650∗612∗671613∗6X(40Ω)fast670689640∗729700slow640∗658614∗685629∗ 表3 真实电源仿真结果图 DRIVEModel信号延迟时间/psByte0Byte1Byte2Byte3CA5X(48Ω)fast615∗∗687615∗∗705667∗∗slow584∗∗652∗572∗∗644624∗∗6X(40Ω)fast610∗∗684603∗∗717693∗∗slow588∗∗661574∗∗665647∗∗ 表2~3中不带标识符号的表示低风险,“*”表示中等风险,“**”表示高风险。分别采用5X,6X两种驱动强度进行仿真分析,在快速和慢速两种模型进行各字节的时延分析,发现6X驱动强度在fast模型较为合适,真实电源的仿真结果差于理想电源,特别是Byte0和Byte2两个字节处于高风险等级。Byte0和Byte2的眼图如图4所示。 图4 Byte0和Byte2眼图(截图) 通过眼图观察,发现信号之间的skew较大,对DDR接收端来说就是有的信号先到,有的信号晚到,需要调整信号的长度,使各字节的信号满足等长要求,调整LPDDR2的电源平面,增加去耦电容,最后各字节的仿真眼图如图5所示,达到LPDDR2走线的设计要求。 本文详细介绍了基于TMS320DM6467T平台的4G无线视频传输模块,分析了视频传输模块的硬件设计方案,信号完整性设计准则,应用HSPICE软件与IBIS模型,对设计好的PCB进行仿真分析,改善了LPDDR2信号走线上的信号反射和串扰,优化了眼图的形状,确保了PCB走线的设计质量以及LPDDR2信号的传输速度满足要求,提高4G视频传输模块的PCB设计的成功率。设计生产出的PCB电路板,经过软件开发和系统测试,电路板满足设计需求,促使该产品被很快推向市场,取得不错的经济效益。 [1] 夏振华,张正炳. 基于3G移动通信的无线视频监控的设计[J]. 电视技术,2010,34(3):94-95. [2] TI.TMS320DM6467T digital media system-on-chip datasheet[EB/OL].[2015-06-20]. http://www.farnell.com/datasheets/1520215.pdf. [3] TI. TVP5150AM1-EP Ultralow-Power NTSC/PAL/SECAM video decoder datasheet[EB/OL] .[2015-06-20]. http://www.alldatasheet.com. [4] Hynix. H9TA4GH2GDMCPR series datasheet version 0.1[EB/OL].[2015-06-20]. http://www.hkmjd.com/proclass-read-id-1081621.html. [5] TI. TPS65051 datasheet[EB/OL] .[2015-06-20]. http://www.alldatasheet.com/view.jsp?Searchword=TPS65051RSMT. [6] 华为公司.HUAWEI ME906C LTE M.2 module hardware guide[EB/OL] .[2015-06-20]. http://www.4gltemall.com/huawei-me906c-4g-lte-m-2-ngff-module.html. [7] 黄帅,许雪梅,徐蔚钦,等. 嵌入式3G无线视频监控系统硬件设计与信号完整性分析[J]. 计算机应用,2010,30(9): 2535-2540. [8] JOHNSON H, GRAHAM M.高速数字设计[M]. 北京:电子工业出版社, 2004. [9] BOGATIN E.信号完整性分析[M]. 北京:电子工业出版社, 2004. [10] TI.Implementing DDR2 PCB Layout on the TMS320DM644x DSP[EB/OL] .[2015-06-20]. http://www.ti.com.cn/cn/lit/an/spraac5g/spraac5g.pdf. [11] 陈钺颖,尹飞飞,范军. CMOS模拟集成电路设计与仿真实例-基于Hspice[M]. 北京:电子工业出版社,2014. Hardware Design and Signal Integrity Similation of 4G Video Transmission Module HUANG Xueda1, FU Shiming2 (1. Chongqing University of Posts and Telecommunications,Chongqing CYIT Communication Technologies Co.,Ltd.,Chongqing 400065,China; 2. College of Mathematics and Information Engineering,Chongqing University of Education,Chongqing 400065,China) A hardware solution of 4G video transmission module based on TMS320DM6467T platform is proposed, which take full advantage of the high-bandwidth of 4G network and can realize video signal transmission fastly. The hardware design is discussed in depth and various functional modules are designed. Importance of Signal Integrity(SI) is introduced, and design scheme of SI is proposed. The simulation analysis of hardware circuit board is made by using HSPICE software and IBIS models. The SI problems, which usually appeared in LPDDR2 interface circuit such as reflection and crosstalk, are resolved effectively, and eye pattern quality is increased. Then the quality of circuit board and speed of signal transmission are fully guaranteed, which is satisfied with requirement of video transmission. 4G; video transmission;LPDDR2; signal integrity 重庆市科委基金项目(cstc2013yykfc4003) TN41 A 10.16280/j.videoe.2015.20.004 黄学达(1978— ),硕士研究生,工程师,主要研究方向为LTE-A终端产品硬件研究。 2015-06-24 【本文献信息】黄学达,付仕明.4G视频传输模块的硬件设计与信号完整性分析[J].电视技术,2015,39(20). 责任编辑:闫雯雯

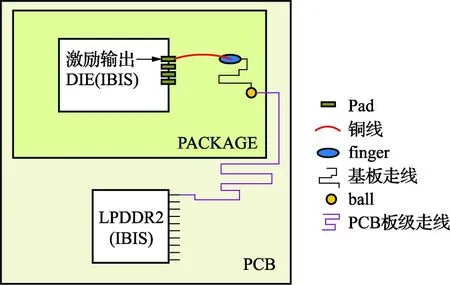

3 4G视频监控模块的LPDDR2 SI仿真分析

4 结论