碳化硅MOSFET桥臂电路串扰抑制方法

钟志远,秦海鸿,袁 源,朱梓悦,谢昊天

(江苏省新能源发电与电能变换重点实验室,南京航空航天大学,江苏南京210016)

碳化硅MOSFET桥臂电路串扰抑制方法

钟志远,秦海鸿,袁 源,朱梓悦,谢昊天

(江苏省新能源发电与电能变换重点实验室,南京航空航天大学,江苏南京210016)

与硅MOSFET相比,碳化硅MOSFET更加有利于满足变换器高效率、高功率密度和高可靠性的发展要求。然而在桥臂电路中,上下管之间的串扰问题严重限制了碳化硅MOSFET性能优势的发挥。本文在分析了串扰问题产生机理的基础上,采用了一种改进的基于PNP三极管的有源密勒箝位方法,对串扰进行了有效抑制,并搭建了双脉冲测试平台进行实验验证。实验结果表明,改进的方法能够获得较好的串扰抑制效果,对碳化硅MOSFET的驱动电路设计具有一定指导意义。

碳化硅;桥臂电路;串扰抑制;有源密勒箝位

1 引言

与传统硅MOSFET相比,碳化硅MOSFET具有击穿电压高、工作频率高和工作温度高等优点。为了满足变换器高效率的发展要求,功率器件的开关速度要尽可能提高,从而减小开关损耗[1-3]。然而在桥臂电路中,要充分发挥碳化硅MOSFET的性能优势,同时保证变换器的可靠性,如何抑制上下管之间的相互干扰(简称为串扰)成为电路设计的关键问题之一[4-6]。

串扰抑制方法可分为无源抑制方法和有源抑制方法[7-10]。无源抑制方法包括在MOSFET栅源极外并电容、增大驱动电阻等,这些方法会增加开关损耗,效果并不理想。文献[7]在MOSFET栅极增加了三极管,发生串扰时将栅极短接到源极,但栅极串扰电压的精确检测比较困难且过快的关断速度会加剧栅极负向串扰电压;文献[10]通过增加辅助开关管,提出了两种有源密勒箝位驱动电路,虽然获得了较好的抑制效果,但是需要增加辅助MOSFET及其驱动电路,大大增加了电路复杂性。

本文首先阐述了串扰问题的产生机理,推导了串扰电压与栅极驱动电阻、漏源极电压变化率等因素之间的数量关系;在此基础上对PNP三极管有源密勒箝位驱动电路进行了改进,弥补了原有方法的不足,在不增加电路复杂性的情况下,有效减小了栅极串扰电压的大小;并以Cree公司的碳化硅MOSFET CMF10120D为例,搭建了双脉冲测试电路,对改进的驱动电路的串扰抑制效果进行了实验验证。

2 SiC MOSFET桥臂电路串扰产生机理

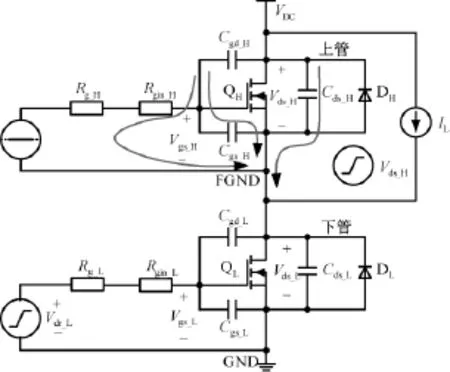

桥臂电路是一种常用的电路结构,含有两个串联的互补导通的开关器件,其主要应用拓扑包括双向DC-DC变换器、半桥变换器和全桥变换器等。桥臂电路中开关管在高速开关动作时,上下管之间的串扰会变得比较严重。当开关管栅极串扰电压超过门极开启电压阈值,就会使处于关断状态的开关管导通,引发桥臂直通问题[10]。此外,当串扰电压超过门极最大电压范围时还会导致器件失效,因此串扰问题严重限制了碳化硅器件性能优势的发挥。图1为下管开通瞬间,上管串扰的产生机制原理图,桥臂电路由上下两个开关管QH、QL及其驱动电路构成,Cgd、Cgs、Cds分别为开关管栅漏极、栅源极和漏源极寄生电容,Rg、Rgin分别为栅极驱动电阻和栅极寄生电阻,VDC为直流母线输入电压。下管开关过程中,上管等效电路如图2所示。

图1 下管开通瞬间的串扰产生机理Fig.1 Schematic of crosstalk in turn-on transient of lower switch

图2 上管串扰电压的等效分析电路图Fig.2 Equivalent circuit for analysis of crosstalk voltage in upper switch

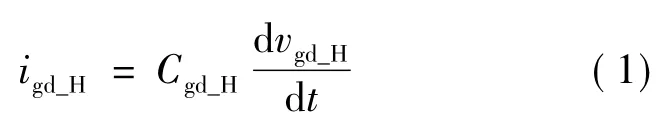

在图1所示的下管开通瞬态过程中,上管漏源极电压开始上升,此电压变化率会在密勒电容Cgd_H上形成密勒电流,方向如图2中箭头所示,密勒电流大小为:

栅极电阻R_H(驱动电阻Rg_H和内部寄生电阻Rgin_H之和)与栅源极寄生电容Cgs组成并联回路,密勒电流对该回路充电,根据基尔霍夫定律可得:

因此开关管栅源极串扰电压大小为:

式中,a为开关管的漏源极电压转换速率dvds_H/dt; Cgd_H、Ciss_H分别为上管的密勒电容和输入电容。

下管开通瞬态过程中,上管串扰电压为正值,如果这个串扰电压的峰值超过了上管的开启电压阈值,上管将会部分导通,上下管之间将流过直通电流,增加两个开关管的开关损耗,严重时会导致器件失效[10]。

在下管关断瞬态过程中,相似地,上管的栅源极会感应出负向串扰电压,这个负的串扰电压不会导致直通问题,但如果它的幅值超过了器件允许的栅极最大负偏压,同样会导致开关管失效。在上管开通和关断瞬态过程中,也会对下管产生相同的串扰问题。

式(3)表明,无论是开通还是关断瞬态,栅源极串扰电压的大小与开关管的漏源极电压变化率dvds/dt成正比,即与开关管的开关速度成正比。此外,串扰电压与时间t成正比,而t的最大取值为开关管漏源极电压变化过程结束时刻,即此时串扰电压达到最大值。在开关过程中,开关管的漏源极电压近似线性变化,dvds/dt近似是恒定值,因而栅源极串扰电压的最大值为:

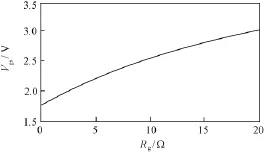

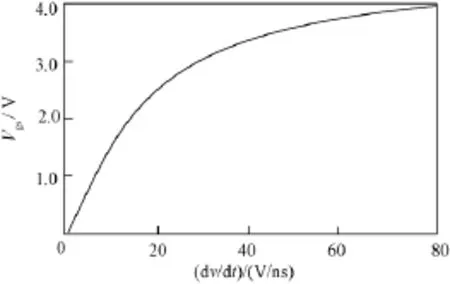

式中,Cgd_H、Ciss_H和VDC通常是由所选器件和工作条件决定,以CMF10120D型号的碳化硅MOSFET为例,其栅极内部寄生电阻、输入电容和密勒电容分别为13.6Ω、928pF和7.45pF,图3、图4分别给出了VDC=600V时不同栅极驱动电阻(漏源极电压变化率取20V/ns)和漏源极电压变化率(栅极驱动电阻取10Ω)与栅源极串扰电压的关系。

图3 串扰电压与栅极驱动电阻关系(VDC=600V,dvds/dt=20V/ns)Fig.3 Relationship between crosstalk voltage and gate drive resistance(VDC=600V,dvds/dt=20V/ns)

从图3、图4中可以看出:

(1)在漏源极电压变化率为20V/ns的情况下,驱动电阻大于9.2Ω时,栅源极串扰电压会超过CMF10120D的开启阈值电压(2.5V),导致桥臂上下管直通问题;

(2)在驱动电阻为10Ω时,漏源极电压变化率大于19V/ns的情况下,栅源极串扰电压同样会超过开启阈值电压,出现直通问题。

图4 串扰电压与电压变化率关系(VDC=600V,Rg=10Ω)Fig.4 Relationship between crosstalk voltage and dv/dt (VDC=600V,Rg=10Ω)

为充分考虑极限情况下栅极串扰电压的影响因素,假设漏源极电压变化率dvds/dt趋近于无穷大,则栅极串扰电压的极限值为:

式(5)表明,CMF10120D在直流母线电压达到331V时,其栅极串扰电压的极限值就会达到开启阈值电压(2.5V),存在上下管直通的危险,因而无法充分发挥碳化硅MOSFET的性能优势。

3 改进的有源密勒箝位串扰抑制方法

传统的有源箝位串扰抑制方法主要是在主开关管栅源极并联PNP三极管或增加辅助MOSFET,将主开关管栅极箝位到地或负压,实现有源密勒箝位。这样虽然可以较好地抑制栅源极正向串扰电压,防止直通问题,但是过快的关断速度会加剧桥臂中另一开关管的负向串扰电压,而碳化硅MOSFET的最大允许负电压较低,CMF10120D的负电压极限值只有-5V,因此传统的串扰抑制方法不适用于碳化硅MOSFET桥臂电路。本文使用了一种改进的有源密勒箝位驱动电路,在主开关管栅源极两端增加了辅助三极管和辅助电容,辅助三极管使用PNP三极管8550,电路图如图5所示,图中只给出了上管的驱动电路,下管驱动电路与上管相似,其工作原理如下:

(1)在上管开通过程中,辅助PNP三极管Qa_H的发射极电压高于基极,使其处于关断状态,辅助电容没有接入电路中,不会影响驱动电路的正常工作,避免了栅源极直接外并电容导致开通损耗增大的问题。

(2)上管关断后,在下管开通瞬间,上管中由于串扰产生的密勒电流流过驱动电阻后,会使辅助PNP三极管Qa_H导通,辅助电容Ca_H接入电路,Ca_H的取值远大于Cgs(通常取Ca_H为Cgs的10倍以上),为密勒电流提供了低阻抗放电回路,有效抑制上管栅源极正向串扰电压。

(3)在下管关断瞬间,主开关管的栅源极电容放电,会在驱动电阻上产生一个左负右正的电压,同样使下管的辅助PNP三极管Qa_L导通,下管的辅助电容Ca_L接入电路,此时能够防止下管的关断速度过快,避免了由于串扰导致的上管栅源极负向串扰电压过大的问题。

图5 改进的有源密勒箝位驱动电路Fig.5 Modified active Miller clamp drive circuit

增加了辅助电容后,通过求解电路微分方程,可得出此时栅极串扰电压Vgs_H的表达式为:

式中,A为辅助电容Ca和输入电容Ciss之和。

图6给出了正向串扰电压与辅助电容容值的关系,栅极正向串扰电压要小于开关管的开启电压阈值(2.5V),为满足正向串扰电压要求,辅助电容应该大于1.3nF,从图6中可看出,辅助电容大于10nF之后,串扰电压幅值基本保持不变,因此辅助电容选择10nF。

4 实验验证

为验证改进的有源密勒箝位驱动电路的串扰抑制效果,搭建了碳化硅MOSFET双脉冲测试电路,其原理图如图7所示。图中,上管QH和下管QL均为CMF10120D型号的碳化硅MOSFET,上管为待测器件,上下管采用相同的栅极驱动电路。实验中仅给下管栅极两个触发信号,而上管的栅极触发信号始终保持低电平,因而上管栅源极两端电压Vgs_H的变化完全是由下管的开关动作引起的串扰。保持功率电路不变,避免因PCB布局的不同而影响测量结果。考虑到实验安全性,实验中设定的输入电压VDC分别取300V、400V和500V,栅极驱动电阻Rg分别取6.8Ω、10Ω和20Ω。

图6 正向串扰电压与辅助电容容值的关系Fig.6 Relationship between positive crosstalk voltage and assisted capacitance

图7 双脉冲测试电路Fig.7 Double pulse test circuit

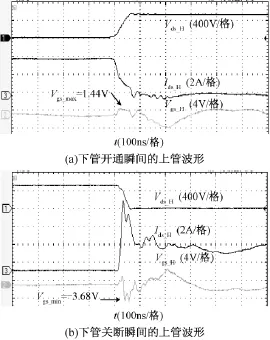

图8给出了输入电压VDC=500V、驱动电阻Rg=6.8Ω时基本驱动电路的串扰测量波形,其中图8 (a)为下管开通瞬间上管的测量结果,图8(b)为下管关断瞬间上管的测量结果。图中 Vgs_H、Vds_H和Ids_H分别为上管的栅源极电压、漏源极电压和漏极电流。从图8(a)和图8(b)中的Vgs_H波形可以看出,此时正向串扰电压和负向串扰电压分别为2V、-4.16V,已接近 CMF10120D的开启电压阈值(2.5V)和栅极负电压极限值(-5V)。

为明确实验测试中栅极串扰电压的变化,图9给出了不同输入电压与不同驱动电阻下串扰电压的测量结果。图中Vgs_H(+)和Vgs_H(-)分别为下管开通瞬间和下管关断瞬间的上管栅极串扰电压幅值。

从图9中可看出输入电压对栅极串扰电压的影响趋势,保持驱动电阻不变,随着输入电压的增大,Vgs_H(+)和 Vgs_H(-)都相应增大。图 9中 Vgs_H(+)和 Vgs_H(-)都与驱动电阻成反比关系,说明增加驱动电阻能够减小串扰电压,但是这种方法会降低碳化硅MOSFET的开关速度,增加开关损耗,因而简单增加驱动电阻并不能较为理想地解决串扰问题,不利于碳化硅MOSFET的高频应用。

图10、图11分别给出了输入电压VDC=500V、驱动电阻Rg=6.8Ω、辅助电容值Ca=10nF时,改进驱动电路的串扰测量波形及串扰电压测量结果。从图11中可以看出,改进的有源密勒箝位驱动电路对串扰电压的抑制效果非常显著,输入电压为500V时,正向串扰电压和负向串扰电压分别为1.44V和-3.68V,分别比基本驱动电路降低了28%和11%,有效降低了上下管直通的风险,同时避免了负向串扰电压过大而使开关管失效的情况。

图8 基本驱动电路的测量波形Fig.8 Measured waveforms of basic drive circuit

图9 基本驱动电路的测量结果Fig.9 Measured results of basic drive circuit

图10 改进驱动电路的测量波形Fig.10 Measured waveforms of modified drive circuit

图11 改进驱动电路的测量结果Fig.11 Measured results of modified drive circuit

5 结论

本文对桥臂电路串扰问题的产生机理进行了分析,对由辅助三极管构成的传统有源箝位驱动电路进行了改进,增加了辅助电容,对串扰电压进行抑制。最终采用碳化硅MOSFET CMF10120D搭建了双脉冲测试电路平台,对改进的串扰抑制方法的实际效果进行验证。实验结果表明,改进的驱动电路有效弥补了原有方法的不足,在有效抑制正向串扰电压的同时,能够防止开关管关断速度过快导致的负向串扰电压超过门极负电压极限而造成器件失效的情况,具有较高工程应用价值。

[1]Biao Zhao,Qiang Song,Wenhua Liu.Experimental comparison of isolated bidirectional DC-DC converters based on all-Si and-SiC power devices for next-generation power conversion application[J].IEEE Transactions on Industrial Electronics,2014,61(3):1389-1393.

[2]孙凯,陆珏晶,吴红飞,等(Sun Kai,Lu Juejing,Wu Hongfei,et al.).碳化硅MOSFET的变温度参数建模(Modeling of SiC MOSFET with temperature dependent parameters)[J].中国电机工程学报 (Proceedings of the CSEE),2013,33(3):37-43.

[3]Kazuto Takao,Hiromichi Ohashi.Accurate power circuit loss estimation method for power converters with Si-IGBT and SiC-diode hybrid pair[J].IEEE Transactions on E-lectron Devices,2012,27(2):1025-1038.

[4]Igor Baraia,Jon Andoni Barrena,Abad Gonzalo,et al.An experimentally verified active gate control method for the series connection of IGBT/diodes[J].IEEE Transactions on Power Electronics,2014,27(2):1025-1038.

[5]Nithiphat Teerakawanich,C Mark Johnson.Design optimization of quasi-active gate control for series-connected power devices[J].IEEE Transactions on Power Electronics,2014,29(6):2705-2714.

[6]Dimosthenis Peftitsis,Roman Baburske,Jacek Rabkowski,et al.Challenges regarding parallel connection of SiC JFETs[J].IEEE Transactions on Power Electronics,2013,28(3):1449-1463.

[7]Zheng Chen,Milisav Danilovic,Dushan Boroyevich,et al.Modularized design consideration of a general-purpose,high-speed phase-leg PEBB based on SiC MOSFETs[A].Proceedings of the 2011-14th European Conference on Power Electronics and Applications(EPE 2011)[C].2011.1-10.

[8]Zheyu Zhang,Fred Wang,Leon M Tolbert,et al.Active gate driver for crosstalk suppression of SiC devices in a phase-leg configuration[J].IEEE Transactions on Power Electronics,2014,29(4):1986-1997.

[9]I Josifovic,J Popovic-Gerber,J A Ferreira.Improving SiC JFET switching behavior under influence of circuit parasitics[J].IEEE Transactions on Power Electronics,2012,27(8):3843-3854.

[10]B Wrzecionko,D Bortis,J Biela,et al.Novel AC-coupled gate driver for ultrafast switching of normally off SiC JFETs[J].IEEE Transactions on Power Electronics,2012,27(7):3452-3463.

(,cont.on p.23)(,cont.from p.12)

Crosstalk suppression method of SiC MOSFET in phase-leg configuration

ZHONG Zhi-yuan,QIN Hai-hong,YUAN Yuan,ZHU Zi-yue,XIE Hao-tian

(Jiangsu Key Laboratory of New Energy Generation and Power Conversion,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China)

Compared with silicon(Si)MOSFET,silicon carbide(SiC)MOSFET is more conducive to meet the requirements of power electronic converters towards high efficiency,high power density and high reliability.However,the crosstalk between the upper and lower switch limits the SiC MOSFET performance in phase-leg configuration.Based on analyses of crosstalk mechanism,this paper uses an improved method of active Miller clamp based on PNP transistor for crosstalk suppression.A double-pulse test prototype is also built to verify the theoretical explanation.As is shown by the experimental results,the improved method achieves good effect in crosstalk suppression and provides guide in design of gate driver for SiC MOSFET in phase-leg configuration circuit.

silicon carbide;phase-leg configuration;crosstalk suppression;active Miller clamp

TN713.4

:A

:1003-3076(2015)05-0008-05

2014-06-30

江苏省新能源发电与电能变换重点实验室开放基金(ZAB11002-14)、中央高校基本科研业务费专项资金和南京航空航天大学研究生创新基地(实验室)开放基金(kfjj20130213)资助项目

钟志远(1990-),男,山东籍,硕士研究生,从事功率变换技术的研究;秦海鸿(1977-),男,江苏籍,副教授,研究方向包括功率变换技术、电机控制。