基于FPGA的高速图像数据存储系统

李超,吕晓龙

哈尔滨工程大学自动化学院,黑龙江哈尔滨 150001

基于FPGA的高速图像数据存储系统

李超,吕晓龙

哈尔滨工程大学自动化学院,黑龙江哈尔滨 150001

为满足高速全景图像的实时无损存储的需求,设计了基于现场可编程门阵列(field-programmable gate array,FP-GA)的SATA阵列和TF卡阵列嵌入式存储系统。用2片FPGA作为控制器,分别负责全景图像的采集处理任务与存储传输任务,设计了8层PCB板级硬件系统并对高速数字信号线进行了细致的阻抗匹配,并设计了支持SD3.0协议的RTL级控制器。实际测试TF卡阵列存储平均速度为227.36 MB/s,峰值速度达293 MB/s,实现了数据的高速存储功能。

全景视觉;现场可编程门阵列;TF阵列;SD3.0;高速存储;阻抗匹配

随着图像传感器制造技术的高速发展,数码相机的分辨率和速度都有大幅提升,因此对图像的处理能力和存储能力都提出了越来越高的要求。与PC系统相比,嵌入式的图像采集、处理和存储系统具有高速的处理和存储数据的能力,实时性强并具有大数据量、小型化的特点。

全景视觉视野范围可以达到180°~360°,广泛应用于监控、视觉导航、太空探测、机器人等领域。由于全景图像数据量大且速度快,很难实现图像采集之后的实时无损存储,本文针对高速全景图像采集系统,构建基于现场可编程门阵列(Field-Pro-grammable Gate Array,FPGA)的专用嵌入式高性能图像实时存储系统,满足数据的高速、大容量、实时性的要求。

西安电子科技大学的NAND Flash存储阵列容量为800 GB,存储速度达到300 MB/s[1]。中科院空间中心以NAND Flash作为存储介质,以四级流水线的方式,最高存储速率达500 Mbit/s,存储容量达128 Gbit,并可以扩展[2]。信亿科技的ANS-9012固态硬盘,采用SDHC卡阵列作为存储介质,平均读取速度为121.4 MB/s。台湾友晶公司的DE4开发平台,以Altera Stratix IV GX系列的FPGA为主控芯片并配有4路SATA硬盘接口。国内自由电子科技代工设计的“高速高清DVR板”采用Xlinx的Virtex5系列的FPGA,设计了2路高速CameraLink接口,支持DDR2缓存和12路SATA硬盘[3]。

这些开发平台覆盖了图像采集、传输和存储功能,但造价非常高昂,适用于通用验证平台,不适合针对性很强的应用。对于高速全景图像而言,采集、处理、存储的数据量大,实现实时无损非易失性存储的难度很大。

1 总体方案设计

在高速系统设计中,一般都遵循面积和速度的平衡互换原则,本文将数据流串并转换,把高速的串行数据流分流为多路并行处理单元进行数据存储。本系统采用2片FPGA分别进行图像的采集处理与存储传输。如图1所示为系统结构图,FPGA1选用EP3C80F780,与4片SSRAM和2路CameraLink接口构成高速图像采集处理子系统;FPGA2选用带有高速串行解串器的EP4CGX110DF31[4-5],设计了4 路SATA接口和8路高速TF卡接口,分别实现硬盘阵列和TF卡阵列,实现图像的存储功能,USB3.0接口与VGA接口分别实现传输与显示功能。

图1 系统结构图

2 板级系统设计

2.1 硬件电路设计

2.1.1 高速接口的布线及阻抗匹配

本文设计了8层PCB板级硬件系统,多层PCB不仅扩大了布线空间,而且合理的分层设计能够提高电源的纯净度和信号的质量,不仅能减少外界环境的干扰,也能减少PCB对外界的电磁辐射[6]。

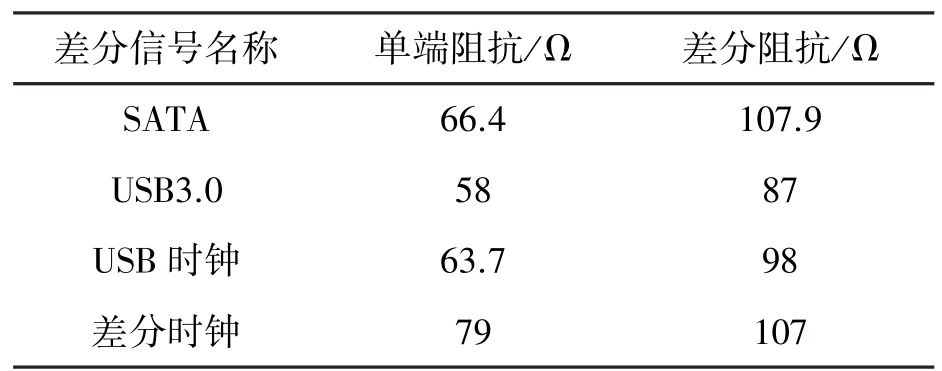

SATA和USB3.0差分信号对与TF卡数据线都是高速数字信号,对阻抗匹配和信号走线都有很高的要求,否则会产生振铃、反射等不良现象。SATA差分信号对必须满足单端阻抗60Ω(±15%),差分阻抗100Ω (±15%)的要求,USB3.0信号线的阻抗要求为单端阻抗60Ω(±15%),差分阻抗90Ω(±15%)。

借助PCB阻抗设计软件Polar SI9000计算信号线的参数,当线宽为5 mil,线间距为7 mil,层高为6 mil,信号线厚度为1.4 mil(1 oz)时,单端阻抗为66.4Ω,差分阻抗为107.9Ω,满足系统要求,其他高速差分信号线的匹配阻抗值如表1所示。

表1 高速差分信号线的匹配阻抗值

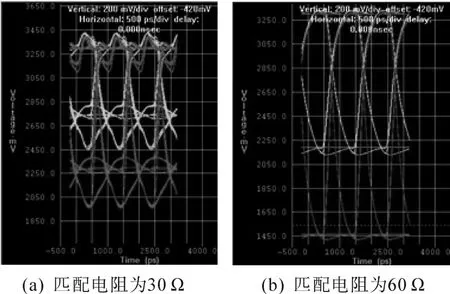

2.1.2 PCB板级硬件电路信号完整性分析

利用HyperLynx软件对关键的高速差分信号与TF卡数据信号线进行板级信号完整性分析,验证布线合理性,及时修改不满足要求的信号线,如图2所示为TF卡数据线在不同匹配电阻时的信号图,图2(a)的匹配电阻为30Ω,信号有较大的超调和抖动,把匹配电阻调为60Ω后,如图2(b)所示,信号质量有了明显提升。如图3所示为存储系统的硬件板级系统。

图2 TF卡数据信号线在不同匹配电阻时的信号

图3 高速图像数据存储装置的硬件板级系统

2.2 SD3.0协议的RTL级设计

支持SD3.0总线协议[7]的TF卡速度等级为UHS-I,最高读写速度达104 MB/s,TF卡有3种工作模式:非激活模式、卡识别模式和数据传输模式。图4为SD控制器的结构,控制器由命令传输模块和数据传输模块构成,命令和数据管理分开控制,便于数据控制和调试。数据模块受命令模块控制,2个模块之间进行通讯协作,数据模块根据命令模块发出的命令进行数据的发送或接收,这样结构紧凑,控制方便,而且可以减少FPGA的资源消耗。

图4 SD控制器结构

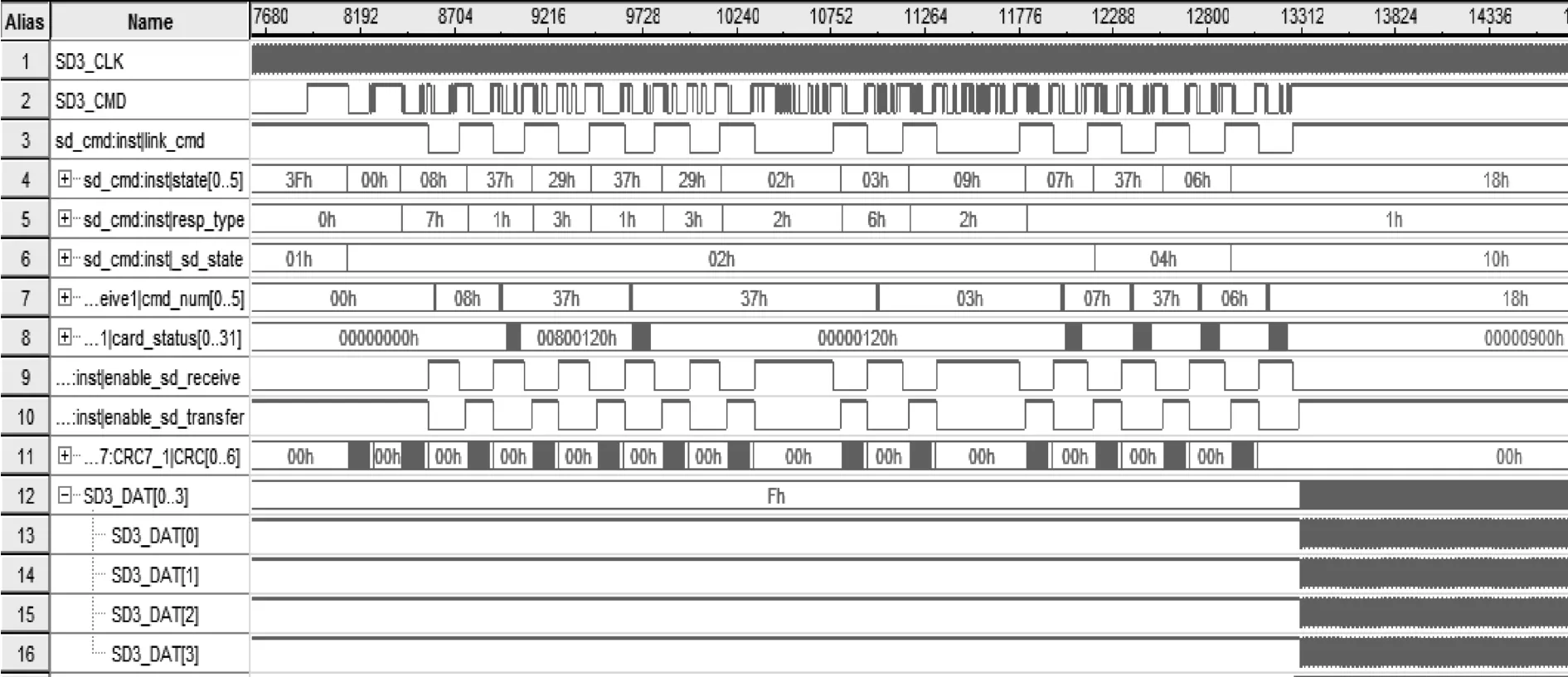

卡识别模式下的工作状态转换为:空闲状态—准备状态—认证状态[8-10]。数据传输模式的工作状态为:就绪状态—传输状态—发送/接收数据状态。卡先进入就绪状态,主机获取CSD寄存器信息后,发送CMD7使要操作的卡进入传输状态,然后主机发送ACMD6设置传输数据线的宽度,主机发送CMD18,从TF卡读数据,发送CMD25,对TF卡写数据。写入数据时,采用多块预擦除和多块读写操作,在多块写操作时,先发送CMD23设定要进行写操作的数据块数,然后发送ACMD23进行多块预擦除,最后发送CMD25进行多数据块写操作。用Verilog HDL语言描述SD主机控制器,并通过有限状态机(FSM)实现状态跳转[11],如图5所示为SD主机的有限状态机。

图5 SD主机的有限状态机

3 系统测试分析

本系统使用SanDisk公司的Extreme Pro移动存储卡进行测试,单卡容量为16 GB,速度等级为UHS-I。采用SignalTap II工具对FPGA信号进行采样分析,图6为采集到的TF卡正确初始化过程。

图6 SignalTap II采集到的TF卡初始化过程

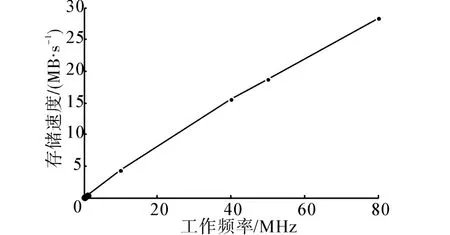

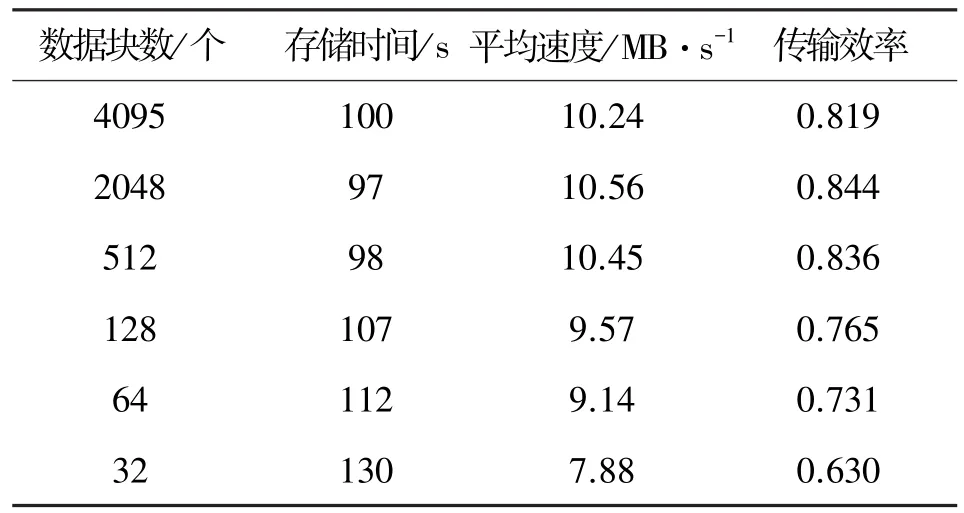

对系统分别进行固定存储时间和固定存储数据量的存储测试。固定存储时间存储,是向TF卡写入120 s时长的数据,每次读写2 048块数据,在不同的工作频率下,测试TF卡的实际存储速度,测量参数如表2所示,存储速度与工作频率之间的关系如图7所示。固定存储数据量存储,是向TF卡写入1 GB的数据,工作频率为25 MHz时,单次写入不同的数据块数,测试TF卡的存储速度,测量参数如表3所示,存储速度与读写块数之间的关系如图8。

表2 固定存储时间存储测试参数(每次读写2 048块数据)

图7 存储速度与工作频率之间的关系

表3 固定存储数据量存储测试参数(工作频率为25 MHz)

图8 存储速度与读写数据块数之间的关系

由实验数据得,每次读写数据块数固定时,随着工作频率增加,实际传输速度逐渐增大,最大平均速度为28.42 MB/s,但传输效率却逐渐降低,最大传输效率为91.43%。工作频率固定时,每次读写数据在512块以上时,传输效率稳定在84%左右,在512块以下时,随着数据块的减少,传输效率逐渐降低。工作频率为80 MHz,单次写入数据块数为2 048时,平均存储速度最大为28.42 MB/s,此时小块数据的周期为1 066,峰值速度为36.64 MB/s,传输效率为91.6%。在实验中,只用8路TF卡阵列的2路接口进行TF卡阵列并行存储的验证。在SD3.0协议中,SDR50、SDR104等高速模式需要1.8 V的信号电压,而此系统只能提供3.3 V的信号电压。在3.3 V的信号电压下,协议中高速模式的最高工作频率为50 MHz,理论最高存储速度为25 MB/s。而本系统的工作时钟最高为80 MHz,超出额定工作频率60%,实际测试本系统的工作时钟最高为80 MHz,单卡平均速度为28.42 MB/s,峰值速度为36.64 MB/s,双TF卡阵列的平均速度为56.84 MB/s,峰值速度为73.28 MB/s。若把8片TF卡全部加入到系统中,则平均速度为227.36 MB/s,峰值速度为293 MB/s,满足高速存储的要求。

4 结论

针对高速全景图像的实时无损存储,本文设计了基于FPGA的SATA阵列和TF卡阵列嵌入式存储系统。通过设计、仿真与实际测试结果表明:

1)此双FPGA系统方案,实现了数据采集处理与存储传输任务的分离,效率更高。

2)设计的8层PCB板级硬件系统,能够满足SATA、USB3.0等高速数字信号的传输要求。

3)设计的RTL级TF卡控制器支持SD3.0协议,在3.3 V信号电压时,单卡存储的平均速度为28.42 MB/s,峰值速度达36.64 MB/s。

4)设计的TF卡阵列,实际测试平均速度为227.36 MB/s,峰值速度为293 MB/s。

本系统实现了嵌入式TF卡阵列的高速图像实时无损存储功能,可广泛应用于全景视觉、机器人视觉导航、监控等领域,具有很好的实际应用价值。

[1]方火能.高速大容量存储阵列控制器的设计与实现[D].西安:西安电子科技大学,2012:41-59.

[2]陈斌,沈卫华.嫦娥二号卫星大容量存储器设计[J].航天器工程,2011(5):99-104.

[3]孙长胜.高速摄影系统中海量数据存储器研究[D].成都:电子科技大学,2011:1-6.

[4]吴继华,蔡海宁.Altera FPGA/CPLD设计:2版[M].北京:人民邮电出版社,2011:46-100.

[5]Altera Corporation.Cyclone IV Device Handbook[EB/OL].[2012-12-01].www.altera.com.cn.

[6]王剑宇,苏颖.高速电路设计实践[M].北京:电子工业出版社,2010:1-280.

[7]SD Group.SD Specifications Part 1 Physical Layer Simpli-fied Specification Version 3.01[S].2010.

[8]李显龙.基于SD总线的FPGA加解密算法实现[D].广州:华南理工大学,2012:6-14.

[9]王清,刘新宁.SD卡硬件启动和数据存储的控制逻辑的设计实现[J].电脑知识与技术,2008(31):990-991.

[10]唐磊,洪传荣.基于FPGA的SD卡控制器设计[J].电声技术,2011(3):29-31.

[11]夏宇闻.Verilog数字系统设计教程:2版[M].北京:北京航空航天大学出版社,2010:20-300.

High-speed image data storage system based on FPGA

LIChao,LYU Xiaolong

College of Automation,Harbin Engineering University,Harbin 150001,China

In order to satisfy the need for the real-time and loss-less storage of a high-speed panoramic image,an embedded image data storage system based on FPGA with SATA array as well as TF card array is designed.The controller consists of two pieces of FPGAs,which and they are in charge of collecting/processing and storing/trans-fermissions of the panoramic image respectively.Further,a hardware system with a PCB board of eight layers is devised,and an impedancematch is performed for the high-speed digital signal lines.Then,an RTL-level control-ler that supportes SD3.0 protocol is projected.Finally,the actual test shows that the average speed of TF cards ar-ray is 227.36 MB/s and the peak speed is up to 293 MB/s,thus a high-speed storage capacity of the data is a-chieved by the developed system.

panoramic vision;field-programmable gate array(FPGA);TF array;SD3.0;high-speed storage;im-pedancematching

TN911

A

1009-671X(2015)02-44-04

10.3969/j.issn.1009-671X.201503016

2015-03-19.

日期:2015-04-08.

国家自然科学基金资助项目(61175089,61203255).

.李超(1991-),男,硕士研究生;

吕晓龙(1977-),男,讲师.

吕晓龙,E-mail:35122911@qq.com.

http://www.cnki.net/kcms/detail/23.1191.U.20150408.1448.001.html