一种LED与PRESENT密码算法重构实现研究

刘波涛,李 浪,2,贺位位,余孝忠,2,杜国权

(1.衡阳师范学院 计算机科学系,湖南 衡阳 421002;2.聚落文化遗产数字化技术与应用湖南省重点实验室,湖南 衡阳 421002)

0 引 言

物联网越来越深入到人们生产生活中,其安全引起了大家高度关注。2007年密码学者提出了适合资源约束的轻量级密码算法PRESENT[1],2011年超轻量级密码算法LED也被提出[2],二个密码算法主要是为资源受限的智能卡加密研发的。如果攻击者知道智能卡加密运算为某一具体密码算法,则容易采取相应攻击手段进行攻击,如果把二种密码算法重构在一起,随机选择某一密码算法进行运算,由于攻击者不知道具体运算的加密算法,则安全性相应提高。重构计算作为一种新兴的计算模式,在许多方面得到了深度应用。重构密码算法是利用可重构计算技术,能够根据需要灵活配置以实现不同的密码算法,从而提高安全性。

重构算法是密码安全的一个重要研究方向,近年来,许多研究机构都致力于密码算法的可重构研究[6-8]。2010年,文献[6]设计了一种 DES、AES和SMS4密码算法的高效可重构,文献[7]给出了一种AES和Camellia算法的可重构硬件实现,两者都未给出可重构算法的具体优化方案。本文实现了一种LED-PRESENT算法重构,研究了优化实现,并对其性能进行了实验验证。

1 LED与PRESENT轻量级密码算法简介

1.1 LED加密算法简介

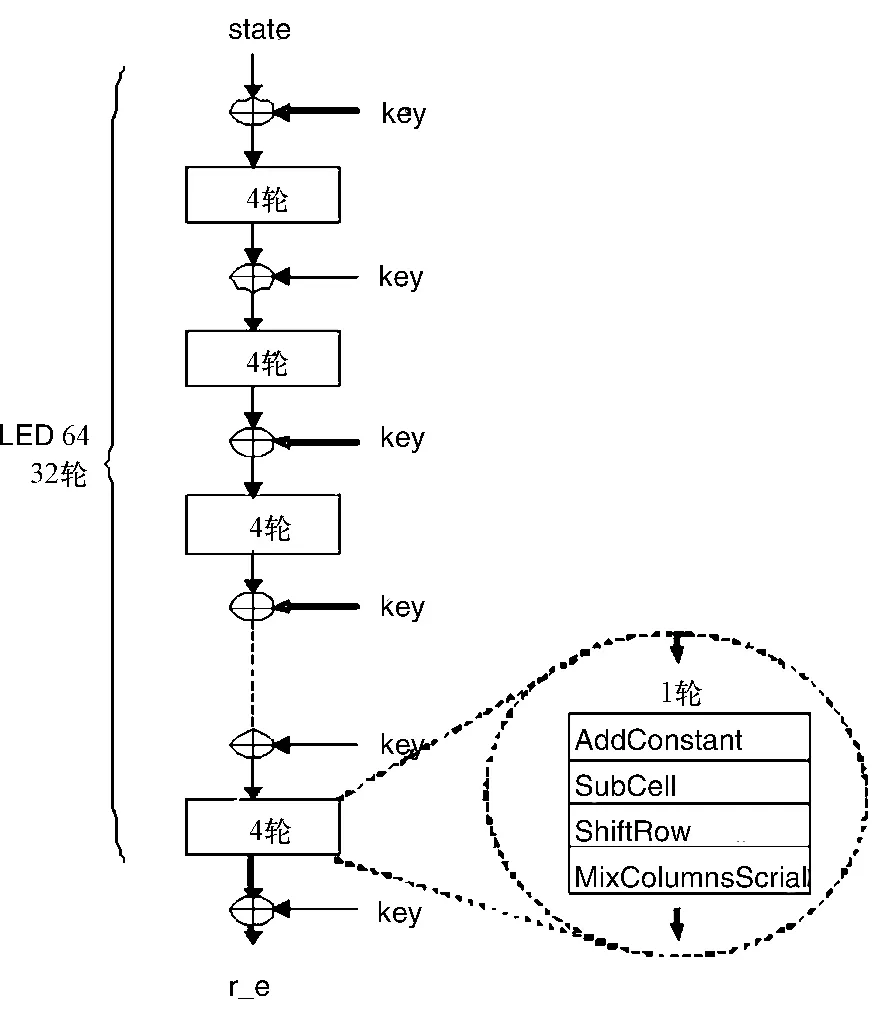

LED密码算法是一种具有SP结构的分组迭代密码算法,其明文长度为64-bit,密钥长度为64-bit或128-bit,对应轮数分别为32轮和48轮,分别用LED-64和LED-128表示。图1为LED-64加密运算过程。

图1 LED-64加密运算结构

LED加密过程:

(1)明文和密钥异或:轮密钥相加(AddRound-Key);(2)进行4轮运算,每个轮包括常数变换(AddConstant)、S 盒 变 换 (SubCell)、行 变 换(ShiftRow)、列混合变换(MixColumnsSerial)4个运算;(3)将中间结果和密钥k异或,转到第(2)步,重复执行8次;(4)输出密文C。

1.2 PRESENT加密算法简介

PRESENT密码算法采用SP结构的轻量级密码算法,其明文长度为64-bit,密钥长度为80-bit或128-bit,记为 PRESENT-80和 PRESENT-128,加密变换需要31轮迭代运算。图2为PRESENT-80加密运算过程。

由图2可知,PRESENT有轮密钥加函数(AddRoundKey)、S盒替换(Sboxlayer)、层置换(pLayer)、密钥扩展(Update)4个模块运算。

图2 PRESENT-80加密运算结构

2 LED-PRESENT重构方法

2.1 重构方案

在两个加密算法中都需要进行S盒变换(Sub-Cell)、密钥加(AddRoundKey)运算,基于此,对LED与PRESENT密码算法S盒变换(SubCell)和密钥加(AddRoundkey)进行重构实现。考虑到所要消耗的面积,还需对LED-PRESENT算法进行FPGA优化实现。

2.2 优化方案

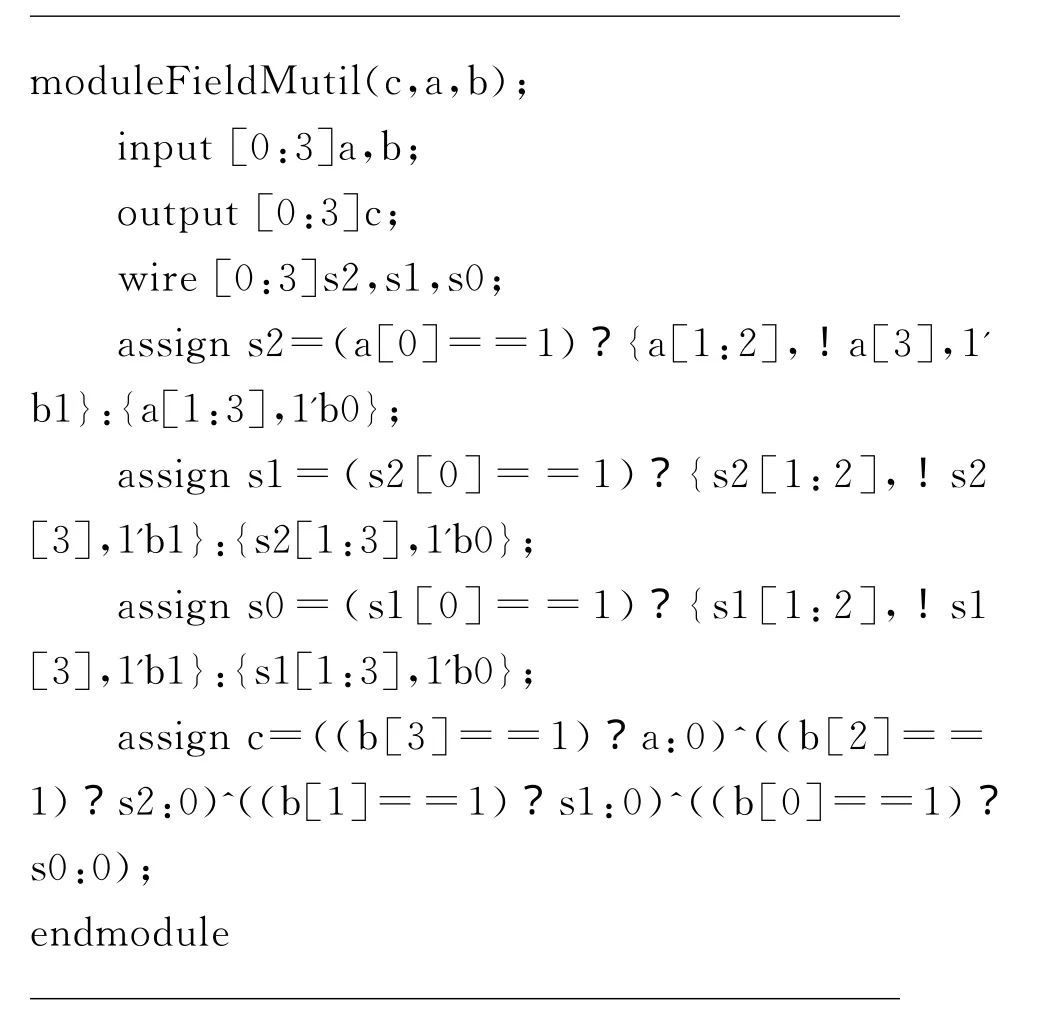

1)在LED有限域部分,用assign连续赋值方式赋值,使得完成一次有限域计算不需要时钟延时,也不需要额外申请寄存器。下面为具体优化实现的VerilogHDL代码:

2)在PRESENT主控制模块中,通过计数器控制重复调用PresentRound模块,可使整个算法实现的面积大为减少。具体VerilogHDL实现代码如下:

2.3 实现步骤

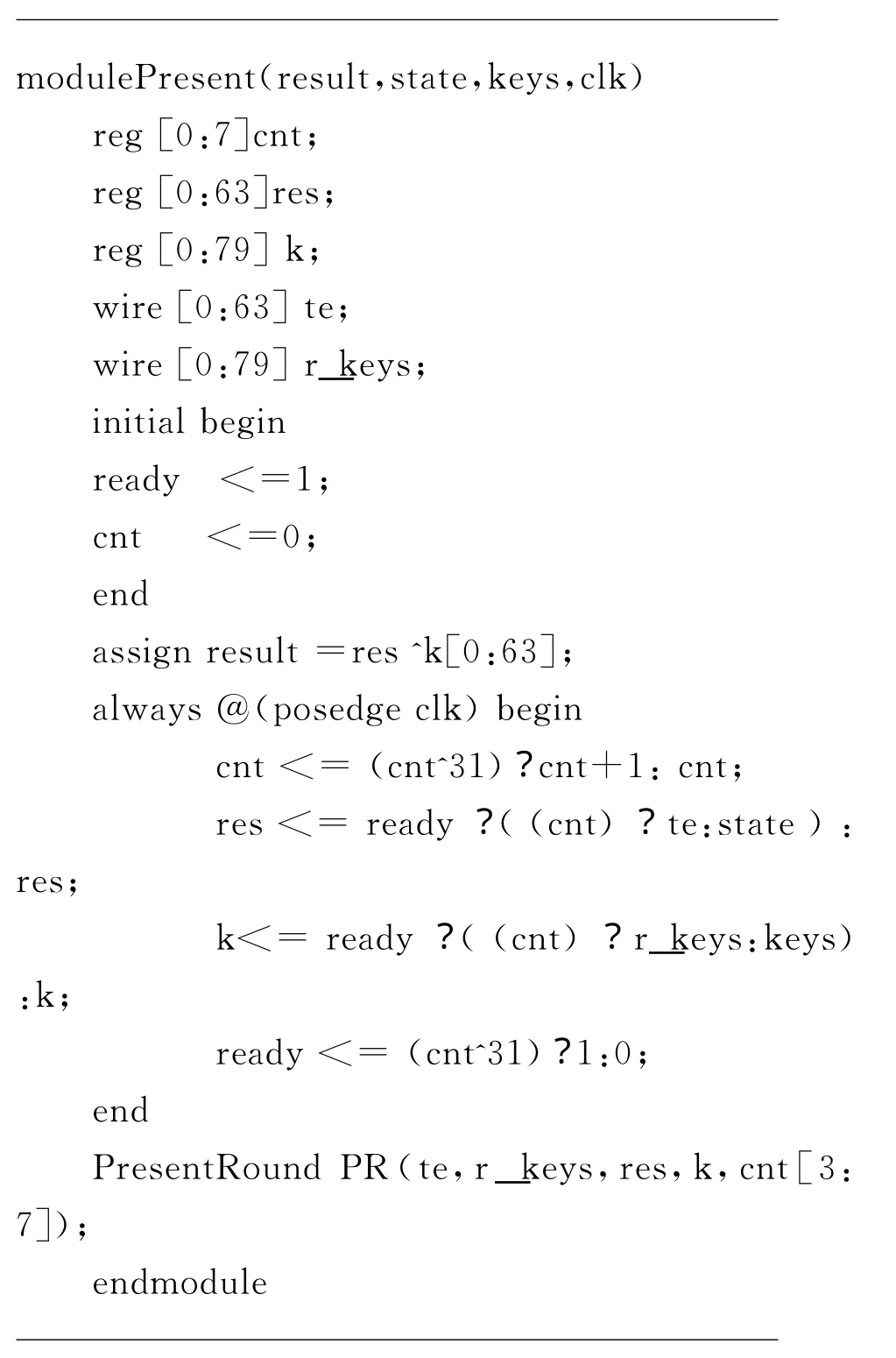

以密钥长为64-bit的LED和80-bit的PRESENT为例,结合流程图给出具体的操作过程。

1)明文加密前由系统随机生成一个1-bit随机数:switch.

2)switch为1时,选择进行 PRESENT-80加密;为0时,选择进行LED-64加密,运算结构如图3。

图3 LED-64与PRESENT-80重构结构流程

明文64-bit,密钥80-bit进行加密的具体参数如下表示,其中state表示明文,key表示密钥。

state=64’h0000_0000_0000_0000;

key=80’h0000_0000_0000_0000_0000;

switch=$random()%2;

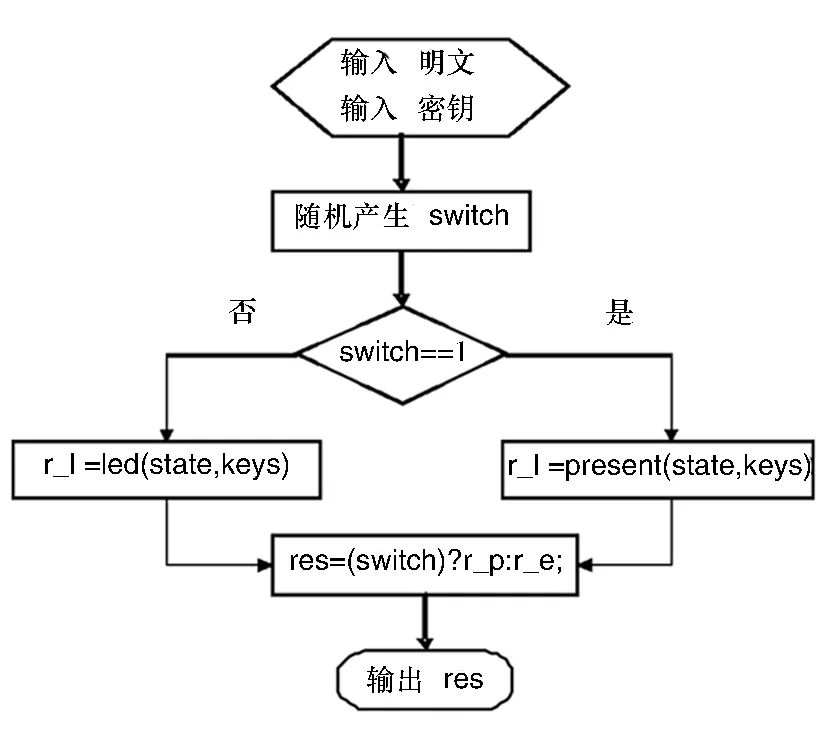

3)整个算法采用Verilog HDL硬件描述语言实现,重构后的算法内部运算流程如图4,具体运算过程如下:

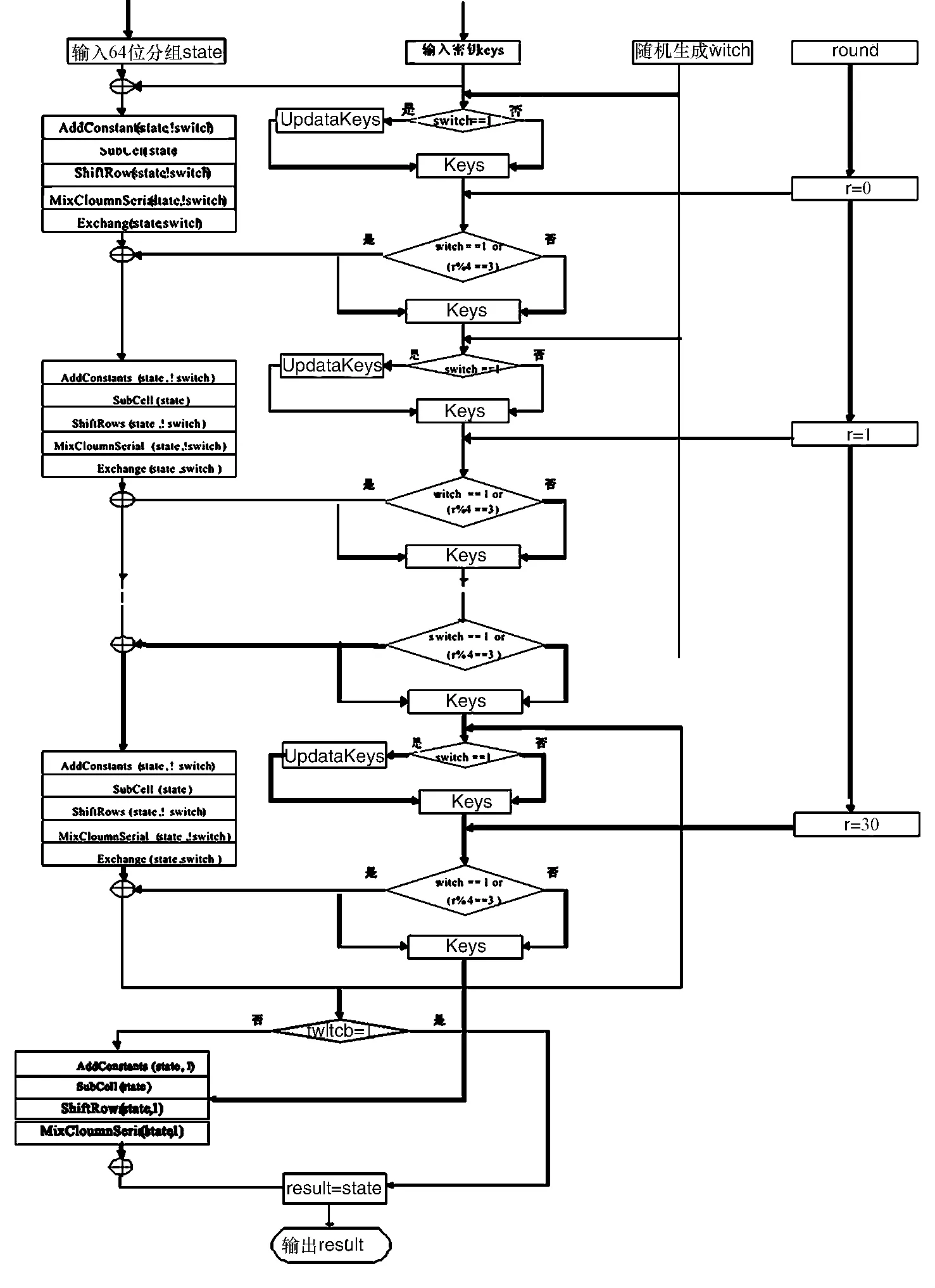

图4 重构算法内部运算流程

(1)初始化明文state、密钥key,系统随机生成switch;

(2)取密钥的前64-bit与明文进行AddRound-Key运算,把运算的轮数r设置为0;

(3)1:如果switch等于1,运算 UpdataKey模块;否则key的值保持不变;

2:state依次完成如下模块运算:(第二个参数相当于使能信号)

2.1AddConstant(state,!switch);

2.2SubCell(state);

2.3ShiftRow(state,!switch);

2.4MixCloumnSerial(state,!switch);

2.5Exchange(state,switch).

3:如果switch等于1或者 (r%4==3),则进行AddRoundKey运算;

4:更新r的值:r=r+1;

(4)跳到(3),重复执行31次;

(5)如果switch等于1,直接输出密文,否则完成LED-64加密算法的最后一轮加密:

AddConstant(state,1);

SubCell(state);

ShiftRow(state,1);

MixCloumnSerial(state,1).

(6)输出密文,运算结束。

由于switch取值为0和1两种,当取值为1时,即选择执行的是PRESENT-80密码算法,由于!switch=0,故3)中的2.1、2.3和2.4是不参与运算的。同理,当switch=0时,执行的是LED-64密码算法,3)中的2.5模块是不参与运算的。

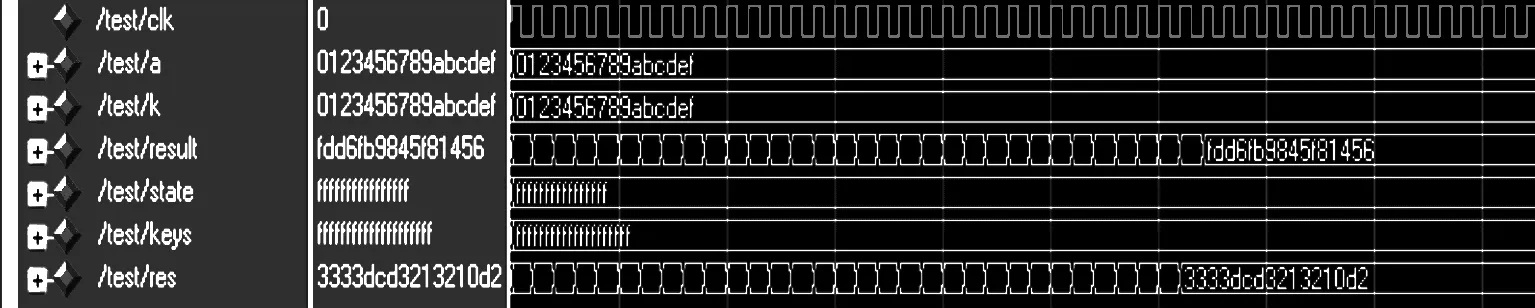

2.4 仿真实验

对Verilog HDL语言实现的LED-PRESENT重构算法进行Modelsim 6.1f仿真,整个算法都是用连续赋值(assign)语句实现,时钟信号控制计算器更新,重构运算分别需要32个时钟周期和31个时钟周期。仿真截图如图5。

图5 重构算法LED-PRESENT仿真截图

从图5的实验结果中可以得到重构算法正确。

3 FPGA硬件实现结果分析

3.1 实验结果

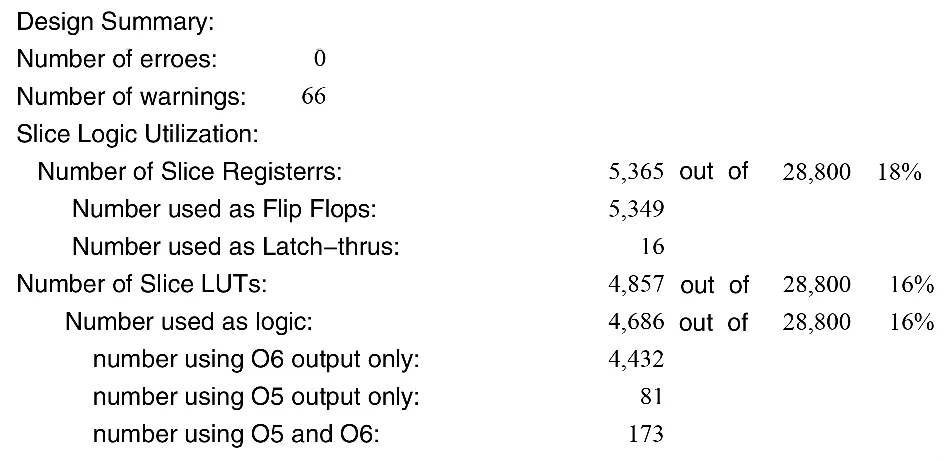

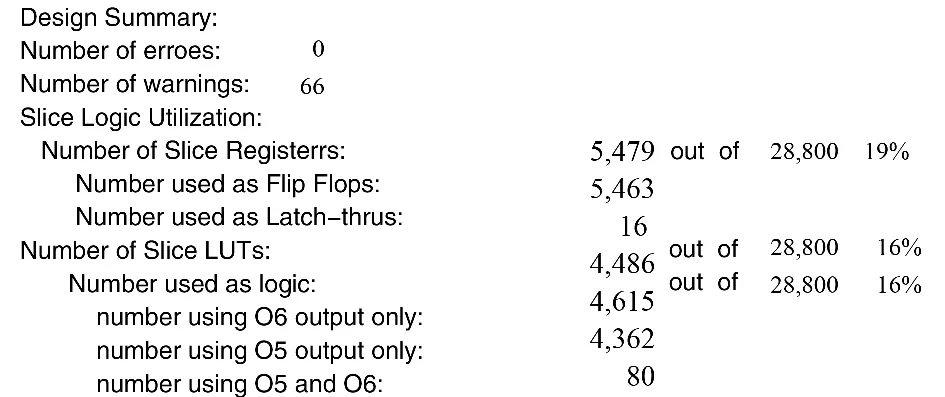

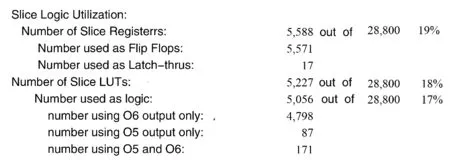

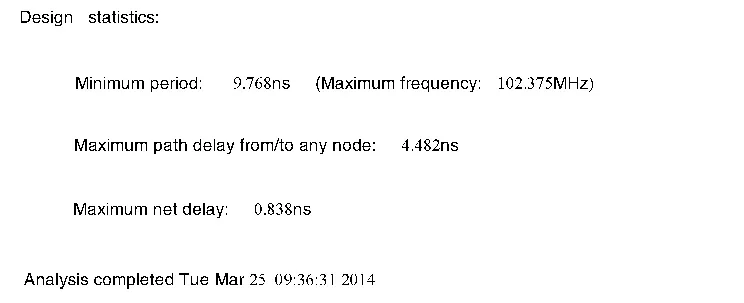

对LED-64和PRESENT-80密码算法,进行了FPGA实现,通过ISE13.2综合下载进行性能分析,FPGA 型号为 Xilinx Virtex-5LX50T。图6是LED-64算法下载到FPGA上的实验数据截图。图7是PRESENT-80算法下载到FPGA上的实验数据截图。图8和图9是LED-PRESENT算法重构后下载到FPGA上的实验数据截图。

图6 LED-64算法面积测试数据

图7 PRESENT-80算法面积测试数据

图8 重构算法LED-PRESENT面积测试数据

图9 LED-PRESENT加密运算频率

3.2 性能分析

根据 实 验 结 果,LED-64、PRESENT-80 以 及LED-PRESENT重构算法的性能对比分析如表1。

表1 性能对比

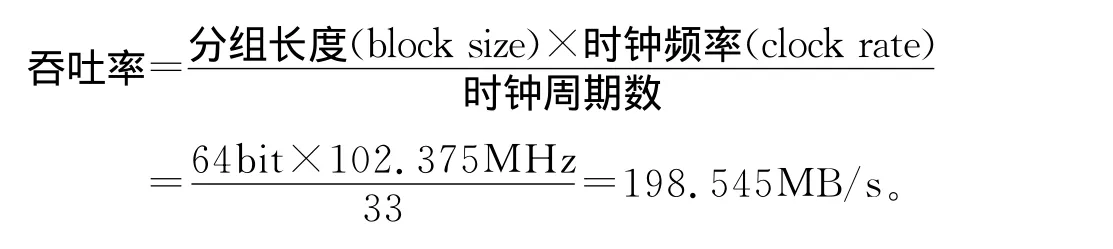

从表1可以得知,LED-64与PRESENT-80算法单独实现面积和为:10222+10265=20487Slices,而重构后LED-PRESENT算法面积为10815Slices,其中Slices是FPGA中面积单元,可以得出重构后的LED-PRESENT比分别实现面积上少了9672个Slices。在加密性能上,分别实现时最高加密速率为198.912Mb/s,而重构密码系统的吞吐率为:

可知,由于使用了优化方法实现,复杂的重构实现并未使系统加密速率降低。

4 结束语

通过对LED与PRESENT密码算法进行重构优化,使得其在单一芯片上资源最优化实现,从而可以适应复杂环境下高安全的加密应用。密码算法重构使得加密运算具有灵活性,从而增强了密码系统的安全。因为密码攻击需要确切知道正在执行的具体密码算法,所以在一定程度上可以抵抗密码攻击。

[1]Bogdanov A,Knudsen L R,Leander G,et al.PRESENT:an ultra-lightweight block cipher//Proceddings of the 2007International Workshop on Cryptographic Hardware and Embedded Systems.Vienna,Austria.2007:450-466.

[2]Guo J,Peyrin T,Poschmann A et al.The LED block cipher//Proceddings of the 2011International Workshop of Cryptographic Hardware and Embedded Systems.Nara,Japan.2011:326-341.

[3]李玮,谷大武,赵辰,等.物联网环境下LED轻量级密码算法的安全性分析[J].计算机学报,2012,35(3):434-445.

[4]吴克辉,赵新杰,王韬,等.PRESENT密码代数故障攻击[J],通信学报,2012,33(8):85-92.

[5]李浪,李仁发,邹祎等.PRESENT密码硬件语言实现及其优化研究[J].小型微型计算机系统,2013,34(10):2272-2275.

[6]李文君.DES、AES和SMS4密码算法的高效可重构实现研究[D].郑州:解放军信息工程大学,2010.

[7]杨宏志,韩文报,李光松.AES和Camellia算法的可重构硬件实现[J].计算机工程,2010,36(10):18-20.

[8]高娜娜,王沁,李占才.一种可重构体系结构用于高速实现DES、3DES和 AES[J].电子学报,2006,34(8):1386-1390.