基于人体域网的FIR数字滤波器的FPGA实现

徐洋,李国权,庞宇,贺焱秋

(重庆邮电大学光电信息感测与信息传输实验室,重庆400065)

人体局域网[1]是一种新的超短距离无线通信网络。它主要是以人体为中心,利用不同功能的传感器节点采集人体生命特征参数,如血氧、血糖浓度、体温和心跳等,再经过信号处理发送到终端。所以数字滤波器的选择对信号的处理尤为重要。常用的数字滤波器有两种:有限脉冲响应滤波器(FIR)和无线脉冲响应滤波器(IIR)。由于IIR滤波器要满足系统函数极点在单位圆内系统才稳定,实现结构必须采用递归型,运算误差大。而FIR滤波器的系统函数极点都在单位圆内,系统有很好的稳定性[2],实现结构采用非递归型,运算误差小,在数字信号处理中被广泛应用。因此,本文采用FIR数字滤波器对物理层数据滤波。而FIR滤波器的实现结构主要有三种类型:直接型、转置型和分布式型。直接型结构主要适用于滤波阶数较低且处理速度要求低的滤波器。转置型结构主要适用于高阶滤波器,但其占用资源较高,处理速度较低。分布式结构主要采用查找表的分割技术可以极大减少滤波器设计规模并提高滤波器的处理速度。

本文从实际应用出发,使用ModelSim仿真工具进行模块设计和功能仿真,选用核心芯片为Altera公司的Cyclone IV系列,型号为DE2-115的FPGA开发板,来进行板上调试,整个过程使用Verilog HDL语言实现。最后与MATLAB理论结果进行对比,验证其可靠性。

1 FIR数字滤波器的实现结构

采用40阶并行分布式FIR滤波器[3],在利用查找表计算时,查找表的ROM将十分巨大,为了减小ROM资源,可以将查找表(LUT)分割成多个小的LTU,而且不会降低运算速度。图1为40阶DA结构FIR滤波器框图。

2 FIR数字滤波器的设计

2.1 FIR数字滤波器的设计流程

该设计流程主要用到MATLAB中的FDATool工具和QuartusII软件的IP核来确定滤波器系数,由ModelSim和QuartusII软件配合开发板来完成系统描述和硬件实现[4],其流程图如图2所示。

图140阶DA结构FIR滤波器框图Fig.140 order DA FIR fi lter block diagram structure

图2FIR数字滤波器流程图Fig.2FIR digital fi lter fl ow chart

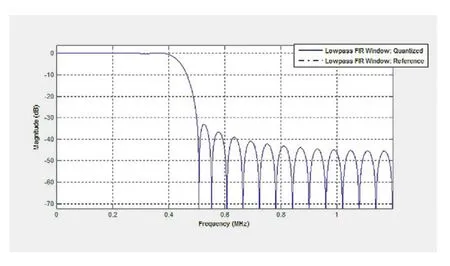

2.2 FIR数字滤波器的系数设计

滤波器阶数与滤波器效果和运算量都有密切关系,滤波器阶数越高,滤波后效果就越明显,但要考虑硬件开销问题。另外,FIR滤波器有两种逼近设计方法即窗口法和频率采样法,由文献[5]可知窗口法更优于频率抽样法。参考IEEE802.15.6协议对物理层的规范,FIR滤波器设计指标如下:

(1)类型:FIR低通

(2)采样频率:Fs=2.4MHz

(3)截止频率:Fc=0.45MHz

(4)窗口类型:Kaiser窗,Beta为2.5

(5)滤波器阶数:40

按照上述指标进行设计,设计后的滤波器幅频响应曲线如图3所示,最后导出浮点型系数。

为了达到对浮点型数据最优量化,本文采用IP核[6]对滤波器系数进行定点化处理。FIR滤波器的系数定点化如图4所示,滤波器定点系数为:

{-17,5,29,20,-24,-49,-11,57,66,-18,-106,-71,83,176,43,-229,-300,100,847,1446,1446,847,100,-300,-229,43,176,83,-71,-106,-18,66,57,-11,-49,-24,20,29,5,-17}。

图3FIR滤波器幅频响应曲线Fig.3FIR amplitude-frequency response curve

3 FIR数字滤波器的FPGA实现

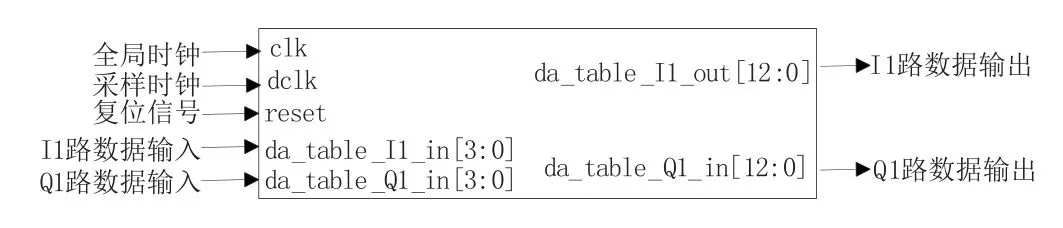

3.1 滤波器的顶层模块实现

输入数据经过π/2-DBPSK调制[7]后为I和Q两路有符号的两位数据,clk为全局时钟,reset为复位信号,高电平有效。由于滤波前要进行四倍上采样处理即两个相邻码元之间进行内插三个“0”,所以需要一个采样时钟dclk,且Tclk=4Tdclk。输出端为I和Q两路有符号的16位数据,顶层模型如图4所示。

图4FIR滤波器顶层模块Fig.4FIR fi lter top module

3.2 滤波器主要模块实现

3.2.1信号发生模块实现

根据信号发生模块的主要功能是为滤波器提供输入数据。该模块输入为随机数,输出为π/2-DBPSK调制后的数据。该模块的输入输出信号如图5所示,FPGA仿真图形如图6所示。

图5信号发生模块Fig.5Signal generation module

图6信号发生模块的FPGA仿真Fig.6FPGA simulation of signal generation module

3.2.2上采样模块实现

上采样模块的主要作用是提高低通重复信号频谱提高时域分辨率和信噪比[8]。上采样的实质是内插,内插的方法有很多种,常用的是相邻码元间内插“0”,由于滤波器设计时上采样系数设为4,即相邻码元间内插三个“0”,这不仅提高信号频率,而且频谱结构不变。该模块的输入输出信号如图7所示,每隔4个dclk时钟采样周期输入信号一次,其余时刻输出为0,图8为FPGA仿真图形。

图7上采样模块Fig.7Up-sample module

图8上采样模块的FPGA仿真Fig.8FPGA simulation of up-sample module

3.2.3查找表模块实现

由于设计的是40阶FIR滤波器,定点化后的40个系数成偶对称,在查找表计算之前先把相同系数对应的数据进行相加处理[9],这样可以看成一个20阶的FIR滤波器,每路信号对应的查找表只需设计5个,大大减小了设计规模。以查找表1为例,查找表1模块的输入输出信号如图9所示,FPGA仿真图形如图10所示。

图9查找表1模块Fig.9Lookup-table1 module

3.2.4循环累加模块实现

从图1可看出输入数据为40个2位并行的数据,经过相同系数对应数据相加处理后变为20个3位并行的数据,此时M等于3,当计数器变到3时即经过三个采样时钟后循环累加模块中“+”变为“-”,因为最高位为符号位。以I路信号的循环累加模块为例,循环累加模块的输入输出信号如图11,FPGA仿真图如12所示, fi r_I_out表示I路循环累加输出值。

图10查找表1模块的FPGA仿真Fig.10FPGA simulation of lookup-table1 module

图11I路循环累加模块Fig.11I road cycle accumulation module

图12I路循环累加模块的FPGA仿真Fig.12FPGA simulation of I road cycle accumulation module

3.3 Signal TapⅡ实时监测

功能仿真完成后,把编写的Verilog代码加载到QuartusII中,配置引脚,完成编译后,通过JTAG模式烧录.sof文件到FPGA开发板中,利用QuartusII软件中的Signal TapII工具对输出信号进行捕获[10],为了观察Q路信号,以Q路为例,Q路输出捕获信号如图13所示,为了防止位溢出,输出高四位设计的都是符号位。

4 仿真验证

将编写的Verilog代码和测试文件导入ModelSim进行功能仿真,FIR滤波器的仿真波形如图14所示。

图13Q路输出捕获信号Fig.13Q road output capture signal

图14FIR滤波器仿真波形Fig.14FIR fi lter simulation waveform

以I路信号为例,取前20个I路输入数据为:

0,0,-1,0,-1,0,-1,0,1,0,-1,0,1,0,1,0,-1,0,-1,0

对应的20个输出数据为:

0,0,17,-5,-12,-25,12,24,-11,-23,15,25,-19,-32,-18,44,79,15,-45,-117

在MATLAB中利用卷积函数conv对20个I路输入数据与40个滤波器系数进行卷积,卷积结果为:

0,0,17,-5,-12,-25,12,24,-11,-23,15,25,-19,-32,-18,44,79,15,-45,-117

由上述数据可以看出滤波器的仿真完全正确。

5 结语

本文针对人体局域网物理层的研究提出一个分布式结构的FIR数字滤波器的解决方案,该方案巧妙地利用查找表将固定系数的乘法运算数转化为查找表操作,极大提高处理速度。但随着对滤波器精度的要求越来越高,滤波器阶数的增加,ROM的数量也会增加,在提高滤波器处理速度的情况下怎么减少ROM数量是当前急需解决的问题。

[1] IEEE standard for local and metropolitan area networks – Part 15.6:Wireless Body Area Networks, IEEE, Feb. 2012.

[2] 金卫, 陈长龄. 基于FPGA的FIR和IIR数字滤波器的设计[J]. 四川大学学报:自然科学版, 2004, 41:376-379

[3] Wang Sen, Tang Bin, Zhu Jun. Distributed Arithmetic for FIR Filter DesignonFPGA [J].Communications, Circuits and Systems, 2007,13(11): 620-623.

[4] 单文军, 周雪纯, 李文华. 基于FPGA的FIR数字滤波器设计与实现[J]. 现代电子技术, 2013,(14):123-126.

[5] 姚海燕. FIR数字滤波器设计窗函数法与频率抽样法比较[J]. 安阳工学院学报, 2007, (6):51-53.

[6] 吴超. FIR数字滤波器软IP的设计与实现[J]. 电脑知识与技术,2014, (20):4732-4734.

[7] Niemela V, Hamalainen M, Iinatti J. On IEEE 802.15.6 IRUWB receivers - simulations for DBPSK modulation [J]. IEEE engineering in Medicine and Biology Society. 2013:1676-1679.

[8] Siddiqi M A, Samad N, Masud S,et al.FPGA-based Implementation of Efficient Sample Rate Conversion for Software Defined Radios[C]. Computer and Information Technology, International Conference onIEEE, 2010:2387-2390.

[9] 张惠国, 唐玉兰, 于宗光,等. FPGA高性能查找表的设计与实现[J]. 固体电子学研究与进展, 2009, 29:584-588.

[10] 叶小敏. Signal Tap II高级功能在FPGA调试中的应用[C]. IT时代周刊论文专版, 2014:296.