一种用于高速数据流的并行数字下变频方法

史秀花, 刘 凯, 王志诚

(上海无线电设备研究所,上海200090)

0 引言

在软件无线电的数字信号处理过程中,数字下变频将数字中频信号下变频为低中频或基带信号,降低后续信号处理的数据率和处理量。随着ADC采样率和采样精度的提高,接收机模拟数字转换速率由兆赫兹向吉赫兹方向发展。吉赫兹采样后的数据流对信号处理平台的运算速度和资源消耗提出了较高要求。

数字下变频有三种实现途径:专用数字下变频芯片,DSP芯片编程和FPGA 编程实现[1]。由于FPGA具有软硬件信号处理、硬件可重构、配置灵活、I/O速度快和便于实现并行处理等优势,已成为数字下变频的常用方法。当前FPGA 器件对吉赫兹采样后的信号直接进行数字下变频时存在四个问题:一是无法用普通的I/O 引脚接收高速信号;二是采用查表法无法实现高速NCO;三是用作混频器的高速乘法器无法实现;四是抽取滤波器中的高速乘法器和加法器无法实现[2]。

本文以降低信号速率为途径对并行数字下变频技术进行研究,将其应用于吉赫兹采样下的数字下变频。并行数字下变频技术以多相滤波为基础,将单路高速数据流经串并转换后分为多路低速数据流信号,然后同时对每路低速信号进行数字下变频。

1 数字下变频的概念

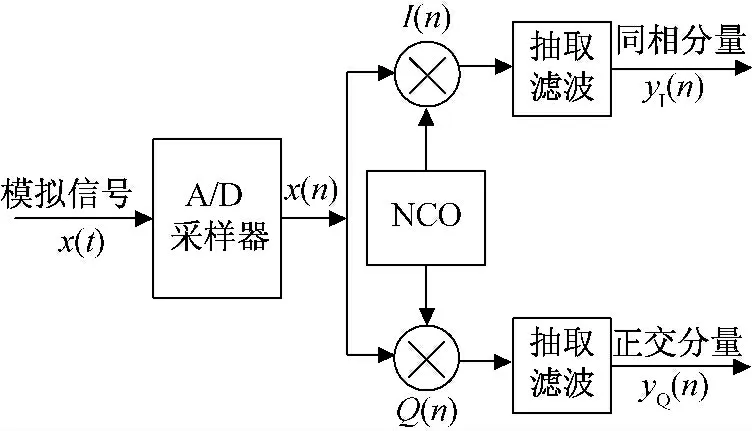

数字下变频的主要功能是将数字中频信号下变频至基带,提供适合后续数字信号处理的信号,基本模型如图1所示。数字下变频可分为混频部分和抽取滤波部分。

图1 数字下变频基本模型

(1)混频

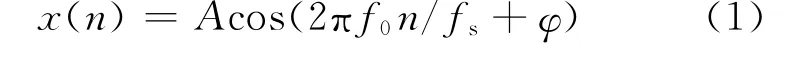

设A/D 采样后的信号为

式中:A 为信号的幅度;f0为信号的中心频率;n为信号的采样序号;fs为A/D 转换器的采样频率;φ 为信号的初相。

NCO 产生的两路正交本振信号分别为

式中:fL0为NCO 的本振频率。

混频后信号的同相分量和正交分量分别为

从式(3)可以看出,混频后的信号中不仅包括期望的基带信号,还包括高频分量,将混频后的信号经过低通滤波可得到基带信号。另外,为了降低数字信号处理的数据率和处理量,需对信号进行抽取处理。

(2)抽取滤波

抽取滤波的作用是降低信号的数据流速率、降低运算量和滤除信号中的高频分量。

在对混频后信号抽取滤波的过程中,由于信号中含有高频分量,采用先抽取后滤波的结构会引起信号频谱混叠,所以抽取滤波应该采取先滤波后抽取的结构。另外,为了保证信号的完整性,抽取后信号的无模糊带宽应该大于信号等效带宽的二分之一。

2 高速数据流的数字下变频

从图1可以看出,混频器、低通滤波的速率和A/D 采样器的输出速率应该保持一致。数字下变频一般在FPGA 中实现,对于吉赫兹的采样数据,目前FPGA 器件中的乘法器速度无法与吉赫兹数据相匹配。因此,需要对A/D 采样信号、本振信号和低通滤波器进行多相划分[3]。

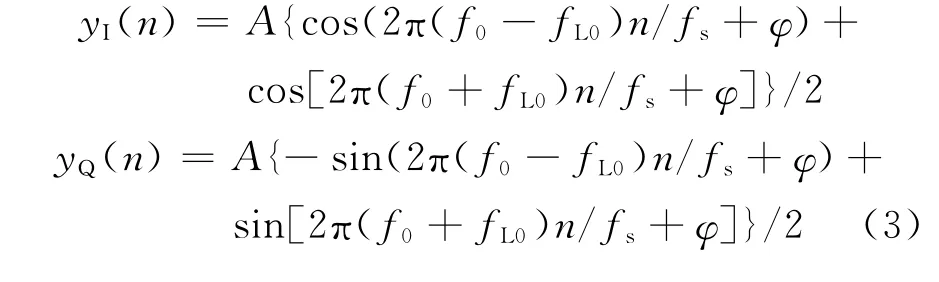

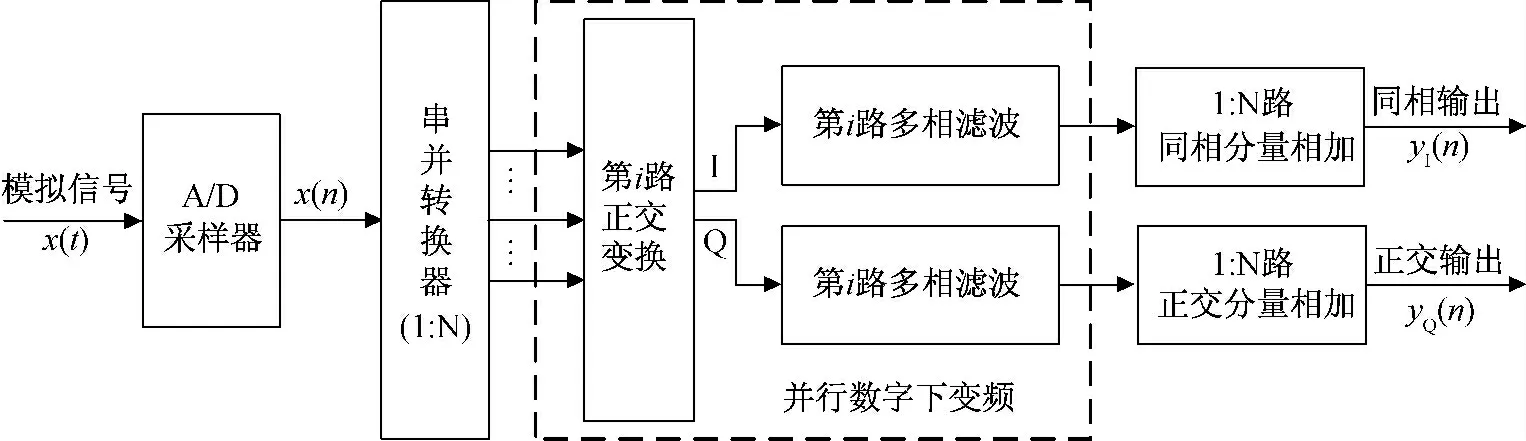

2.1 并行数字下变频

对于吉赫兹的采样信号可以采用并行数字下变频来实现频谱搬移和数据流降速处理,并行数字下变频的模型如图2所示。

从图2可以看出,并行数字下变频首先将A/D 采样数据进行串并转换,即将一路数据率为fs的信号转换为N 路数据率为fs/N 的信号。经过串并转换已经将信号的采样率降低,降低了后续处理对硬件处理速度的要求。串并转换后的每一路低速信号分别与并行NCO 进行混频,再将混频后的每一路信号送入多相滤波器滤除其中的镜频分量。多相滤波器输出的同相分量和正交分量进行相加,可得到最终基带信号的同相分量和正交分量。

2.2 并行NCO

同相分量的本振信号可写为

图2 并行数字下变频的模型

为了保证分相后多路下变频的正确性[4],NCO 分相后的各路信号应该具有相同的采样率和中心频率,但是各路信号之间应该具有一定的相位差。因此,分相后第i路本振信号与分相前的本振信号的关系为

式中:D 为总的分相路数。

从式(5)可以看出,分相后的每路本振信号具有相同的中心频率和采样率,分别为fL0和fs,而且相邻分量之间具有相同的相位差,为

正交分量本振信号分析方法与同相分量相同,这里不再重复。

2.3 滤波器的多相结构

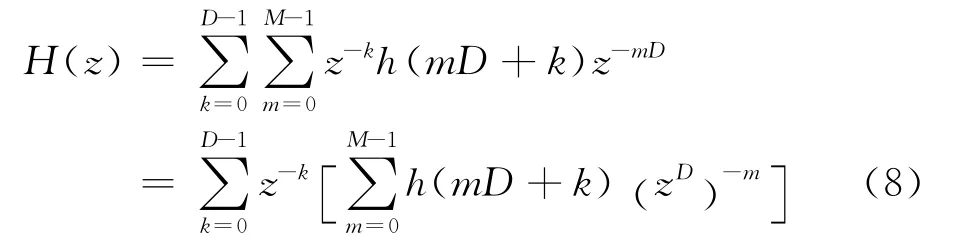

设FIR 数字滤波器的冲击响应为h(n),则其Z变换为

对上式进行重新组织并令n=mD+k(m=0,1,… ,M-1,k=0,1,… ,D-1,N=MD)后为[5]

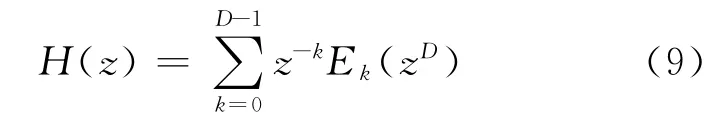

式(9)即为FIR 数字滤波器的多相结构,其网络结构图如图3所示。

图3 滤波器的多相结构

根据抽取器的对等关系[6],将抽取环节(D 倍抽取)引入到多相滤波结构当中,可以得到基于多相分解的低通滤波器高效实现结构[7],如图4所示。

图4 多相滤波的高效实现结构

对比图3和图4,可以看出:多相滤波的高效实现结构中滤波器均位于抽取器后,即滤波是在降速后进行的,可以大大降低滤波器中乘法器和加法器的处理速度。通过合理选择抽取因子D,可以实现吉赫兹采样信号的抽取滤波处理。

蒋介石对于军权的崇尚,造成其对于党的建设、对党义的研究和宣传相对较为漠视,使国民党的意识形态宣导日趋贫乏无力。国民党在三民主义意识形态的理论建构方面,基本上毫无建树。王子壮在日记里曾谈及:“自北伐迄今已达十余载,而党义著作之贫乏,不特未能表现于社会科学各方面,甚且解释主义之著作亦寥寥可数。”㉗

3 仿真验证

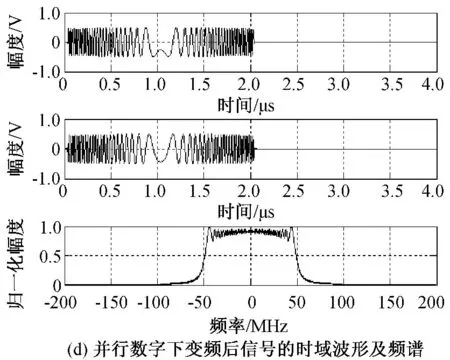

本文中仿真参数设置为:信号形式为线性调频信号;信号中心频率为2.5GHz;采样频率为2GHz;信号带宽为100 MHz;信号时宽为2μs;串并转换后的信号路数为5。使用Matlab软件对该信号进行并行数字下变频仿真,仿真结果如图5所示。

图5(a)是A/D 采样后信号的时域波形及频谱,图5(b)是并行数字下变频后第1路信号的时域波形及频谱,图5(c)是并行数字下变频后第5路信号的时域波形及频谱,图5(d)是经过并行数字下变频后信号的时域波形及频谱。从仿真结果可以看出,使用并行数字下变频技术可以完成吉赫兹采样信号的下变频和降速处理。

图5 并行数字下变频仿真结果

4 FPGA 硬件实现

根据仿真参数可知,由于A/D 采样率为2 GHz,进入FPGA 的数据率为2GHz,因此选择的FPGA 芯片应该具有快速的I/O 口。另外,选择的A/D 采样率为2GHz,串并转换路数为5,串并转换后信号的数据率为400 MHz,即FPGA需处理的数据率为400 MHz,因此应选择支持较高速度乘法器的FPGA 芯片。

选 择 Xilinx 公 司 Virtex-6 系 列 的XC6VSX315T 芯片来实现2GHz采样信号的并行数字下变频进行实物验证,该芯片支持的最大乘法器速度为600 MHz,满足2GHz采样信号5路串并转换后400 MHz数据率对乘法器速度的要求。另外,选择的采样精度为12bit,该芯片有24对GTX 高速I/O 口,传输速率高达11Gbit/s,也满足2 GHz数据率对I/O 口传输速率的要求。

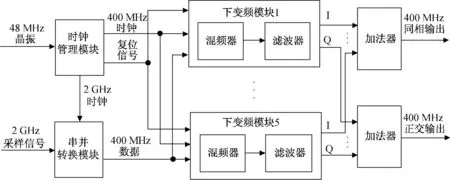

图6给出了FPGA 实现2GHz采样信号并行数字下变频的原理框图,图中包括一个时钟管理模块、一个串并转换模块、五个下变频模块和八个加法器模块。时钟管理模块用于产生400 MHz的时钟和复位信号;串并转换模块用于将1 路2GHz数据率的信号转换为5路数据率为400MHz的信号;下变频模块用于完成5路信号的正交变换和滤波将信号下变频至基带;加法器模块用于实现五路数字下变频模块产生同相分量和正交分量的综合。

图6 并行数字下变频程序的原理框图

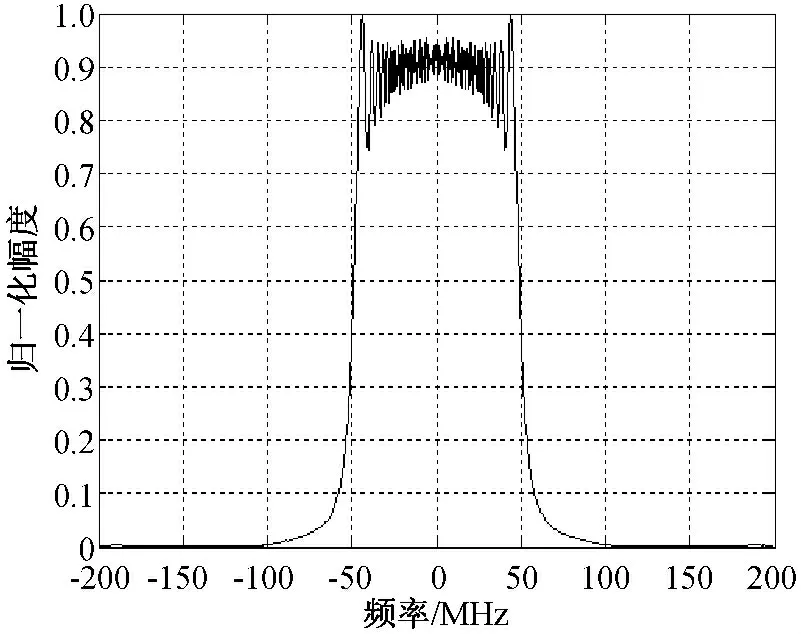

图8给出了2GHz采样信号并行数字下变频的FPGA 实现结果的频谱。可以看出,FPGA可以完成2GHz采样信号的并行数字下变频。

图8 并行数字下变频FPGA 实现结果的频谱

5 结束语

本文通过对并行数字下变频技术研究,将其应用于吉赫兹采样信号的数字下变频中,并对并行数字下变频进行MATLAB 仿真和FPGA 实现,仿真和实验结果表明并行数字下变频可用于吉赫兹采样信号中,支撑吉赫兹采样技术的工程实现。

[1] 郭连平,田书林,王志刚,等.并行数字下变频中的NCO 实现研究[J].仪器仪表学报,2012,33(5):999-1004.

[2] 陈大海,王洪,吕幼新.宽带数字下变频器的高效实现结构[J].电子测量与仪器学报,2008,22(5):43-47.

[3] 常虹,赵国庆,牛新亮.高效的宽带数字信号化接收机设计[J].西安电子科技大学学报(自然科学版),2010,37(3):464-468.

[4] 付永庆,李裕.基于多相滤波器的信道化接收机及其应用研究[J].信号处理,2004,20(5):517-520.

[5] 廉昕,姜坤,王元钦,等.基于并行NCO 的宽带数字下变频器[J].电子测量技术,2012,35(7):73-77.

[6] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2006.

[7] 王亚军,李明.基于多相滤波的数字中频正交相干检波系统[J].制导与引信,2009,30(3):56-60.