一种集成于I/O的段码式LCD驱动IP核设计

陈 洁,陈 岚

中国科学院 微电子研究所,北京 100029

段码式液晶显示器LCD(Liquid Crystal Display)以其驱动电流小,配置灵活,功耗低,寿命长及成本低廉等优势被广泛应用于仪器仪表中。段码式LCD的驱动较为复杂,为了延长LCD的使用寿命,段码式LCD需要由至少3个电平构成的方波序列来驱动[1]。一般情况下,0.18 μm工艺中的数字集成电路的电源电压通常为1.8 V,而驱动LCD的最高电平需要高于3 V,因此数字电路无法简单地直接输出预期的方波序列。为了实现段码式LCD的驱动,通常需要采用另外的驱动芯片或者设计复杂的模拟电路[2-3],这无疑增加了集成电路后端设计流程的复杂度和段码式LCD应用的开发成本。

为此本文设计了一种集成于I/O单元的通用的段码式LCD驱动IP核(Intellectual Property core),使得I/O单元在保留原有功能的同时又具有驱动段码式LCD的能力。本IP核虽为模拟电路结构,但在应用时完全兼容数字后端设计流程,同时本IP核的应用提高了芯片集成度,缩短了段码式LCD应用的开发周期,降低了应用的开发成本。

1 系统设计

1.1 原理简介

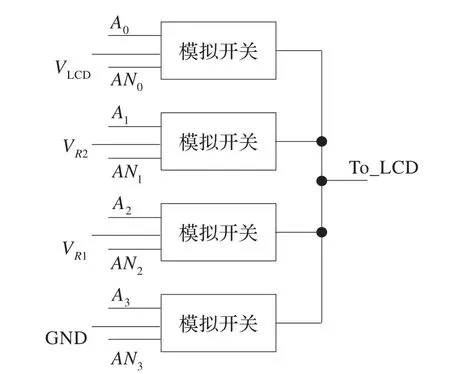

段码式LCD的驱动电路结构如图1所示,为了实现方波输出,需要给驱动电路提供0、Δu、2Δu和3Δu等直流电平输入,并通过模拟开关电路分时导通[4]。直流电平可由片外电阻分压产生,开关电路的控制信号由前级数字模块产生。图1中的A0~A3、AN0~AN3为控制信号的输入端口,VLCD、VR2、VR1和GND分别为 3Δu、2Δu、Δu和0等直流电平的输入端,To_LCD为驱动电路的方波输出端。在本设计中,控制信号An和ANn为互补数字信号,Δu=1.1 V 。

集成电路中的开关电路通常采用传统的CMOS传输门[5-8],图1中的模拟开关模块的开关功能主要就是由传输门实现的。一般情况下,0.18 μm工艺的芯片内标准晶体管供电电压为1.8 V,因此,芯片内部数字电路的信号电压最大为1.8 V。而1.8 V的控制信号无法正常控制输入电压为2.2 V和3.3 V的传输门,为了提高控制信号的电压,首先需要设计电压转换电路对模拟开关电路的控制输入信号进行电压转换,将0 V和1.8 V的控制信号转换为0 V和3.3 V。电压转换电路的输出信号经缓冲电路消除噪声抖动后输入到传输门的控制端。

图1 段码式LCD的驱动电路结构图

1.2 电压转换电路

在电压转换电路中使用了锁存电路,锁存电路以其简单实用的特性被广泛应用于集成电路中,以实现低电压对高电压的转换[9-11]。图2所示的锁存电路为双稳态电路,当输入不相等时,电路在正反馈的作用下会使输出最终稳定在VLCD或GND。在本设计中,VLCD为3.3 V,An和ANn为互补数字信号。如An为逻辑‘1’,则A_trans端输出3.3 V,反之输出为0,从而完成1.8 V的控制信号到3.3 V的控制信号的转换。

图2 控制电压的转换电路结构图

1.3 缓冲电路与传输门

图3为缓冲电路和传输门的结构,其中前两级反相器为电压转换电路的输出缓冲级,缓冲电路可以提高驱动电路的抗干扰能力,消除可能发生的信号抖动(噪声)。

图3 控制电压的缓冲电路与传输门

电压转换电路输出的A_trans信号通过两个3.3 V供电的反相器,形成稳定的控制信号A_f,A_f再通过一个反相器产生AN_f,AN_f与A_f一起控制传输门是否导通。IN为3Δu、2Δu、Δu或0 V等直流电平的输入端口,To_LCD为驱动电路的输出端口。

1.4 晶体管尺寸的确定

输出方波的跳变频率和负载对传输门的驱动能力提出了要求。本设计需要考虑的负载有:片外LCD屏幕的电容、I/O中大面积金属线的电容以及封装带来的电容等。

取跳变时间t为时钟周期T的20%,取传输门输出的跳变时间为输出电压的10%到90%的区间,则可得传输延时公式:

其中r为传输门的等效电阻,c为传输门负载总电容,U为LCD的最大跳变电压。由式(1)可以得到r的最大值rmax。参考芯片制造厂的数据文档后,可由此rmax确定传输门中 MOS管的尺寸,NMOS:W/L=1.1 μm/0.35 μm ,PMOS:W/L=1.4 μm/0.3 μm 。

2 驱动电路与I/O的结合

本设计的最独特之处在于将此IP核合并到I/O中,使得数字芯片可以在不添加额外管脚的情况下也能具有段码式LCD的驱动能力。由于本IP核与芯片内部的接口均为数字接口,所以能完全兼容数字后端设计流程,而不需要手动布线。

图4 驱动电路与IO的结合

如图4所示,将此IP核的输出端直接拼接于模拟I/O的输入端,便可以将结合了模拟I/O的驱动电路合并到任意带三态功能的数字管脚上,使此管脚能为段码式LCD驱动端口和原数字端口所复用。当此管脚上的LCD驱动单元的模拟开关全部处于关断状态时,此管脚可用于原有的数字功能。若要使用LCD驱动功能,则需要控制此管脚上的数字I/O单元保持为高阻态,管脚可以输出预期的方波序列,实现LCD驱动的功能。

需要注意的是,数字I/O口要具有三态功能才能实现复用。若应用中的数字I/O口原本没有三态功能,则可将原数字I/O口替换为增加了三态功能的数字I/O口再与模拟I/O合并。在本设计中,此IP核的3Δu、2Δu、Δu和0 V的直流输入都来自电源环,以简化布线的复杂度。

3 版图实现与测试

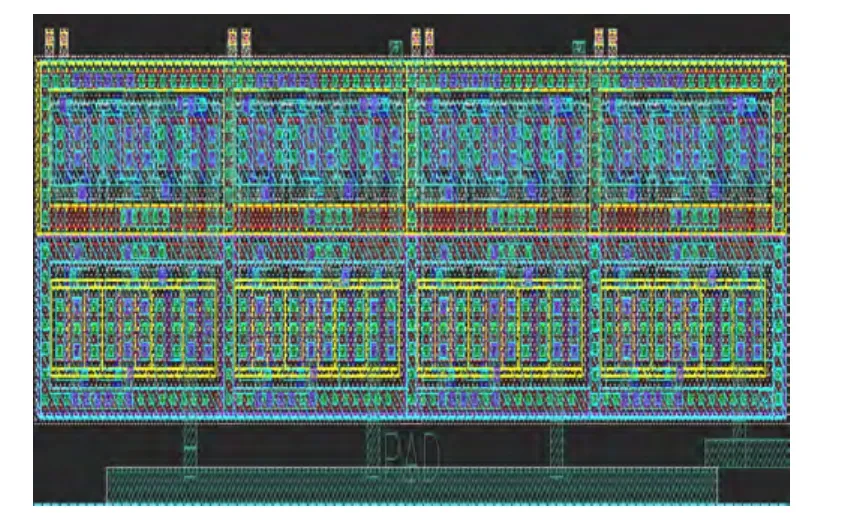

一般情况下,0.18 μm工艺中的标准晶体管栅极最多只能承受3 V的电压,而在本设计中,栅极需要承受3.3 V的电压,因此,为了正常应用于3.3 V的电压环境,本设计中的每一个晶体管都需要使用厚栅,以保证栅极能承受高于3.3 V的电压。此外,为了减少噪声的干扰,本IP核在电路周围添加了保护环。

最终版图如图5所示,面积为 36.22 μm ×7.33 μm=265.5 μm2。

图5 IP核最终版图显示

图6为流片后的测试结果在示波器中的显示。复用管脚在LCD驱动模式下能正常输出预期的方波序列,能正常驱动段码式LCD。

图6 流片后的测试结果

4 结论

本文实现了段码式LCD驱动IP核与数字/模拟I/O的高效集成,使得数字芯片管脚具有了直接驱动段码式LCD的能力;实现了一个兼容数字电路后端设计流程的模拟结构IP核,使得复杂的LCD驱动电路能通过纯数字后端设计流程完成。本文IP核的应用提高了芯片集成度,缩短了段码式LCD应用的设计周期,降低了应用的开发成本。最终芯片测试结果表明,所设计的通用IP核能够驱动段码式LCD正常显示,实现了预期的设计目的。

[1]Chen Ziping,Chuang Chehao,Ker Mingdou.Design on new tracking circuit of I/O buffer in 0.13-/spl mu/m cell library for mixed-voltage application[C]//Proceedings of the IEEE International Symposium on Circuits and Systems(ISCAS 2006),21-24 May,2006.

[2]车晓路,王永生,赵再新,等.液晶显示器驱动电路的设计[J].微处理机,2008,29(3):24-27.

[3]Lanuzza M,Corsonello P,Perri S.Low-power level shifter for multi-supply voltage designs[J].IEEE Transactions on Circuits and Systems II,2012,59(12):922-926.

[4]Huang Yujung,Liu Chihfeng,Chang Shaopin,et al.Design of LCD driver IP for SOC applications[C]//Proceedings of IEEE Asia-Pacific Conference on Advanced System Integrated Circuits,Aug,2004:62-65.

[5]Liu Nan,Liu Shiyu,Yoshimura T.Wirelength driven I/O buffer placement for flip-chip with timing-constrained[C]//Proceedings of IEEE Asia Pacific Conference on Circuits and Systems(APCCAS),2-5 Dec,2012:631-634.

[6]Moghe Y,Lehmann T,Piessens T.Nanosecond delay floating high voltage level shifters in a 0.35 m HV-CMOS Technology[J].IEEE Journal of Solid-State Circuits,2011,46(2):485-497.

[7]Osaki Y,Hirose T,Kuroki N,et al.A low-power level shifter with logic errorcorrection forextremely low-voltage digital CMOS LSIs[J].IEEE J Solid-State Circuits,2012,47(7):1776-1783.

[8]Khorasani M,Benham M,van den Berg L,et al.High-voltage CMOS controller for microfluidics[J].IEEE Trans on Biomed Circuits Syst,2009,3(2):89-96.

[9]Matsumoto A,Sakiyama O,Tokunaga S,et al.Multiphaseoutput level shift system used in Multiphase PLL for low power application[C]//Proceedings of the IEEE Symposium on VLSI Circuits Date of Conference,14-16 June,2007.

[10]Dwivedi D,Dwivedi S,Potladhurthi E,et al.Voltage up level shifter with improved performance and reduced power[C]//Proceedings of the 25th IEEE Canadian Conference on Electrical and Computer Engineering(CCECE 2012),April 29-May 2,2012:1-4.

[11]Zhang Xiaolin,Lin Zhi,Chen Song,et al.An efficient level-shifter floorplanning method for multi-voltage design[C]//Proceedings of the IEEE International Conference on ASIC,2011:421-424.