基于数字电路的二阶Σ-Δ 调制微加速度计*

李 洋,黎晓林,吴 健,周晓峰,车录锋

(1.中国科学院 上海微系统与信息技术研究所 传感技术联合国家重点实验室,上海200050;2.中国科学院大学,北京100039)

0 引 言

Σ-Δ 调制结构由于其精度高的特性,在低速高精度ADC 中已经被广泛采用。随着MEMS 技术的不断发展,加速度计在性能方面也有了很大的提升[1,2],例如:采用真空封装的三明治结构的电容式微加速度计就具有高灵敏度、大动态范围和低热机械噪声等优点[3]。高性能微加速度计通常采用带有静电力反馈的单比特Σ-Δ 调制电路作为其接口电路。

在现有Σ-Δ 调制接口电路中,基本都是基于由运算放大器、模拟开关等器件组成的全模拟电路进行PID 运算和单比特比较。由于Σ-Δ 调制电路的系统稳定性会随着系统阶数的提高而降低,高阶Σ-Δ 调制电路的稳定条件更为苛刻[4]。在这种情况下,模拟电路中存在的各种寄生效应会较明显增大电路设计难度。为了简化模拟电路部分的设计,减少模拟电路的干扰,Colibrys 公司的Dong Yufeng 等提出了使用数字滤波代替模拟积分器方法[5,6]。

本文设计了一种基于现场可编程门阵列(FPGA)的二阶Σ-Δ 调制微加速计,使用数字电路替代部分模拟电路,将基于运算放大器的PID 电路和单比特比较电路使用FPGA 进行数字实现,降低了模拟电路的结构复杂度,减少了模拟电路的噪声。

1 系统结构

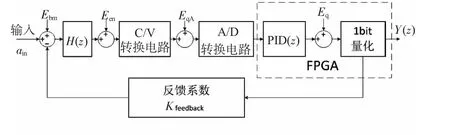

所研究的数字Σ-Δ 调制微加速度计的接口电路基本结构同传统纯模拟电路Σ-Δ 调制结构相类似,具体系统结构如图1 所示。其中,微加速度计为硅—硅键合三明治结构,由上下固定极板和中间可动极板构成。上下两极板通过模拟开关与正负参考电压相连接,以此来检测中间极板的位置;同时,中间极板也在反馈回路中通过模拟开关同正或负参考电压相连接,以此来实现静电力反馈。通过由开关电容和放大器构成的电容/电压(C/V)转换模块,将传感器输出的差分电容值转换成电压值。随后,由前端放大电路将放大后的信号传递给A/D 转换电路,将模拟信号转换为数字信号。通过FPGA 对采样到的电压值进行相关数学处理,得到最终的系统输出,并生成反馈信号反馈回传感器实现电路闭环。由于本文所研究的系统为二阶Σ-Δ 调制系统,因此,PID 电路为相位补偿电路,不包含高阶滤波电路。

图1 数字Σ-Δ 调制微加速度计模块图Fig 1 Module diagram of micro-accelerometer of digital Σ-Δ modulation

1.1 传感器和C/V 转换电路

传感器和C/V 转换电路如图2 所示。Ct(x)是传感器上极板与中间极板间的电容,Cb(x)是下极板与中间极板间的电容。由于电路为闭环电路,反馈回路将使中间极板保持在平衡位置附近,中间极板的偏移量非常小。因此,上下极板与中间极板间的电容同偏移量之间的关系可以近似看作为线性关系,且相对于平衡位置互相对称。可以得到C/V 转换电路的电压输出Vout1为

其中,C0为平衡位置时的极板间电容,x 为中间极板同平衡位置之间的偏移量,d0为平衡位置时中间极板同上下两极板之间的距离。

图2 传感器和C/V 转换电路Fig 2 Sensor and C/V converter circuit

1.2 采样保持和前端放大与A/D 转换电路

这部分电路如图3 所示,有

由于闭环回路中中间极板位置改变很小,Vout2为一个很小的数值,为了能够让A/D 转换电路更好地采样,将Vout2通过前端放大器进行一定倍数的放大,随后,将放大后的电压信号通过10 bit A/D 转换电路进行采样,得到相应的数字信号。

图3 采样保持和前端放大与A/D 转换电路Fig 3 Sample hold,front-end amplifier and A/D converter circuit

系统内部噪声引入的噪声如图4 所示。其中,Ebm为传感器的机械噪声,Een为模拟电路噪声,EqA为A/D 转换电路的量化噪声,Eq为量化器的量化噪声。通过对系统噪声进行分析,可知机械噪声密度为51 ngn/Hz1/2,模拟电路噪声密度在nV/Hz1/2量级,量化器量化噪声在μgn/Hz1/2量级。10 bit 的A/D 转换电路的量化噪声密度在nV/Hz1/2量级,不会给系统引入过大的噪声。

图4 带噪声的系统模块图Fig 4 System module diagram with noise

1.3 PID 与反馈

在传感器设计时,为了降低机械热噪声,传感器会有较低的阻尼和较高的Q 值,这样会带来闭环系统的不稳定。所以,在采用Σ-Δ 数字闭环检测结构来设计Σ-Δ 加速度计时,通常需要在系统的前向通路中加入适当的相位补偿电路。对于二阶的Σ-Δ 数字接口电路,采用补偿系数为0.7的微分结构能很好地保证系统在±1gn的信号输入范围内保持稳定。电路补偿部分的传输函数H(z)为

通过判断补偿后的数据的最高位,取出数据的正负,实现数据的1 bit 量化。随后将量化后的输出传输给反馈回路,相应地给传感器的中间极板加入正、负参考电压,实现力的反馈,最终实现电路闭环。反馈力Ffeedback的大小为

其中,ε 为介电系数,A 为传感器中间极板面积,Vf为反馈电压。

2 系统仿真

为了对系统的功能和性能进行验证,本文对系统进行了相关的仿真。设定系统采样频率50 kHz,过采样率32。通过对系统加入80 Hz 的正弦信号激励,系统的输出频谱见图5。系统输出功率谱中,系统基带内本底噪声密度为-87 dBV/Hz1/2,等效于44.7 μV/Hz1/2。由于电路灵敏度为1.2 V/gn,因此,噪声密度为37 μgn/Hz1/2。

图5 系统的输出频谱Fig 5 Output frequency spectrum of system

3 系统测试

由于采用分离的模拟开关芯片作为系统开关,为了简化电路结构,CV 电路、采样保持电路和前端放大电路都采用单端结构的放大电路。通过搭建PCB 板级系统,并编写相关FPGA 代码,本文初步实现了基于FPGA 的加速度传感器数字Σ-Δ 接口电路。其中,系统工作的采样率为50kHz,传感器谐振频率为780 Hz。最终实现的二阶数字Σ-Δ 微加速计PCB 板如图6 所示。

图6 二阶数字Σ-Δ 微加速计PCBFig 6 PCB of 2nd-order digital Σ-Δ micro-accelerometer

图7 为给系统施加频率为80 Hz 的±1 gn正弦激励信号时的输出频谱。从图中可以看到系统在80 Hz 处有一峰值在-3 dB 的单一信号主峰,同加入激励频率相同。同时,系统基带内本底噪声为-65 dBV/Hz1/2,等效于557 μV/Hz1/2,由于系统灵敏度为1.4 V/gn,系统的噪声密度小于400 μgn/Hz1/2。

由于采用的传感器噪声为51 ngn/Hz1/2,该噪声主要来自于闭环电路系统。整个电路系统为PCB 板级电路,采用分离元件进行电路搭建,并且系统结构也采用的是单端电路的结构。由于系统中开关元件使用的是分离的模拟开关芯片,其开关的导通电阻也较大(约120Ω),该导通电阻给系统会引入较大的电路噪声。同时,由于在电路系统中使用了A/D 转换电路,需要高频控制信号,也给电路引入了一定的信号串扰,会引入较大的噪声。

图7 二阶数字Σ-Δ 微加速度计PCB 板测试结果Fig 7 PCB test result of 2nd-order digital Σ-Δ micro-accelerometer

4 结 论

提出了基于FPGA 的数字二阶Σ-Δ 调制微加速计闭环接口电路的电路结构,电路将采样保持后的数据通过前端放大后转换为数字信号,并对其进行相应的处理。通过搭建二阶PCB 板级电路,测试并验证了该电路结构,并测得系统闭环基带内噪声密度小于400 μgn/Hz1/2。上述研究为以后高阶数字Σ-Δ 调制闭环接口电路的设计提供了指导。

[1] Boser B E,Wooley B A.The design of sigma-delta modulation analog-to-digital converters[J].IEEE J SSC,1988,23(12):1298-1308.

[2] Yazdi N,Ayazi F,Najafi K.Micromachined inertial sensors[J].Proc of IEEE,1998:1640-1659.

[3] 徐伟鹤,林友玲,车录锋,等.一种圆片级硅三层键合的三明治加速度传感器[J].传感技术学报,2008,21(2):230-232.

[4] Schreier R,Temes G C.Understanding delta-sigma data converters[M].Piscataway:IEEE Press,2005:107-109.

[5] Pastre Marc,Kayal Mather,Dong Yufeng.A 300Hz 19b DR capacitive accelerometer based on a versatile front end in a 5th-order ΔΣ loop[C]∥ESSCIRC 2009,Athens:2009:288-291.

[6] Pastre Marc,Dong Yufeng,Nguyen Anne-Marie.A navigationgrade MEMS accelerometer based on a versatile front end[C]∥IECON 2011,Melbourne:IEEE,2011:4038-4043.