基于国产芯片的E1接口重构技术研究与实现*

孙 伟,李 鉴,杨玉发

(西南通信技术研究所,四川 成都 610041)

基于国产芯片的E1接口重构技术研究与实现*

孙 伟,李 鉴,杨玉发

(西南通信技术研究所,四川 成都 610041)

接入路由器中接入板的FPGA和CPU等关键元器件采用国产化芯片,控制数据和业务数据分布式协同处理,同时对板卡进行模块化设计,使得更改接口模块和加载不同程序实现设备的静态重构。采用两片FPGA既能弥补国产芯片性能的不足,也使得不同接入板数据处理模块易于隔离。介绍了接入板的整体设计思路、所要解决的问题和软硬件设计方案,并对CPU、FPGA和接口模块间的通道进行配置。经过测试,E1板卡能很好的完成数据的收发处理。

国产化; E1接入;重构

0 引 言

在信息系统设备中使用的关键元器件及软件方面,国外的CPU、专用芯片、操作系统和数据库等对我们来说类似黑匣子,其安全性未知[1]。为摆脱对国外专用芯片的依赖,保证新型路由交换设备的安全运行,采用的关键技术和基础核心软硬件需要做到自主可控。

传统接入路由器中的接口板设计采用高性能ASIC或网络处理器进行转发,存在着灵活性不足或成本太高的问题。新型接入路由器中接口板采用AISC+FPGA架构[2],控制流和数据流协同处理,极大地提高了路由器的处理能力和容量。

1 总体设计

接入路由器需要具有多业务支持能力、提供丰富的接口类型和多种协议转换机制[3],目前高性能的FPGA因其灵活的可编程性,使得在接入路由交换方面具有独特的优势。接入路由器板卡种类多,在板卡具有不同接口时,利用静态FPGA重构技术载入相应程序,完成不同业务数据流的处理。

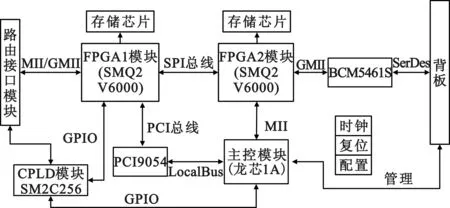

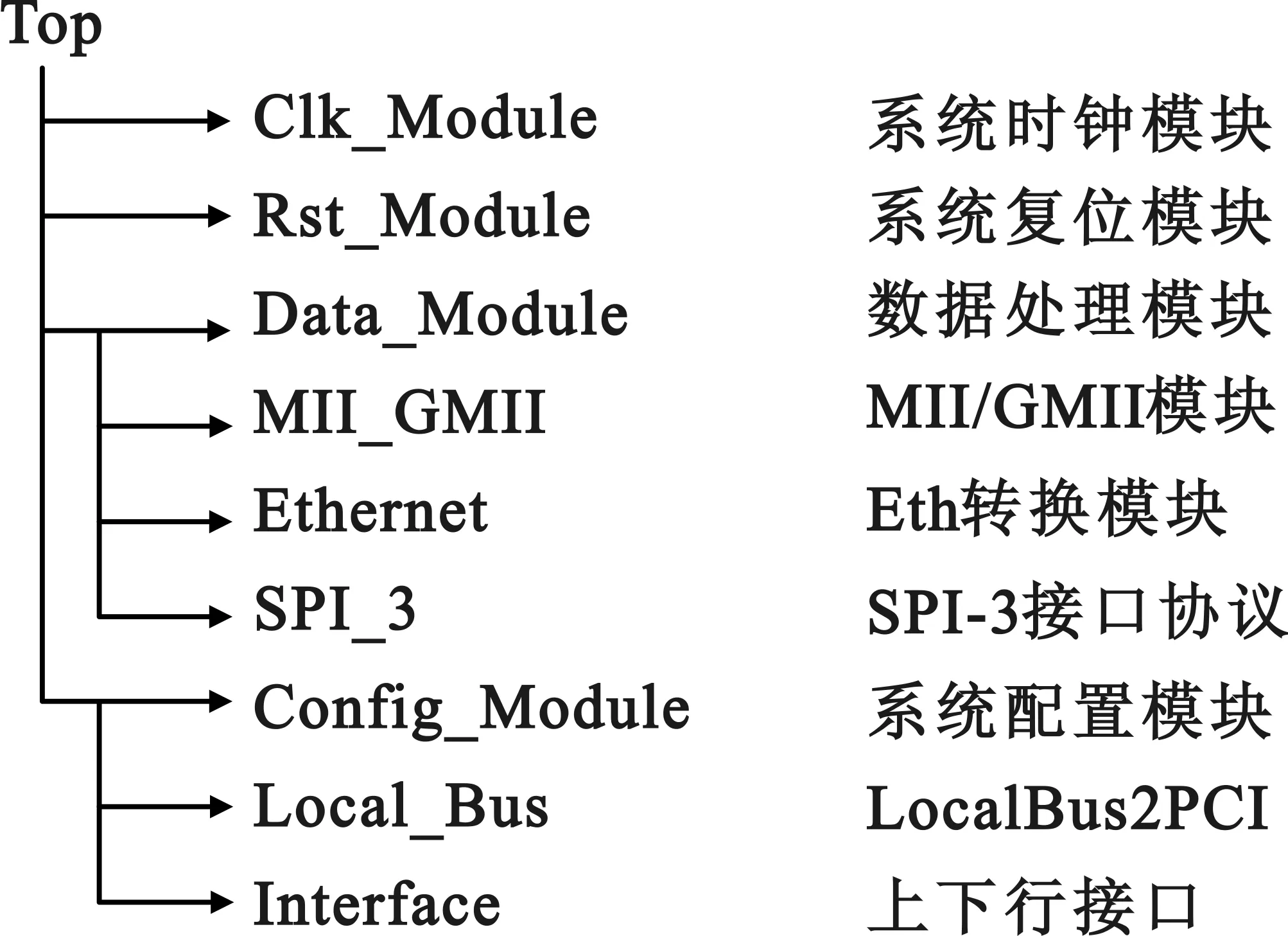

接入板主要完成外部输入数据与Ethernet数据之间的双向转换,包括包头的处理、以太网帧的封装、业务数据和协议的处理,总体设计框图如图1所示[4]。路由接口模块接收外部数据实现数据成帧,之后数据帧送给FPGA模块,FPGA模块实现帧同步和链路层HDLC(High Level Data Link Control,高级数据链路控制)数据包的封装与收发,并转换成Ethernet数据送交给后端背板,主控模块完成接入板的配置和管理,CPLD模块对FPGA进行上电和程序加载的管理。

图1 接入板总体设计框

2 需要解决的问题

接入路由器因其多业务、多接口的特点,需采用模块化的设计方式,支持多种接入板的混插,提供高速转发性能。国外高端FPGA芯片和通信处理器厂家主要有Xilinx公司、Altera公司和飞思卡尔公司,国内主要有京微雅格、国微和龙芯中科公司等。与选用国外成熟的器件方案不同,国产芯片的可参考设计较少。为达到与国外单片FPGA相同的效果,在设计时采用多片FPGA协同工作,使不同逻辑设计合理的分布在不同的FPGA上。国产FPGA需要满足高速接口、增加可用资源、弥补时序能力和硬核短缺。

各个接入板完成的功能不同,通过加载相应的FPGA程序,实现FPGA的静态重构。硬件设计保持接入板后端数据处理和控制部分基本不变,只更改前端接口模块以适应不同应用场景,确保不同接入板载入的VerilogHDL程序存在较小差异。接入路由器完成的功能复杂,数据种类繁多,如何在保障性能的基础上实现快速重构将是本文的难点.

3 软硬件设计

3.1 硬件设计

为保证不同数据接口与接入板的互联互通和FPGA静态重构类型的多样,接口模块采用连接器与接入板主框架相连,使接口模块可复用,并且接口模块不会影响接入板本身的其它模块。数据处理部分的CPLD模块和FPGA模块分别采用国微公司的SM2C256和600万门级的SMQ2V6000,SMQ2V6000与Xilinx公司的Virtex-II系列完全兼容。主控芯片采用龙芯1A处理器,Ethernet接口芯片采用BCM5461S,PCI桥接芯片采用PCI9054。接入板硬件设计框图如图2所示。

图2 接入板硬件设计框

接入板主体部分两片FPGA外接存储芯片供加载程序、扩展FPGA内部资源和数据缓存,FPGA1与FPGA2之间通过SPI-3(System Packet Interface, Level 3)接口协议连接。PCI9054连接龙芯1A和FPGA1,完成PCI转LocalBus总线的功能。此外,CPLD作为全局复位系统管理E1接口模块和两片FPGA,龙芯1A通过背板与接入路由器的主控板交换管理信息。整块板卡以龙芯1A作为管理通道,配置各个芯片,FPGA1和FPGA2作为业务通道,完成板卡的核心功能,包括协议转换、数据封装、报文解析、流分类和监控等功能。

3.2 FPGA设计

作为静态重构的主要器件,FPGA1在前端对来自不同接口的数据进行适配处理,通过MII/GMII/

RMII(供其它类似接入板设计使用)与接口模块连接。静态重构集中在FPGA1内部,载入不同的VerilogHDL程序将相应数据转换为Ethernet数据送往后端,FPGA2保持处理方式不变,实现更改很少的设计完成设备的快速重构。

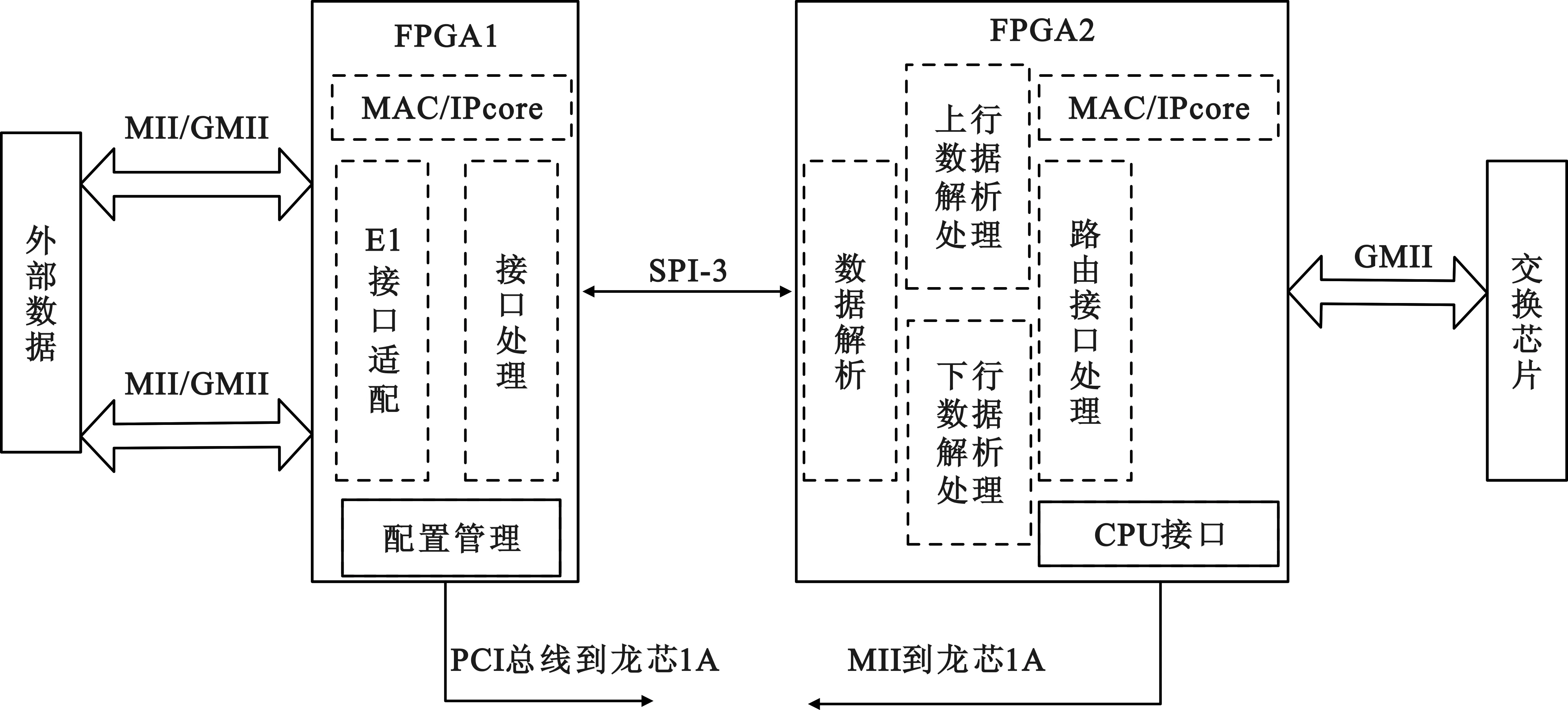

接入板中FPGA的功能划分框图如图3所示,FPGA1与接口模块采用MII/GMII/RMII连接,数据在进入接口模块时进行帧同步,之后在FPGA1中完成包头解析处理,并将数据送往FPGA2进行协议转换和上下行数据解析转发。上行方向,FPGA1对外部数据进行数据缓存同步及格式转换后通过SPI-3总线发送给FPGA2,FPGA2数据解析模块对数据类型进行判断,根据判断结果分别送交给CPU处理模块和后端路由接口处理模块,完成相应数据的分发处理。下行方向数据处理与上行方向相反。

图3 接入板FPGA模块功能划分框

龙芯1A在静态重构中的作用是提供单板管理、驱动配置、状态管理及与主控板交互管理信息等功能。利用SPI总线,通过在FPGA1中编写相应的Verilog程序和龙心1A驱动实现对接口模块中的相应芯片进行初始化。

3.3 通道配置

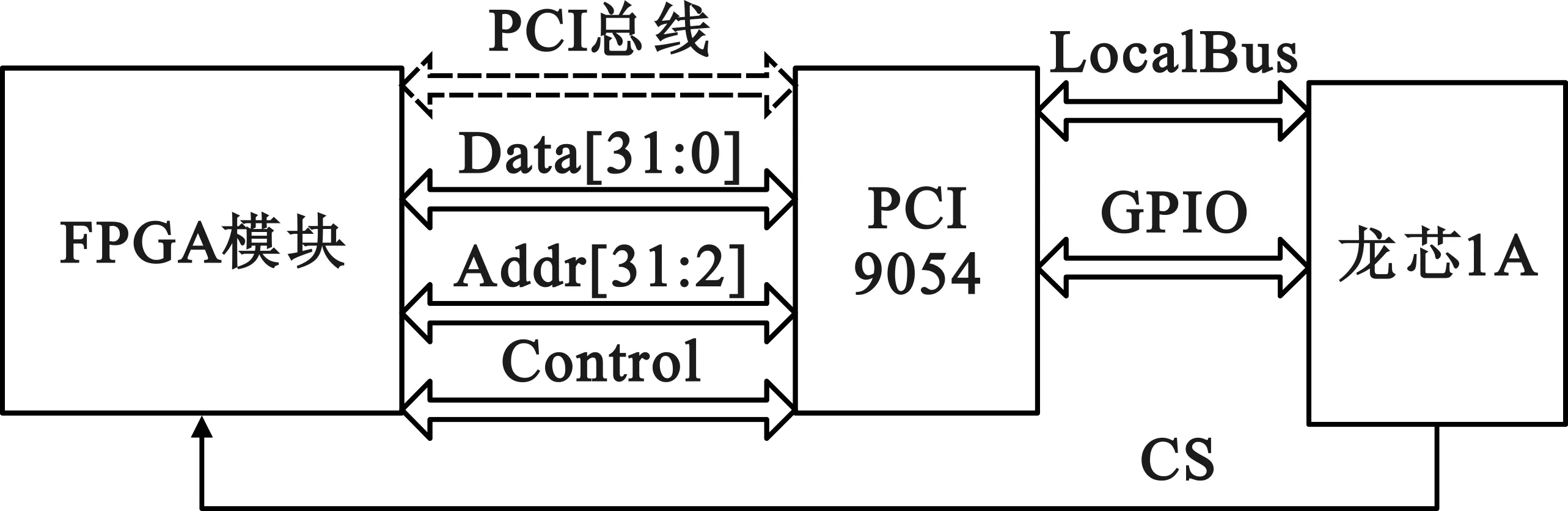

更换不同的模块需要在FPGA1中对龙芯1A与接口模块进行通道配置,为后续数据流的传输提供通道。龙芯1A集成的SPI控制器作为主控端,时钟频率为33 MHz,通过SPI_CS引脚与FPGA1相连,SPI_CS信号与FPGA1输入信号运算的结果实现对模块中芯片的片选。PCI通道管理配置模块如图4所示。

图4 PCI通道管理配置模块

龙芯1A通过PCI9054将PCI转LocalBus总线与FPGA1相连,GPIO部分作为龙芯1A与FPGA1间的备份通信,在PCI出现故障时模拟LocalBus。PCI总线是一种高性能的32位/64位地址数据复用的高速外围设备接口局部总线[5],板卡中龙芯1A作为主设备向FPGA1发送控制信息。PCI9054信号分为3部分:数据线、地址线和控制线,信号先通过FPGA1内部的BUF缓存处理,再对本地数据进行读写控制。

3.4 软件设计

在载入FPGA1用于静态重构的VerilogHDL程序中,对顶层文件采用模块化设计,将接口(MII/GMII和SPI-3)数据处理模块Data_Module和配置模块Config_Module分开处理。顶层设计层次描绘如图5所示。

图5 接入板软件顶层设计结构

MAC接口可配置于10 M/100 M/1 000 M模式下,并调用IP核完成数据的收发处理,数据收发时用FIFO进行同步缓存。本文将接口速率配置为100 M,MAC Core参数如下:

assign mac_configuration_vector = {68′hB8B16_

00_00_00_08_00_03};

经过处理的数据合路后通过32位单向SPI-3总线传输,SPI-3接口协议是一种应用于SONET/SDH PHY层和链路层的接口[6],拥有独立的发送和接收接口,时钟为133 MHz,可使PHY和链路层间的操作更加简洁。FPGA2根据包头信息分别发往搜索引擎传输到下一级或者龙芯1A进行处理。配置模块完成FPGA1与周围芯片的接口配置、寄存器配置、中断处理以及端口MAC地址。FPGA1的配置寄存器语句如下:

assign board_info_reg = {24′h0,fpga2_state,

fpga1_state,board_type,board_slot};

4 技术实现

本文以E1接入板为例,阐述具体设备在静态重构方面的设计。E1是国际电联标准化部门(ITU-T)制定并由欧洲邮政与电信协会(CEPT)命名的数字传输系统一次群(PCM30)标准,我国采用E1标准作为脉冲编码调制(PCM)系统和窄带综合业务数字网(N-ISDN)的基群。E1线路具有延迟稳定,时间同步精确的优点[7]。

4.1 数据收发处理

8路E1接口模块采用DS26514和DS33W41完成数据成帧和转Ethernet的功能,通过MII ( Medium Independent Interface,介质独立接口)与后端的FPGA1相连。

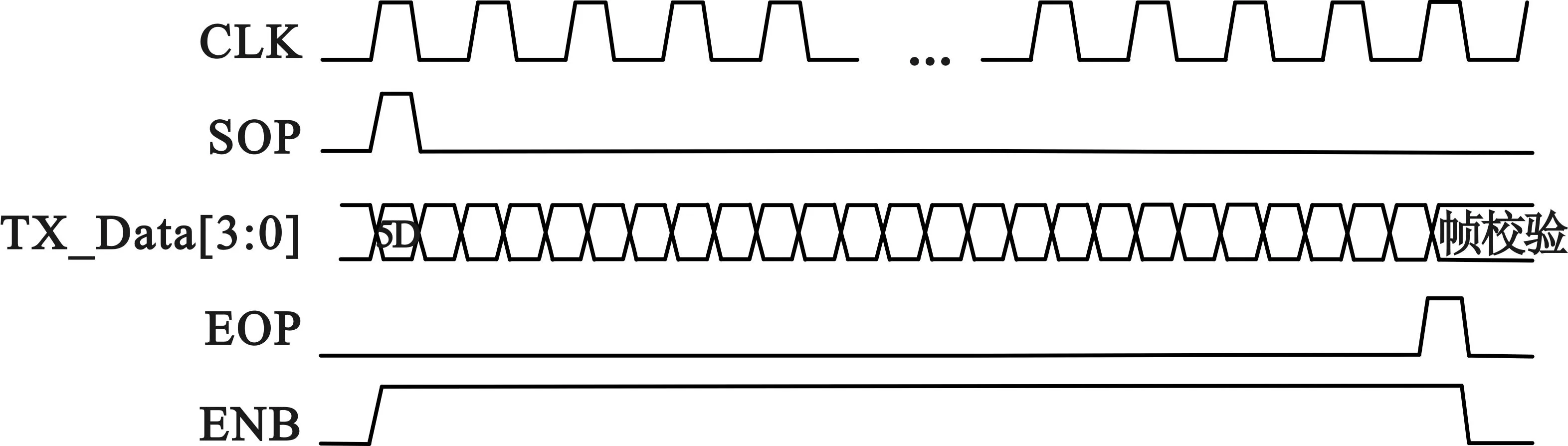

对E1模块、FPGA1、PCI9054和龙芯1A通道配置完成后,模块间进行数据收发处理。每个E1模块有4路E1数据,E1接入板通过DB15接口接入8路E1数据,两个E1模块通过MII与FPGA1连接。MII是IEEE802.3规定的与介质无关接口,负责MAC和以太网PHY之间的通信。MII共16根信号线, 可分成发送,、接收和网络状态三组信号线。MII数据线为4位数据,MII一个完整的数据帧包括帧间隔、前导段、帧起始符、数据和帧结束符,帧起始符序列为10101011,即通过“5D”字段判断数据帧的起始。E1数据通过MII传输到FPGA1, FPGA1工作于PHY模式下,采用外部输入的25MHz时钟。采用自定义的MII数据格式如图6所示,4位数据传输时,SOP信号和EOP信号分别指示数据开始和结束,ENB信号使能数据。

图6 MII数据帧格式时序

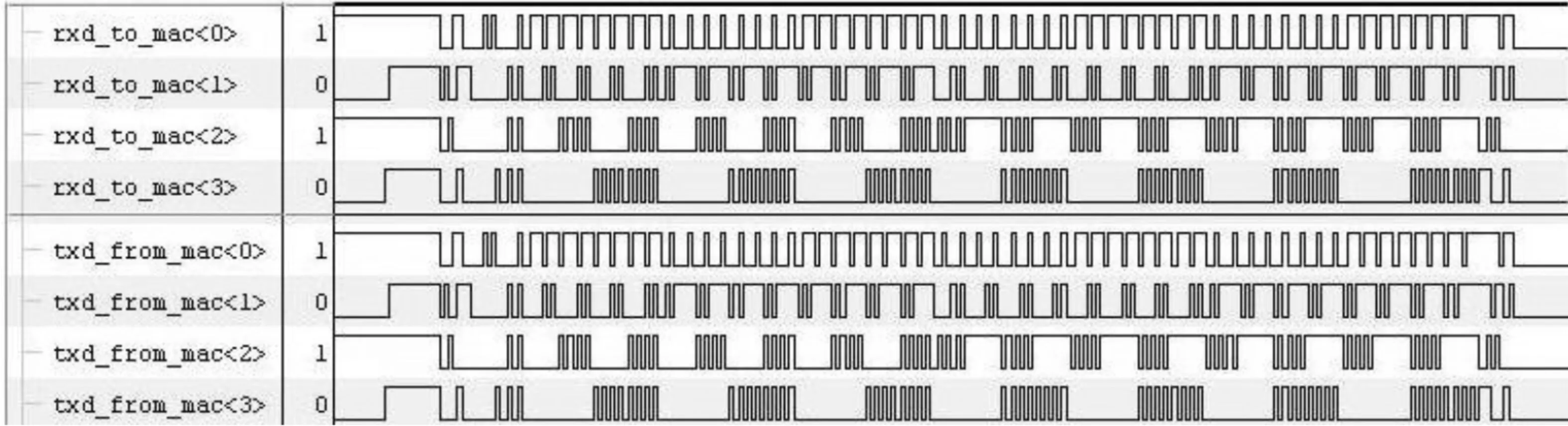

接收的E1数据通过FPGA内部的Ethernet IPCore将数据传输给FPGA2。对IPCore进行设置,根据phy的速度指示配置MAC速度。在FPGA1内部对两个E1模块进来的8路数据进行帧同步,通过FIFO缓存后打上自定义头部标识,用以指示是哪一个模块的数据,然后进行合路并无优先级输出,通过SPI-3送到FPGA2模块进行数据的解析处理。

4.2 测试结果

通过龙芯1A读取两个E1模块中4个芯片的寄存器数据,返回芯片标识和寄存器初始化地址,表示通道可以正常连通。对E1链路的八个端口进行闭环测试,可得到端口状态正常工作。在FPGA1内部构造满足MII数据格式的数据,设定为1 s的间隔时间向外发送一次数据,数据经过FPGA1内部的IPCore后发往E1模块,环回后FPGA1接收数据并发往FPGA2处理。测试结果如图7所示。

图7 数据环回测试结果

5 结 语

接入路由器中接入板的核心器件FPGA和CPU采用国产元器件,作为消除进口元器件“预置后门”威胁的基础,为整个系统的自主可控建立一个硬件平台。板卡采用可进行静态重构的模块化设计,将接口部分和后端数据处理及控制部分弱相关,通过改变接口模块、FPGA1程序和CPU驱动程序,可将板卡改造成所需要的接入类型,实现快速静态重构。通过测试,验证了基于国产芯片的E1接入板能很好的完成数据处理及控制功能,具有良好的可靠性,为以后相似设备的国产化提供参考。

[1] 李冰心. 基于龙芯1A的可信移动终端设计研究[J]. 舰船电子工程,2013,33(02):79 - 85. LI Bing-xin. Design and Implementation of a Trusted Mobile Computer based on Godson 1A Processor[J]. Ship Electronic Engineering, 2013,33(02):79-85.

[2] 汪超. 以太网交换架构路由器中基于FPGA的E1接口设计[D]. 上海:上海交通大学,2009. WANG Chao.E1 Interface Design based on FPGA in Ethernet Switch Router[D].Shanghai Jiaotong University,2009.

[3] 吴捷,施彦媛.一种新型集群路由器智能管理技术的研究[J].通信技术,2013,46(08):65-67. WU Jie, SHI Yan-yuan.Smart Management Technology of A New Cluster Router[J]. Communications Technology, 2013,46(08):65-67.

[4] 杨小冬,王俊芳. 基于时分复用的E1中继单元设计[J]. 无线电工程,2012,42(10):45-60. YANG Xiao-dong, WANG Jun-fang. Design of E1 Relay Unit based on TDM[J].Radio Engineering,2012,42(10):45-60.

[5] 卢一男,张会新,安震等. 基于PCI和FPGA的信号源设计[J]. 计算机测量与控制,2012, 20(09):2584-2596. LU Yi-nan, ZHANG Hui-xin, AN Zheng, et al. Design of Signal Source based on PCI and FPGA[J].Computer Measurement & Control,2012,20(09):2584-2596.

[6] Richard Cametal. System Packet Interface Level3 [S].SPI-3 Specification Optical Interface Forum, 2000.

[7] 闫辉,胡永辉,侯雷. 基于 E1 接口的时间同步系统关键模块设计与仿真[J]. 时间频率学报,2012,35(04):212 - 217. YAN Hui, HU Yong-hui, HOU Lei. Design and Simulation of Key Modules of Time Synchronous System based on E1 Interface[J]. Journal of Time and Frequency, 2012, 35(04): 212-217.

E1 Interface Reconfiguration Technology and Its Implementation based on Domestic Chip

SUN Wei, LI Jian, YANG Yu-fa

(Southwest Research Institute of Communications,Chengdu Sichuan 610041,China)

Domestic chips are usually used in key components for access board of access router, such as FPGA and CPU, control data and business data are in distributed collaborative process, and the modular design makes the change of card interface module and the loading of different programs realize equipment static reconfiguration. The adoption of two pieces of FPGA could make up the inadequacy of domestic chip performance, and makes easy the isolation of different access board data processing modules. The overall design of access board, the problems to be solved, the hardware and software strategies are described. The channels of between the CPU, FPGA and interface module are configured. Experiment indicates that this E1 board could fairly implement data receiving and dispatch process.

domestic; E1 access; reconfiguration

2015-04-17;

2015-08-01 Received date:2015-04-17;Revised date:2015-08-01

TN911

A

1002-0802(2015)09-1096-05

孙 伟(1990—),男,硕士研究生,主要研究方向为通信网络;

李 鉴(1975—),男,硕士,研究员,主要研究方向为通信网络;

杨玉发(1984—),男,硕士,工程师,主要研究方向为网络传输与接入。