多速信号处理中采样率转换的DSP实现*

宁少雄 陈 飞 张文娟 高 俊

(1.海军工程大学科研部 武汉 430033)(2.海军工程大学电子工程学院 武汉 430033) (3.海军陆战学院模拟训练中心 广州 510430)

多速信号处理中采样率转换的DSP实现*

宁少雄1陈 飞2张文娟3高 俊2

(1.海军工程大学科研部 武汉 430033)(2.海军工程大学电子工程学院 武汉 430033) (3.海军陆战学院模拟训练中心 广州 510430)

采样速率转换是现代数字信号处理领域中一个重要组成部分,在通信、雷达等领域有广泛应用。论文首先介绍了信号内插、抽取及采样率转换的基本原理并给出了Matlab仿真结果。然后给出了基于DSP的采样率转换设计与实现,并分析了相关汇编注意事项和结果。

多速信号处理; 内插; 抽取; 采样率转换; DSP

Class Number TN911.22

1 引言

在通信、雷达等数字信号处理领域,经常会遇到抽样率转换的问题[1~3]。一方面要求数字系统能工作在多抽样率状态,以适应不同抽样信号的需要;另一方面,对一个数字信号,要视对其处理的需要及其自身的特征,能在一个系统中以不同的抽样频率出现。例如,当需要将数字信号在两个具有独立时钟的数字系统之间传递时,则要求该数字信号的抽样率要能根据时钟的不同而转换。比如在音频信号处理时,就存在着多种抽样频率,得到立体声声音信号所用的抽样频率是48kHz,CD产品用的抽样率是44.1kHz,而数字音频广播用的频率是32kHz[4~5]。对一个信号抽样时,若抽样率过高,必然会造成数据的冗余,则希望能在该数字信号的基础上将抽样率降下来。一个数字传输系统,既可传输一般的语音信号,也可传输视频信号,这些信号的频率成份相差甚远,因此,相应的抽样频率也相差甚远[6]。因此,该系统应具有传输多种抽样率信号的能力,并自动地完成抽样率的转换。多抽样率数字信号处理的核心内容就是信号抽样率的转换及滤波器的实现[7~8]。

2 基本原理

2.1D倍抽取

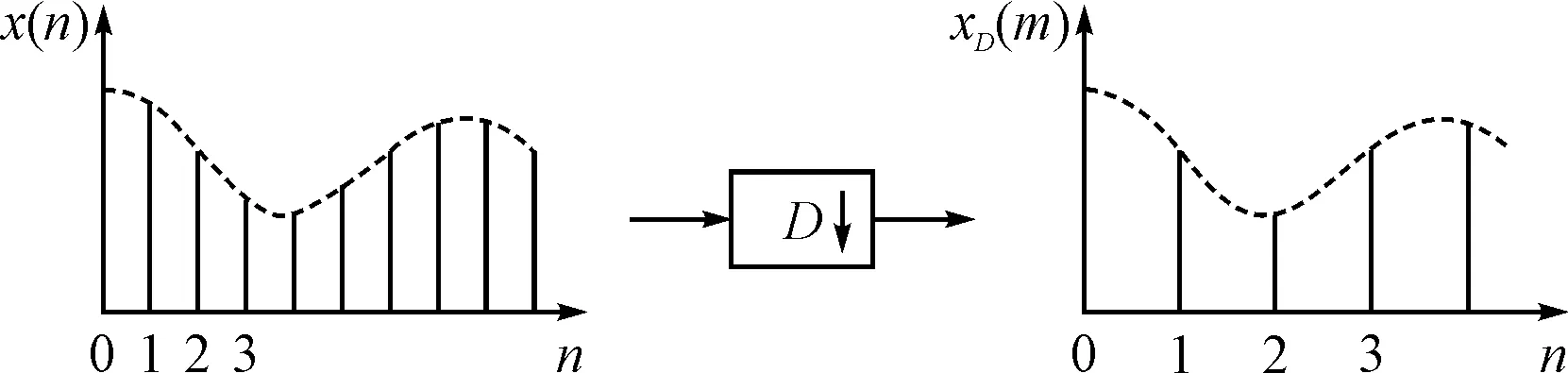

将抽样序列x(n)的速率降低D倍的过程称为抽取。为避免降低速率时产生混叠,对原序列进行低通滤波是必不可少的。将原始采样序列x(n)每隔D-1点取一个值,形成一个新的序列xD(m),有

xD(m)=x(mD)

其中,D为正整数。抽取过程如图1所示。

图1 抽取过程示意图

如果序列x(n)的采样率为fs,则抽取后的序列的xD(m)采样频率为fs/D,抽取后采样率降低了D倍。抽取后进行傅氐变换可得[8]

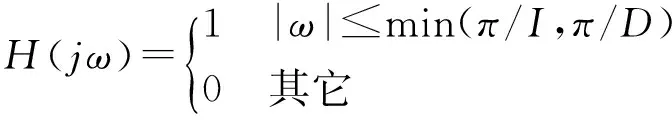

为防止频谱混叠,在抽取前进行抗混叠滤波。抽取的倍数应满足如下条件[2]

其中,fmax为信号的最高频率。

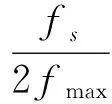

2.2I倍内插

内插和抽取的作用正好相反,它在两个原始序列的样点之间插入I-1个值。设原始序列为x(n),则内插后的序列xI(m)为

内插过程如图2如示。

图2 内插过程示意图

图3 信号内插前后的频域图

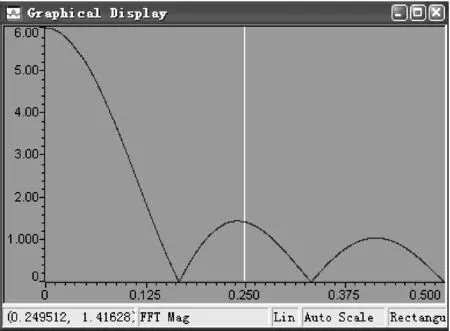

内插后信号的频谱为XI(jω)=X(jωI)。内插后对信号进行低通滤波,滤波器的带宽为π/I。图3给出Matlab仿真的信号内插前后的频率图。

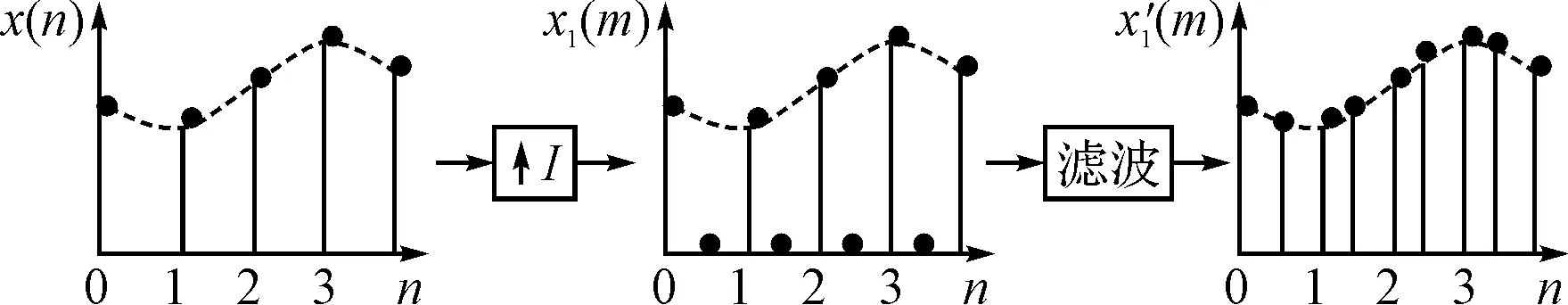

2.3 采样率转换原理

先内插后抽取的任意因子的采样率转换,需要注意的是内插后滤波器和抽取前的滤波器可合并为一个,此时要求所替代的滤波器的频率特性满足下式[9]:

Matlab提供了resample函数用于采样率的变换,调用格式为[10]

y=resample(x,I,D)

其中x为原始序列,y为采样率变换后的序列,I为内插的倍数,D为抽取的倍数。在采样率转换的过程中需要一个低通滤波器,在该函数中自动采用了低通滤波器,它是按照等波动最优化原理设计的,使我们省去了滤波器设计的工作。

3 采样率转换的DSP实现

3.1 滤波器系数存放

内插时由于原信号两采样点之间插有0值,在进行滤波时由于滤波即为乘累加,即将每一个采样点值进行阶数次的乘累加运算,得到一个输出结果。然而,中间的0值无论如何都会导致乘累加部分结果为0,所以可以重新安排滤波器系数在DSP缓冲区中的储存位置,使得简化运算。其原理如图4所示。

图4 滤波器系数存放及输入输出关系图

其滤波过程为

y0=x0·h56+x1·h48+…+x7·h0

y1=x0·h57+x1·h49+…+x7·h1

⋮

y7=x0·h63+x1·h55+…+x7·h7

64个抽头系数的内插滤波器,每输入8个数据样点,滤波输出数目也是8。每存储1个信号数据,要循环读出8次。根据此原理,将MATLAB中得到的滤波器系数重新安排,放入DSP的inc文件中存储。

3.2 数据观察显示

在进行调试,要注意到寄存器窗口各寄存器值的变化是否按设计来跑,同时,要在储存空间观察数据的读写。为了可视化,借此来验证程序编写正确性,下面给序列采样率转换前后在CCS中观察到的频域图。

图5 输入序列的频域图

图6 内插6倍后的频域图

图7 内插6倍后低通滤波频域图

3.3 DSP编程注意事项

3.3.1 数据存放

在CCS仿真时分别存放输入序列和滤波器系数数据,由于C54x为16位定点芯片,其存放格式为Q15位。下面分别说明DSP数据存在: 1) 输入序列。由于全1序列具有较好的实验性和观察性,我们这里使用的为全1,点数取6即可。而因为使用的为16位带符号整型数据,可以表达的数据范围为8000h~7FFFh,即-1~0.9969,因此开辟缓冲区存放6个7FFFh。 2) 滤波器系数。在Matlab中生成21阶低通滤波器系数,小数位为15位,存放在DSP中需要进行转换,即乘215=32768,后将小数位四舍五入,使用floor函数即可方便生成需要的数据。

3.3.2 程序编写

在进行汇编语言程序编写时,由于汇编可读性和可写性差,需要注意的问题较多。 1) 循环缓冲区的开辟。在内插后进行滤波时,由于采用循环缓冲区和双操作数寻址方式实现FIR滤波,必须满足不等式2k>N,N为循环缓冲区的长度,k为起始地址最低有效位的个数,由于已人为将输入序列最大长度定为64,所以在进行循环缓冲区开辟时,至少要保证起始地址后6位为0。 2) 辅助寄存器的使用。由于在循环寻址时无论内插、滤波、抽取都要用到AR0寄存器,且其赋值都不同,需要加以区别。同时在使用双操作数时只能使用的辅助寄存器为AR2~AR5,且要十分注意指针指向的位置。

4 结语

本文研究了多速率信号处理的采样率转换实现技术,介绍了内插、抽取和采样率转换的基本原理,并利用Matlab进行了仿真分析,在此基础上,基于定点DSP的实现了内插和抽取的采样率转换,分析了DSP汇编程序设计实现时需要注意的基本问题,最后给出了DSP仿真结果。

[1] 宗孔德.多抽样率信号处理[M].北京:清华大学出版社,1996.

[2] Chang D C, Wu W R. Maneuvering Target Tracking with High-Order Correlated Noise-A Multirate Kalman Filtering Approach[J]. Wireless Personal Communications,2001,20(17):103-123.

[3] Xia X G, Suter B W. Multirate Filter Banks with Block Samlping[J]. IEEE Transactions On Signal Processing,1996,44(3):484-496.

[4] Franca J, Mitra S K. Multirate Analog-Digital Systems for Signal Processing and Conversion[C]//Proceedings of the IEEE,1997,85(2):242-262.

[5] Liang Jie, Trac D. DCT-Based General Structure for Linear-Phase Paraunitary Filterbanks[J]. IEEE Transactions On Signal Processing,2003,51(6):1572-1580.

[6] 刘春霞,王飞雪.FIR内插滤波器结构与实现综述[J].舰船电子工程,2005,25(2):19-23.

[7] Vaidyanathan P P. Filter Banks in Digital Communications[J]. IEEE Circuits and Systems Magazine,2001,1(2):4-25.

[8] Hentschel T, Fettweis G. Sample Rate Conversion for Software Radio[J]. IEEE Communications Magazine,2000,38(8):142-150.

[9] Huang D F, Chen B S. A Multi-input-multi-output System Approach for the Computation of Discrete Fractional Fourier Transform[J]. Signal Processing,2000(80):1501-1513.

[10] 胡广书.数字信号处理—理论、算法与实现[M].北京:清华大学出版社,2003.

DSP Realization of Sample Rate Conversion in Multi-Rate Signal Processing

NING Shaoxiong1CHEN Fei2ZHANG Wenjuan3GAO Jun2

(1. Office of Research & Development, Naval University of Engineering, Wuhan 430033) (2. College of Electronic Engineering, Naval University of Engineering, Wuhan 430033) (3. Simulation Training Center, Naval Marine Academy, Guangzhou 510430)

Sample rate conversion is the crucial part in digital signal processing, which has practical application in communication, radar domain. In the paper, the theory of extraction of signal, interpolation of signal, sample rate conversion are introduced and the simulation analysis is provided by Matlab tool. Then the design and realization of sample rate conversion are presented using fixed-point DSP, and some relevant issues are analyzed to bring forward the result.

multi-rate signal processing, interpolation, extraction, sample rate conversion, DSP

2014年7月14日,

2014年8月20日

宁少雄,男,硕士,工程师,研究方向:工程管理及网络应用。陈飞,男,硕士研究生,工程师,研究方向为信号调制与编码技术。张文娟,女,硕士,讲师,研究方向:通信工程及网络管理。高俊,男,教授,博士生导师,研究方向:通信理论与技术。

TN911.22

10.3969/j.issn1672-9730.2015.01.027

——信号处理