一种相位量化DAC中电流源电路研究

魏 恒,邹振杰

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

一种相位量化DAC中电流源电路研究

魏恒,邹振杰

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

摘要由于相位量化数模转换器(DAC)转换精度和转换速度的不断提高,因此电流源模块需要满足更高的性能要求。介绍了一种电流源的电路结构,分析了该结构的优缺点,采用了一种减小工艺误差和器件失配的版图设计方法。基于90 nm CMOS工艺模型进行仿真,仿真结果表明,在2 GHz的工作频率下该电流源结构仍能保持较大的输出阻抗特性和较高的输出精度。

关键词相位量化DAC;电流源;输出阻抗

0引言

现代雷达对抗中相参雷达[1]被广泛应用,因此相参干扰技术中的数字射频存储器(DRFM)得到了迅速的发展[2-4]。DRFM芯片主要包括相位量化ADC、相位量化DAC和数字储存和处理等部分。而相位量化DAC主要是将数字部分处理完成的信息恢复为模拟信号,再由模拟单元发送出去。它的特性决定了DRFM对原始信号的复现能力。

随着相参干扰技术的快速发展[5,6],相位量化DAC的工作速度和精度不断提升,对内部电路尤其是电流源的要求也越来越高。针对这些问题,采用了共源共栅结构的电流源结构,来提高电流源的输出阻抗,消除在高频情况下负载对电流源的影响,并在版图[7]设计中减轻工艺误差和器件失配等问题引入的误差和毛刺。并基于90 nm CMOS工艺模型完成了对电路的仿真设计,表明该电流源结构在2 GHz的工作频率下,仍能保持较大的输出阻抗特性和较高的输出精度。

1相位量化DAC系统架构

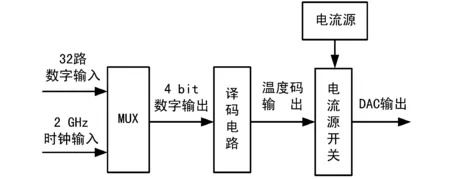

相位量化DAC系统结构主要包括并串转化器模块(MUX)、数字译码电路、电流源模块及其开关电路等4部分,它的量化精度为4 bit,其工作过程如图1所示。

图1 4 bit相位量化DAC结构

DRFM数字部分传输过来的32位数据由MUX模块转化为4位串行的数字信号,译码电路将这4位数字信号转换为可以控制电流源开关的控制信号,电流源在开关的调控下完成对信号的恢复输出。

2电流源电路工作原理

相位量化DAC的阶梯是按照正弦波的形状变化的,如果输入是温度相位码,一个4位相位量化DAC的输出表达式为:

(1)

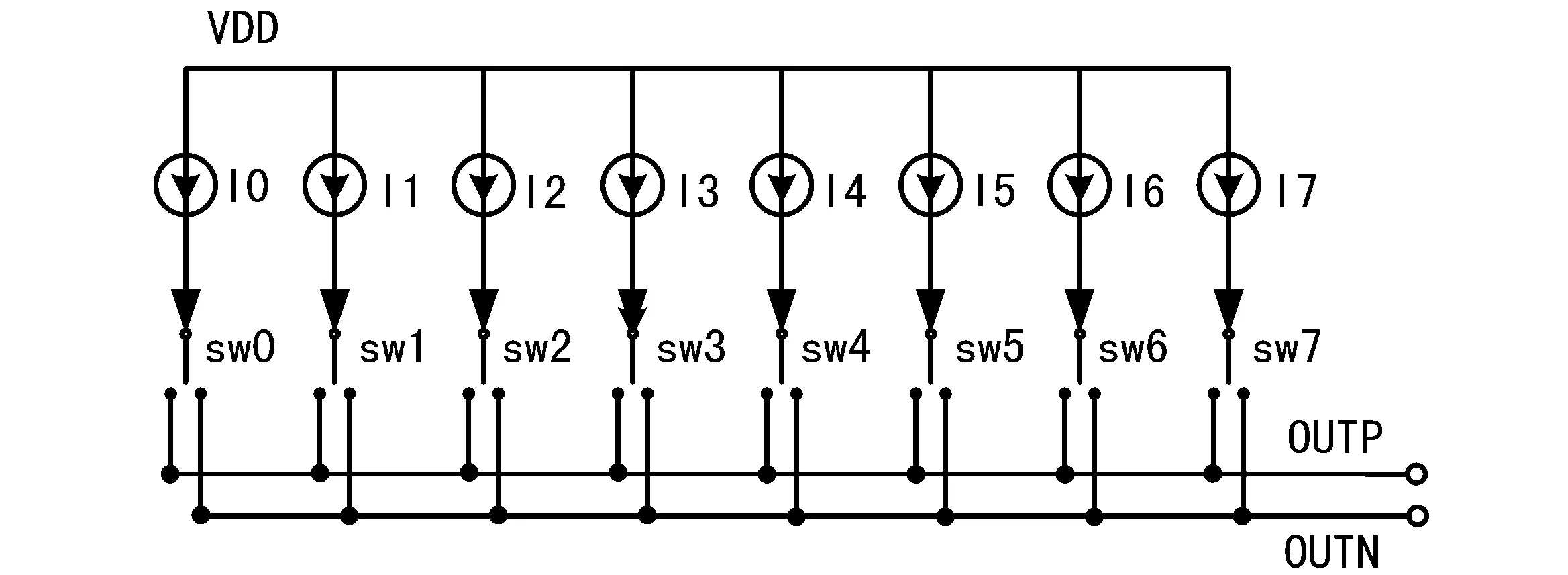

式中,bn为1或0,由输入数据决定;an是每一位的权重,它的值为0.076、0.214、0.324、0.383、0.383、0.324、0.214、0.076。为了实现高速,采用电流源型DAC方案,其结构如图2所示。

图2 电流源型DAC方案

8个电流源的权重比为76∶214∶324∶383∶383∶324∶214∶76,从ADC输出的8位数据分别控制开关sw0、sw1~sw7,输出端口OUTP和OUTN加上50 Ω负载后产生输出波形。

DAC的设计中面临的主要问题包括:高频时电流源输出阻抗的下降,不同权值的电流源匹配,MOS管的热噪声,时钟馈通效应和控制信号的毛刺等问题。而对于4 bit的相位量化DAC来说,假设满量程输出为1 000 mV,则最小的量化输出为76 mV,因此电路的热噪声并不是恶化性能的主要因素。而控制信号的毛刺问题可以通过严格的版图布局和驱动电路的调整来消除。如何解决高频时电流源输出阻抗的下降和不同权值的电流源匹配是本芯片设计的难点和重点。

3电流源电路和版图设计

3.1 电流源电路设计

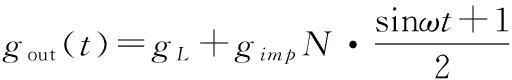

假设电流源的个数为N,DAC输出的正弦波为sinωt,则在时刻t开启的开关个数为[8,9]:

(2)

对于DAC的输出端口,在t时刻输出阻抗就为负载电阻和n(t)个单位电流源输出阻抗的并联,关系式为:

(3)

此时,DAC的输出电压为:

(4)

式中,I是每个电流源上产生的输出电流;gL和gimp分别为负载跨导和单位电流源的输出跨导,对Vout(t)进行泰勒级数展开:

(5)

式(5)中各个参量的表达如下:

(6)

(7)

(8)

(9)

(10)

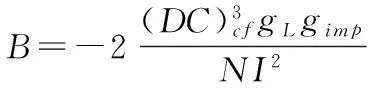

从Vout(t)的泰勒级数展开式中可以得出二次谐波值为:

(11)

一般来讲二次谐波决定了DAC输出波形的无杂散动态范围。

因此对于给定精度的DAC,单位电流源输出阻抗为:

(12)

对于10 bit DAC来说,要求的SFDR值为60 dBc,如果负载电阻为50 Ω,N=1 024,则电流源的输出阻抗要达到10 MΩ,这在低频下容易满足,在高频下由于寄生电容的存在,输出阻抗严重下降。

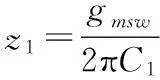

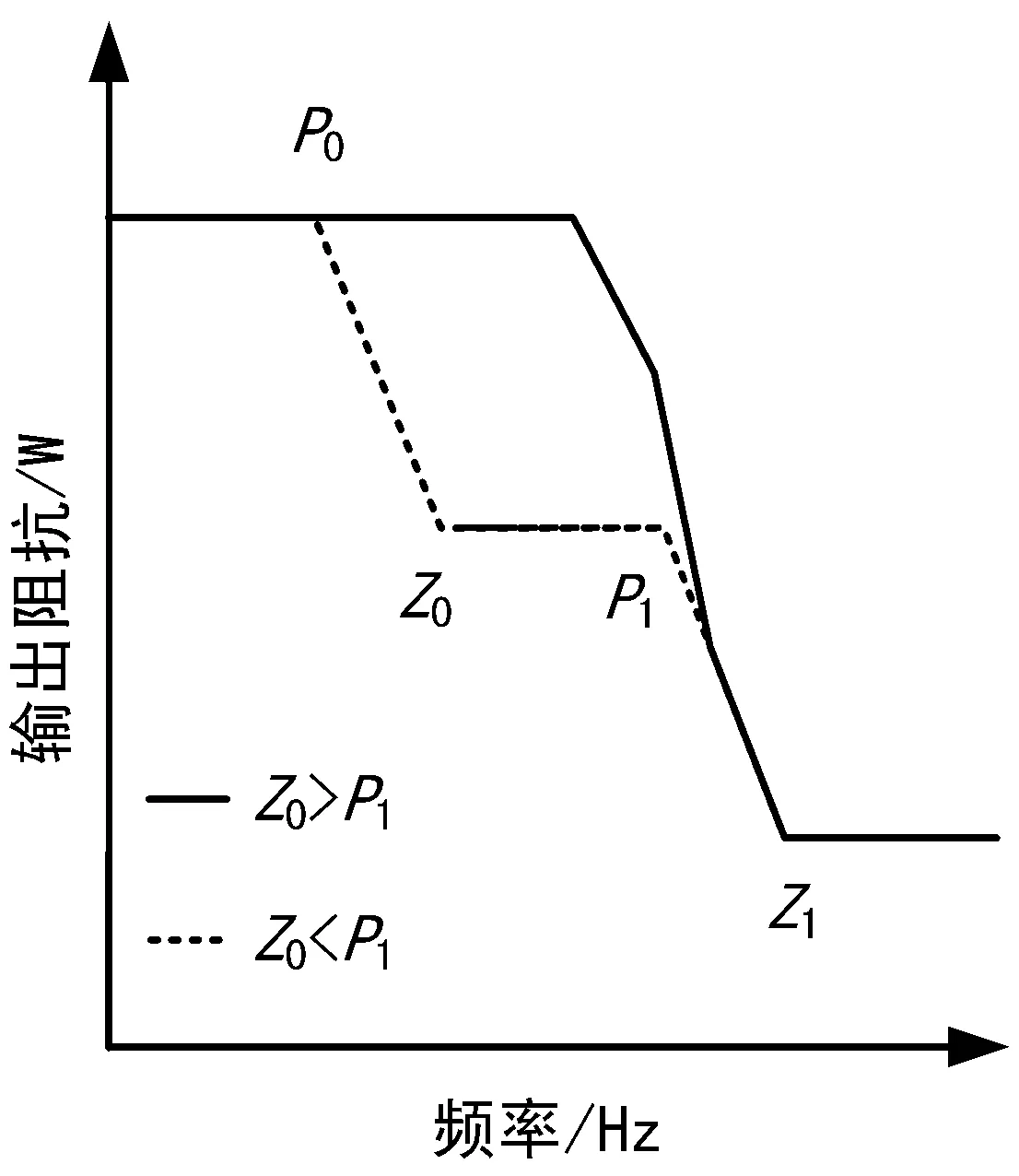

寄生电容主要包括MOS管自身的寄生电容和版图设计中引入的走线和线间电容。而版图引入的电容在设计中很难完全消除,尤其是在高频工作条件下。因此在电路设计阶段就必须采用可行的办法来提高电流源的输出阻抗。在该文的设计中电流源的结构采用的是共源共栅结构,如图3所示,该结构将电流源的输出阻抗增加了共栅管的本征增益,同时,抑制了高频工作时输出阻抗的下降。

图4中各个参量表达为:

(12)

(13)

(14)

(15)

这种结构由于其较大的输出阻抗在现在的电流源DAC中常被采用,从图4中可以得出C0和C1共同决定了输出阻抗的带宽,在电流源的设计中要尽可能地减小C0和C1。因此在采用共源共栅结构可以极大程度地增加电流源输出阻抗,提高电流源输出特性。

图3 共源共栅电流源结构

图4 输出阻抗与频率关系

3.2 电流源版图设计

在电路设计中,电流源电路是按照固定的权重设计的,但是由于工艺偏差和器件失配,会使电流源之间的权重关系发生变化,导致电流源的输出偏离设计值,在版图的设计中,要采用一定的办法来克服这些影响,在本文的电流源版图设计上,采用Q2Random Walk[10]的方法,如图5所示,基本原理是假设电流源电路一共有16×16个器件,首先,将电流源的整体版图布局分为16个子部分,如图中的A、B、C等,这16个子模块是随机的排布在版图的16个区域,然后,将一个子模块内部再划分为16个区域,如图中的1、2、3等,再把16个器件随机分布在这16个区域,采用这样的方法,可以将工艺偏差和器件失配的问题随机化,而不是集中于某1个或几个电流源上。

图5 Q2Random Walk版图设计方法

除此之外,在电流源开关电路的版图设计上,要采取屏蔽措施,减小周围电路上的信号对开关电路的影响,同时控制信号到开关栅极的走线要尽量保证等长,使开关的开启和关闭能够保持同步。

4仿真结果分析

使用Cadence Spectre 仿真器对相位量化DAC的电流源电路进行仿真,在90 nm CMOS工艺模型下,Corner设置为:mos=tt,temperture=27 ℃,Vdd=1.2 V。电流源的输出阻抗结果如图6所示。

在低频区域,电流源的输出阻抗可以达到3 GΩ以上,随着工作频率的增大,受到节点电容的影响,电流源的输出阻抗开始快速下降,当输入信号频率为2 GHz时,电流源的输出阻抗仍大于56 kΩ。

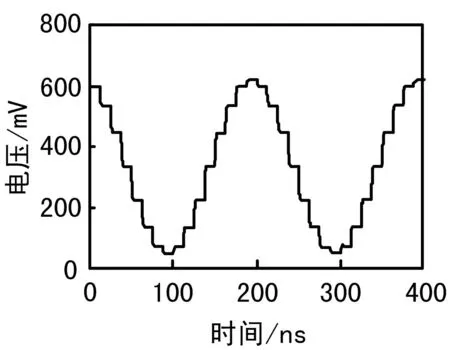

为了较好地观察电流源每个支路的权重是否正确,给电流源输入一组变化速率为80 MHz的温度码,电流源输出为5 MHz的正弦波,这样可以方便地观察出每个温度码对应的模拟输出,如图7所示。

图6 输出阻抗与频率关系

图7 电流源输出波形仿真

通过Cadence仿真软件可以计算出每一级电流源输出电压差值的比值是:21.6∶63.3∶89.7∶109∶109∶89.7∶63.3∶21.6,与理论上计算出的比值基本一致。

将电流源输出信号做快速傅里叶分析后得到该共源共栅结构的电流源输出频谱特性如图8所示。从仿真结果可以看出,SFRD达到了-56 dBc,远远满足4 bit量化精度的要求。

图8 相位量化DAC整体电路的输出频谱

5结束语

采用共源共栅结构的电流源模块,通过提高电流源的输出阻抗来消除在高频情况下负载对电流源的影响,电路结构简单。同时在电流源版图设计上,采用Q2Random Walk方法,减轻工艺误差和器件失配等问题引入的误差和毛刺,最终使电流源电路在2 GHz时钟速率下保持较大的输出阻抗和较高的输出精度,完成对模拟信号的恢复。对同类产品的设计具有一定的借鉴作用,满足了高速、高精度相位量化DAC的应用需求,具有广阔的应用前景。

参考文献

[1]张正平.雷达发射机频率稳定度的研究[J].无线电工程,2010,40(3):1-2.

[2]丁鹭飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,2002:16-35.

[3]陈旸.搜索雷达抗干扰技术分析[J].无线电工程,37(7):44-46.

[4]邹振杰,陈明辉,曲明.一种4bit相位量化ADC电路分析[J].无线电通信技术,2011,37(6):40-42.

[5]胡伟东,吕昕,高本庆.超宽带雷达技术的新进展[J].无线电工程,2005,35(1):35-37.

[6]杨坚.PD和脉压雷达相参干扰技术研究[J].电子对抗技术,1999,14(2):15-18.

[7]李斌,赵一诗,曹纯,等.超深亚微米工艺下预防串扰方法[J].无线电通信技术,2011,37(2):42-44.

[8]MIKAEL G,WIKNER J J,NIANXIONG N T.Cmos Data Converters for Communications[M].Kluwer Academic Publishers,2002.

[9]BEHZAD R.Design of Analog Cmos Integrated Circuits[M].The McGraw-Hill Companies,INC, 2001:384-385.

[10]GEERT A M,VAN D P,JAN V.etc.A 14 bit Intrinsic Accuracy Q2Random Walk CMOS DAC[J].IEEE Journal of Solid-state Circuits,1999,34(12):1 708-1 718.

魏恒男,(1984—),博士,工程师。主要研究方向:射频通信。

邹振杰男,(1986—),硕士,工程师。主要研究方向:模拟电路设计。

Study on Circuit of Current Source in Phase Digitizing DAC

WEI Heng,ZOU Zhen-jie

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

AbstractOwing to the continual enhancement of conversion accuracy and speed of phase digitizing DAC,higher performance current source is demanded.A circuit structure of current source is introduced,the merits and shortcomings are analyzed,and a method for layout design of reducing the process variation and device mismatch is adopted.The simulation is performed based on 90 nm CMOS process,and the results show that this structure has high output impedance and accuracy at 2 GHz clock rate.

Key wordsphase digitizing DAC;current source;output impedance

作者简介

收稿日期:2015-03-08

中图分类号TN432

文献标识码A

文章编号1003-3106(2015)06-0028-04

doi:10.3969/j.issn.1003-3106.2015.06.08

引用格式:魏恒,邹振杰.一种相位量化DAC中电流源电路研究[J].无线电工程,2015,45(6):28-31.